针对X86架构系统故障定位的检测板的制作方法

针对x86架构系统故障定位的检测板

技术领域

[0001]

本发明属于自动化控制领域,具体涉及一种针对x86架构系统故障定位的检测板。

背景技术:

[0002]

x86泛指一系列intel公司用于开发处理器的指令集构建,早期处理器以数字命名为80x86,之后的处理器只要采用该指令集,即称为x86处理器。x86处理器构建的硬件系统称为x86系统,而x86系统启动最前期需要对其cpu以及周围硬件进行初始化操作,该操作可以统称为一套小型系统即bios。

[0003]

bios(basic input/output system)即基本输入输出系统,亦称为rom bios、system bios、pc bios,是在通电引导阶段运行硬件初始化,以及为操作系统提供运行时服务的固件。bios是x86启动时加载的第一个软件。bios流程中通过lpc总线端口0x80进行调试码输出。

[0004]

lpc总线通常和主板上的南桥物理相连,南桥在ibm pc at平台上通常连接了一系列设备。lpc总线是intel在1998时作为工业标准架构体系(isa)的替代品引入,lpc总线是4bit宽,33.3mhz的总线。

[0005]

现在,bios的作用是初始化和测试硬件组件,以及从大容量存储设备(如硬盘)加载引导程序,并由引导程序加载操作系统。bios还为dos操作系统提供键盘、显示及其他i/o设备的硬件抽象层。

[0006]

当电脑的电源开启,bios就会从主板上的rom芯片运行,运行加电自检(post),测试和初始化cpu、ram、直接存储器访问控制器、芯片组、键盘、软盘、硬盘等设备。当所有的option rom被加载后,bios就试图从引导设备(如硬盘、软盘、光盘)加载引导程序,由引导程序加载操作系统。

[0007]

x86平台下,系统主板的bios启动失败会直接导致计算机主板无法正常运行,且没有任何故障调试手段,无论硬件故障还是bios故障都无从下手,且其他设计相关bios的故障板只是简单的通过指示灯或者数码管进行故障定位,而无法定位流程中的故障。

技术实现要素:

[0008]

本发明的目的在于克服现有技术中的缺陷,提供一种针对x86架构系统故障定位的检测板。

[0009]

为了实现上述目的,本发明的技术方案如下:

[0010]

一种针对x86架构系统故障定位的检测板,包括lpc总线接口单元、led数码管单元、串口逻辑单元和cpld逻辑控制单元,lpc总线接口单元、cpld逻辑控制单元、串口逻辑单元依次相连,led数码管单元与cpld逻辑控制单元相连。

[0011]

所述lpc总线接口单元,用于进行lpc总线采集和解析,按照lpc总线协议low pin count(lpc)interface specification,以时钟信号lclk为输入,按照帧同步信号lframe#解析并行数据lad[3:0]信号,即以33mbit时钟采集4bit并行数据并按lpc总线协议

解析为特定端口的8位实际数据。

[0012]

所述led数码管单元,即cpld控制逻辑输出8bit数据,数码管按照16进制hex显示输出相应的数字。

[0013]

所述串口逻辑单元,以82c52模块为基础(即串口寄存器逻辑符合82c52芯片逻辑)进行串口rs232电平信号输出,输出数据为每次采集的lpc总线8位数据。

[0014]

所述cpld逻辑控制单元,用于进行lpc总线解析并控制数码管和串口逻辑电路单元输出。

[0015]

本发明的优越性在于:bios启动中每个阶段完成都会控制南桥芯片对0x80端口输出特定的数据,即bios跑码,该数据传输在lpc总线上。本发明bios故障检测板可以采集lpc总线数据并将跑码显示在数码管上,另外特别说明,由于bios跑码速度远大于普通人眼识别数字速度,则通过故障码查看启动流程变为不可能,而通过串口模块打印故障码,即可将跑码数据记录在本地以便用于之后排故分析。

附图说明

[0016]

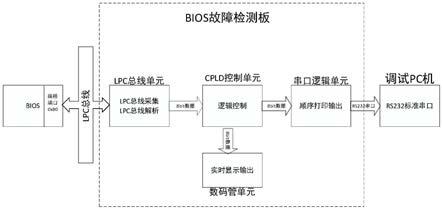

图1为本发明实施提供的一种针对x86架构系统故障定位的检测板的结构连接图。

具体实施方式

[0017]

以下通过附图和具体实施方式对本发明作进一步的详细说明。

[0018]

如图1所示,一种针对x86架构系统故障定位的检测板,包括lpc总线接口单元、led数码管单元、串口逻辑单元和cpld逻辑控制单元,lpc总线接口单元、cpld逻辑控制单元、串口逻辑单元依次相连,led数码管单元与cpld逻辑控制单元相连。

[0019]

所述lpc总线接口单元,用于进行lpc总线采集和解析,按照lpc总线协议low pin count(lpc)interface specification,以时钟信号lclk为输入,按照帧同步信号lframe#解析并行数据lad[3:0]信号,即以33mbit时钟采集4bit并行数据并按lpc总线协议解析为特定端口的8位实际数据。

[0020]

所述led数码管单元,用于根据cpld控制逻辑输出8bit数据,数码管按照16进制hex显示输出相应的数字。

[0021]

所述串口逻辑单元,以82c52模块为基础(即串口寄存器逻辑符合82c52芯片逻辑)进行串口rs232电平信号输出,输出数据为每次采集的lpc总线8位数据。

[0022]

所述cpld逻辑控制单元,用于进行lpc总线解析并控制数码管和串口逻辑电路单元输出。

[0023]

该发明工作流程:lpc总线单元实时检测总线数据并解析南桥端口0x80数据,cpld控制逻辑将该数据通过数码管的那样实时显示并通过串口逻辑控制单元输出rs232电平信息,该rs232串口信息通过连接pc机串口接收并存储。

[0024]

上述实施例仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1