一种片上系统仿真平台及其构建方法与流程

1.本发明涉及片上系统仿真技术领域,具体涉及一种片上系统仿真平台及其构建方法。

背景技术:

2.随着半导体行业的飞速发展,硅的尺寸、功能和软件的复杂性都达到了前所未有的水平。为了达到产品在预期时间上市的目标,需要在产品开发周期中引入并行性,在产品开发过程中进行仿真测试。

3.在现有的开发方式中,常见的仿真测试方式有搭建片上系统仿真环境和利用cpu总线功能模型(bus function model,bfm)进行片上系统仿真两种。但是,现有的片上系统仿真环境是通过真实的cpu执行c代码来进行仿真,这种仿真方式在cpu ip导入不及时的情况下,将无法进行片上系统验证平台的搭建和调试,也无法进行软件的前期开发。通过cpu总线功能模型bfm构建verilog或者system verilog激励进行片上系统的仿真,采用这种方式进行软件开发的c语言代码无法直接在片上系统仿真平台上运行,不利于软件代码开发以及片上系统应用场景的构建。

技术实现要素:

4.为了解决现有技术中的不足,本发明提出了一种片上系统仿真平台及其构建方法,该仿真平台及其构建方法能够通过dpi虚拟出一个cpu在芯片片上系统仿真环境中替代真实的cpu,不仅可以使软件开发人员尽快开始代码开发,还可以使硬件验证人员利用软件人员开发的代码为芯片构建更多的应用场景,从而达到更高效、更全面验证芯片的目的。

5.为实现上述目的,本发明采用了以下技术方案:

6.根据本发明的第一方面,提供了一种片上系统仿真平台,该仿真平台包括:总线模块、cpu总线功能模型单元和系统存储模块。

7.所述总线模块包括axi总线控制单元、axi-ahb转接桥、ahb总线控制单元、ahb-axi转接桥、apb总线控制单元、ahb-apb转接桥和axi-apb转接桥。

8.所述cpu总线功能模型单元通过axi接口或ahb接口与所述总线模块相连,且所述cpu总线功能模型单元设有dpi接口;所述dpi接口,用于将所述cpu总线功能模型单元中的任务开放给c语言接口。

9.所述系统存储模块包括静态随机存取存储器sram;所述系统存储模块与所述axi接口或所述ahb接口相连。

10.如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述cpu总线功能模型单元采用system verilog语言生成。

11.如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述axi总线控制单元、所述ahb总线控制单元和所述apb总线控制单元均包括主端口和从端口。

12.如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述cpu总线

功能模型单元,其采用write_bus和read_bus任务对所述总线模块进行操作,采用delay_cyc作为延时任务,采用main_thread作为入口任务。

13.如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述c语言接口通过调用write_bus、read_bus、delay_cyc和main_thread任务完成对总线模块的操作。

14.如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述总线模块连接有多个ip,采用main_thread任务访问与总线模块连接的设备的寄存器,或将系统存储模块初始化后供与总线模块连接的设备使用。

15.根据本发明的第二方面,提供了一种上述片上系统仿真平台的构建方法,该方法包括:

16.(1)构建总线模块。

17.(2)采用system verilog语言生成cpu总线功能模型单元,并通过axi接口或ahb接口将cpu总线功能模型单元与总线模块连接。

18.(3)采用静态随机存取存储器sram构建系统存储模块,并将系统存储模块与axi接口或ahb接口的slave相连。

19.(4)采用dpi接口将cpu总线功能模型单元与c语言接口连接,使cpu总线功能模型单元中的任务开放给c语言接口,c语言接口调用write_bus、read_bus、delay_cyc和main_thread任务完成对总线模块的操作。

20.如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,该方法还包括构建测试用例,例化总线模块、cpu总线功能模型单元和系统存储模块,并生成时钟和复位任务。

21.与现有技术相比,本发明具有以下有益效果:

22.本发明通过dpi虚拟出一个cpu在芯片的片上系统仿真环境中替代真实的cpu,这样不仅能够使软件人员可以尽快进行代码开发,还可以使硬件验证人员利用软件人员开发的代码为芯片构建更多的应用场景,达到更高效、更全面验证芯片的目的。

附图说明

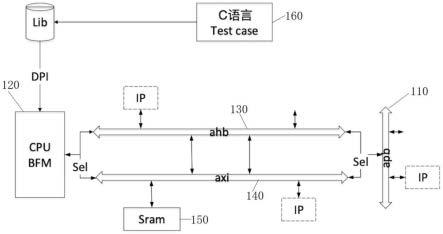

23.图1是本发明中片上系统仿真平台的原理图;

24.图2是本发明中片上系统仿真平台的结构框图;

25.图3是本发明中片上系统仿真平台构建方法的流程图。

26.其中:

27.110、总线模块,120、cpu总线功能模型单元,130、ahb接口,140、axi接口,150、系统存储模块,160、c语言接口。

具体实施方式

28.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的全部其他实施例,都属于本发明保护的范围。

29.另外,本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在

三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,一般表示前后关联对象是一种“或”的关系。

30.本发明通过dpi虚拟出一个cpu在芯片的片上系统仿真环境中替代真实的cpu,这样不仅能够使软件人员可以尽快进行代码开发,还可以使硬件验证人员利用软件人员开发的代码为芯片构建更多的应用场景,达到更高效、更全面验证芯片的目的。

31.图1示出了本发明中片上系统仿真平台的原理图,图2示出了片上系统仿真平台的结构框图。该仿真平台包括:总线模块110、cpu总线功能模型单元120和系统存储模块150。

32.所述总线模块110包括axi总线控制单元、axi-ahb转接桥、ahb总线控制单元、ahb-axi转接桥、apb总线控制单元、ahb-apb转接桥和axi-apb转接桥。所述总线模块110连接有多个ip,采用main_thread任务访问与总线模块连接的设备的寄存器,或将系统存储模块初始化后供与总线模块连接的设备使用。所述axi总线控制单元为4*4,包括4个主端口master port和4个从端口slave port。所述axi-ahb的转接桥为4*4,包括4个主端口master port和4个从端口slave port。所述apb总线控制单元包括4个从端口slave port。

33.所述cpu总线功能模型单元120通过axi接口140或ahb接口130与所述总线模块110相连,且所述cpu总线功能模型单元120设有dpi接口。通过dpi接口把cpu的bfm中的task开放给c语言接口160,c语言可以直接调用main_thread并在内部调用write_bus和read_bus完成对总线的操作,调用delay完成延时任务。

34.所述cpu总线功能模型单元120为虚拟的cpu,其采用write_bus和read_bus任务对所述总线模块110进行操作,采用delay_cyc作为延时任务,采用main_thread作为入口任务。所述c语言接口通过调用write_bus、read_bus、delay_cyc和main_thread任务完成对总线模块的操作。

35.所述系统存储模块160包括静态随机存取存储器sram;所述系统存储模块160与所述axi接口140或所述ahb接口130相连。

36.本发明通过dpi虚拟出一个cpu在芯片片上系统仿真环境中替代真实的cpu,这样软件人员既可以尽快开始代码开发,硬件验证人员也能利用软件人员开发的代码为芯片构建更多的应用场景,达到更高效,更全面验证芯片的目的。

37.本发明的目的一方面在芯片开发过程中引入更多的并行性,包括片上系统仿真与设计集成的并行性,软件开发与片上系统仿真验证的并行性等。另一方面可以结合软件应用,在片上系统仿真阶段增加更多系统级的行为,既方便软件开发遇到问题时通过片上系统仿真调试,有便于硬件覆盖更多应用场景。

38.图3示出了片上系统仿真平台构建方法300的流程图。

39.在框310,构建总线模块。总线模块的master port和slave port可以连接不同的ip,在任务main_thread中可以完成对连接ip的寄存器访问,也可以初始化静态随机存取存储器sram内容给连接的ip使用。

40.在框320,采用system verilog语言生成cpu总线功能模型单元,并通过axi接口或ahb接口将cpu总线功能模型单元与总线模块连接。所述cpu总线功能模型单元通过system verilog创建一个cpu的bfm,有一套axi或者ahb的总线接口与总线系统相连,把对总线模块的操作抽象成write_bus和read_bus两个task,另外增加一个delay_cyc作为延时task,增加一个cpu的入口任务main_thread,构建c语言需要的其他任务。

41.在框330,采用静态随机存取存储器sram构建系统存储模块,并将系统存储模块与axi接口或ahb接口的slave相连。

42.在框340,采用dpi接口将cpu总线功能模型单元与c语言接口连接,使cpu总线功能模型单元中的任务开放给c语言接口,c语言接口调用write_bus、read_bus、delay_cyc和main_thread任务完成对总线模块的操作。

43.在框350,构建测试用例,例化总线模块、cpu总线功能模型单元和系统存储模块,并生成时钟和复位任务。硬件验证人员和软件开发人员可以同时进行c语言测试用例的构建。

44.本发明仿真环境简单,不需要把c语言编译成hex的一系列过程和相关交叉编译环境,只需要把c语言编译成相关共享库就可以。软件开发和硬件验证人员可以在还没有真正cpu的时候进行现有ip的仿真和软件代码的开发,尽早开展工作有利于缩短整个芯片开发周期。本发明可以更好地复现问题,当cpu的bfm中的task足够丰富能够覆盖软件开发的所有情况时,软硬件可以同时在一个平台上开发用例,软件出现用例问题时,可以更方便地在硬件仿真平台复现。此外硬件验证人员可以更好的借助丰富的软件库,实现更多系统级应用场景的覆盖,尽早发现并解决系统可能隐藏的问题。

45.以上所述实施例仅仅是对本发明的优选实施方式进行描述,并非对本发明的范围进行限定,在不脱离本发明设计精神的前提下,本领域普通技术人员对本发明的技术方案做出的各种变形和改进,均应落入本发明权利要求书确定的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1