调试方法、装置及存储介质与流程

本发明涉及计算机,尤其涉及调试方法、装置及存储介质。

背景技术:

1、在芯片开发调试过程中,经常需要获取芯片内部的排错(debug)信号进行辅助分析,协助进行芯片调试。

2、目前,一种常见的获取排错信号的方式主要通过串口打印关键的信息,然而该种方式不能打印硬件模块的内部排错信号;另一种常见的获取排错信号的方式主要将硬件模块的内部排错信号直接通过输入输出(input/output,io)资源放出,用逻辑分析仪抓取信号分析,从而帮助分析硬件的工作状态,然而该种方式经常需要占用多个io资源,开销较大等。

3、综上,如何高效获取排错信号,减少io资源占用,是需要解决的技术问题。

技术实现思路

1、本发明实施例提供一种调试方法、装置及存储介质,用以解决io资源紧张的芯片排错难题。

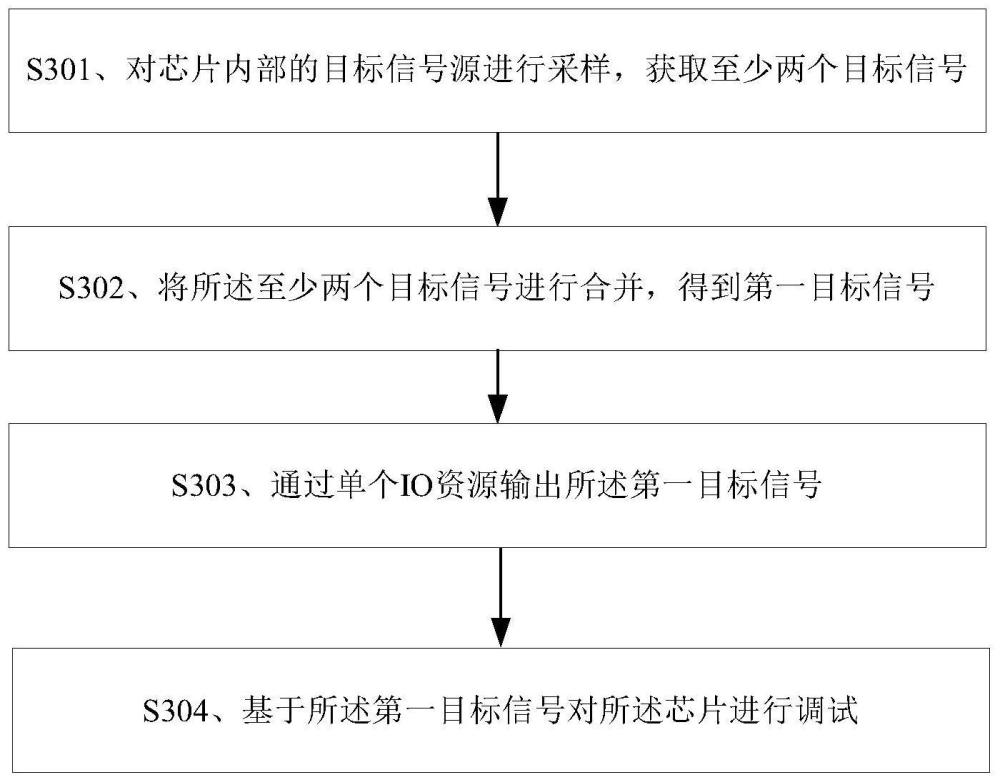

2、第一方面,本发明实施例提供一种调试方法,包括:

3、对芯片内部的目标信号源进行采样,获取至少两个目标信号;

4、将所述至少两个目标信号进行合并,得到第一目标信号;

5、通过单个输入输出io资源输出所述第一目标信号;

6、基于所述第一目标信号对所述芯片进行调试。

7、在一种可能的设计中,所述目标信号包括所述芯片内部的排错信号。

8、在一种可能的设计中,对芯片内部的目标信号源进行采样,获取至少两个目标信号,包括:

9、确定采样时钟;

10、通过所述采样时钟对所述芯片内部的目标信号源进行采样,获取至少两个目标信号;

11、将所述至少两个目标信号存储到对应的寄存器中。

12、在一种可能的设计中,所述方法还包括:

13、每个采样时钟周期,更新所述寄存器中存储的目标信号。

14、在一种可能的设计中,将所述至少两个目标信号进行合并,得到第一目标信号,包括:

15、将所述寄存器中存储的多位并行目标信号转换成一位串行目标信号,得到所述第一目标信号。

16、在一种可能的设计中,通过单个输入输出io资源输出所述第一目标信号,包括:

17、确定应用的传输协议;

18、基于所述传输协议通过单个io资源输出所述第一目标信号。

19、在一种可能的设计中,所述方法还包括:

20、抓取并保存输出的所述第一目标信号。

21、在一种可能的设计中,基于所述第一目标信号对所述芯片进行调试,包括:

22、将所述第一目标信号恢复为所述至少两个目标信号并显示;

23、基于所述至少两个目标信号对所述芯片进行调试。

24、第二方面,本发明实施例提供一种调试装置,包括:

25、处理模块,用于对芯片内部的目标信号源进行采样,获取至少两个目标信号;将所述至少两个目标信号进行合并,得到第一目标信号;

26、输出模块,用于通过单个io资源输出所述第一目标信号:

27、调试模块,用于基于所述第一目标信号对所述芯片进行调试。

28、在一种可能的设计中,所述目标信号包括所述芯片内部的排错信号。

29、在一种可能的设计中,所述处理模块具体用于:

30、确定采样时钟;

31、通过所述采样时钟对所述芯片内部的目标信号源进行采样,获取至少两个目标信号;

32、将所述至少两个目标信号存储到对应的寄存器中。

33、在一种可能的设计中,所述处理模块还用于:

34、每个采样时钟周期,更新所述寄存器中存储的目标信号。

35、在一种可能的设计中,所述处理模块具体用于:

36、将所述寄存器中存储的多位并行目标信号转换成一位串行目标信号,得到所述第一目标信号。

37、在一种可能的设计中,所述输出模块具体用于:

38、确定应用的传输协议;

39、基于所述传输协议通过单个io资源输出所述第一目标信号。

40、在一种可能的设计中,所述调试模块还用于:

41、抓取并保存输出的所述第一目标信号。

42、在一种可能的设计中,所述调试模块具体用于:

43、将所述第一目标信号恢复为所述至少两个目标信号并显示;

44、基于所述至少两个目标信号对所述芯片进行调试。

45、第三方面,本申请实施例提供了一种调试装置,包括至少一个处理器和接口电路,所述接口电路用于为所述至少一个处理器提供数据或者代码指令,所述至少一个处理器用于通过逻辑电路或执行代码指令实现如上述第一方面以及第一方面任一可能设计所述的方法。

46、第四方面,本申请实施例提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,当所述计算机程序被运行时,执行如上述第一方面以及第一方面任一可能设计所述的方法。

47、第五方面,本申请实施例提供了一种芯片系统,该芯片系统包括处理器,用于调用存储器中存储的计算机程序或计算机指令,以使得该处理器执行上述第一方面以及第一方面任一可能设计所述的方法。

48、结合第五方面,在一种可能的实现方式中,该处理器可以通过接口与存储器耦合。

49、结合第五方面,在一种可能的实现方式中,该芯片系统还可以直接包括存储器,该存储器中存储有计算机程序或计算机指令。

50、第六方面,本申请实施例提供了一种计算机程序产品,当所述计算机程序产品在计算机上运行时,使得所述计算机执行上述第一方面以及第一方面任一可能设计所述的方法。

51、综上,本发明实施例中,通过用单个io资源将芯片内部多个目标信号,例如排错信号同时放出,不仅能够使接收端一次性接收到多个目标信号,提高了信号接收效率,还提高了单个io资源的承载输出效率,减少了io资源的占用率,有效解决了io资源紧张导致的芯片排错难题。此外,io状态一般可以在芯片外用逻辑分析仪抓取,但会受限于外围连接关系,给信号抓取带来困难,而本申请实施例通过单个io资源将芯片内部多个目标信号同时放出,能够实现芯片内部的多信号抓取,更加方便快速,抓取成功率更高。

技术特征:

1.一种调试方法,其特征在于,包括:

2.如权利要求1所述的方法,其特征在于,所述目标信号包括所述芯片内部的排错信号。

3.如权利要求2所述的方法,其特征在于,对芯片内部的目标信号源进行采样,获取至少两个目标信号,包括:

4.如权利要求3所述的方法,其特征在于,所述方法还包括:

5.如权利要求3或4所述的方法,其特征在于,将所述至少两个目标信号进行合并,得到第一目标信号,包括:

6.如权利要求1~4中任一项所述的方法,其特征在于,通过单个输入输出io资源输出所述第一目标信号,包括:

7.如权利要求6所述的方法,其特征在于,所述方法还包括:

8.如权利要求1~4、7中任一项所述的方法,其特征在于,基于所述第一目标信号对所述芯片进行调试,包括:

9.一种调试装置,其特征在于,包括:

10.一种调试装置,其特征在于,包括存储器,以及一个或多个处理器,所述存储器与所述一个或多个处理器耦合;

11.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质用于存储计算机程序,当所述计算机程序在电子设备上运行时,使得所述电子设备实现如权利要求1至8中任一项所述的方法。

技术总结

本发明涉及计算机技术领域,尤其涉及调试方法、装置及存储介质,以解决IO资源紧张的芯片排错难题。本发明实施例提供的调试方法包括,对芯片内部的目标信号源进行采样,获取至少两个目标信号;将所述至少两个目标信号进行合并,得到第一目标信号;通过单个IO资源输出所述第一目标信号;基于所述第一目标信号对所述芯片进行调试。通过该方法,用单个IO资源将芯片内部多个目标信号同时放出,有效解决了IO资源紧张的芯片排错难题。

技术研发人员:彭国杰,魏华铭

受保护的技术使用者:炬芯科技股份有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!