一种用于公钥密码算法加速的协处理器的制作方法

1.本发明属于数字逻辑电路技术领域,更具体地,涉及一种用于公钥密码算法加速的协处理器。

背景技术:

2.公钥密码算法具有信息的加密、解密、数字签名和签名验证等功能,且具备公钥和私钥两套不同的密钥,使其在安全性上强于对称密码算法。随着信息安全风险的不断上升,密钥的长度也在不断加长,随之而来的是公钥算法的计算量在快速变大。使用编程手段来实现公钥密码算法不仅容易遭受外来攻击,而且计算效率低下,因此,使用专门的计算单元加速特定算法成为了主流优化思想。

3.当前主流的公钥密码算法主要包括rsa、ecc以及sm2这三种算法。目前,业界普遍要求兼容2048、3072甚至4096位长度的rsa,ecc和sm2则涉及到椭圆曲线域的兼容性。当前ecc广泛使用的有限域是素数域和二元域,sm2基于ecc之上,要求必须同时兼容这两种域中的椭圆曲线问题计算,同时规定密钥长度为256/257位。国内外在公钥算法加速器设计上的成果众多,但是在兼容性的取舍、密钥长度的限定和算法的硬件实现上都不尽相同。

4.传统公钥密码加速器存在以下不足点:能加速的公钥密码算法通常是单一的,在当前多种公钥密码算法混合使用的场合,其很难发挥出最大的加速效果;支持的rsa密钥长度短,不符合目前的安全性需求;对ecc/sm2算法的运算域支持不完备,只支持素数域和二元扩域其中一个运算域;支持的ecc/sm2算法的椭圆曲线长度较短,难以满足当下以及未来的需求。

技术实现要素:

5.针对现有技术的缺陷和改进需求,本发明提供了一种用于公钥密码算法加速的协处理器,其目的在于解决传统加速器支持的算法单一、支持的密钥长度低和运算域不齐全的问题。

6.为实现上述目的,本发明提供了一种用于公钥密码算法加速的协处理器,包括:底层算法单元,包括模加减电路、q值计算电路和蒙哥马利模乘电路;中层算法单元,包括点的加法电路、点的倍乘电路和模幂电路,可调用所述底层算法单元;顶层算法单元,包括模逆电路和点的标量乘电路,可调用所述中层算法单元和所述底层算法单元;逻辑控制单元,用于根据操作命令控制所述底层算法单元、所述中层算法单元和所述顶层算法单元,以实现4096位及以下任意长度的rsa算法中模幂操作、sm2算法中椭圆曲线的多倍点操作以及ecc算法中椭圆曲线的多倍点操作。

7.更进一步地,第一乘数a、第二乘数b和模数n分别按照32位一组分为w+1个元素后输入所述蒙哥马利模乘电路,所述蒙哥马利模乘电路用于:s1,计算第一参数t:t=(ai×

b0+s0)&(0xffff_ffff),i的初始值为0,ai为所述第一乘数a分组后的第i+1个元素,b0为所述第二乘数b分组后的第1个元素,s0为当前模乘结果s的第1个元素;s2,计算第二参数u:u=(q

×

t)&(0xffff_ffff),q为预计算参数;s3,计算第三参数z:z=s0+d+ai×

b0+u

×

n0,d为初始值为0的第四参数,n0为所述模数n分组后的第1个元素;s4,更新第四参数d:d=z>>32;s5,更新第三参数z:z=sj+d+ai×bj

+u

×

nj,j的初始值为1,sj为当前模乘结果s的第j+1个元素,bj为所述第二乘数b分组后的第j+1个元素,nj为所述模数n分组后的第j+1个元素;s6,更新s

j-1

和第四参数d:s

j-1

=z&(0xffff_ffff),d=z>>32;s7,对j进行加一处理,重复执行所述s5-s6,直至j=w+1;s8,对i进行加一处理,重复执行所述s1-s7,直至i=w。

8.更进一步地,所述蒙哥马利模乘电路包括计算单元,所述计算单元包括:第一wallace树形双域流水线乘法器,用于计算ai×

b0、q

×

t和ai×bj

;第二wallace树形双域流水线乘法器,用于计算u

×

n0和u

×

nj;第一双域加法器,用于根据ai×

b0的计算结果计算所述s1中的第一参数t;第二双域加法器,用于计算s0+d和sj+d;第三双域加法器,用于将ai×

b0的计算结果与u

×

n0的计算结果相加,以及将ai×bj

的计算结果与u

×

nj的计算结果相加;第四双域加法器,用于将s0+d的计算结果与所述第三双域加法器输出的ai×

b0+u

×

n0的计算结果相加以计算所述s3中第三参数z,以及将sj+d的计算结果与所述第三双域加法器输出的ai×bj

+u

×

nj的计算结果相加以更新所述s5中第三参数z,并执行所述s4和s6中更新第四参数d的操作。

9.更进一步地,所述计算单元的数量为一个或多个,当所述计算单元的数量为多个时,多个所述计算单元按照顺序依次执行一轮所述s1-s7。

10.更进一步地,所述第一wallace树形双域流水线乘法器和所述第二wallace树形双域流水线乘法器为32比特宽度的三级流水线乘法器;所述第一双域加法器、所述第二双域加法器、所述第三双域加法器和所述第四双域加法器为64比特宽度的双域行波加法器。

11.更进一步地,所述q值计算电路用于计算预计算参数q,预计算参数q满足:

[0012][0013]

其中,n0为模数n的最低32比特。

[0014]

更进一步地,所述模加减电路可被所述点的加法电路和所述点的倍乘电路调用;所述q值计算电路可被所述操作命令调用;所述蒙哥马利模乘电路可被所述操作命令、所述点的加法电路、所述点的倍乘电路和所述模幂电路调用;所述点的加法电路和所述点的倍乘电路可被点的标量乘电路调用;所述模幂电路可被所述操作命令和所述模逆电路调用;所述模逆电路被所述操作命令和所述点的标量乘电路调用;所述点的标量乘电路被所述操作命令调用。

[0015]

更进一步地,素数域中,所述点的加法电路和所述点的倍乘电路在雅可比-仿射混合坐标系中分别进行点的加法运算和点的倍乘运算;二元扩域中,所述点的加法电路和所述点的倍乘电路在洛佩兹达哈卜-仿射混合坐标系中分别进行点的加法运算和点的倍乘运算。

[0016]

更进一步地,所述模逆电路采用费马小定理算法实现双域模逆运算,最大模数比特宽度为4096位。

[0017]

总体而言,通过本发明所构思的以上技术方案,能够取得以下有益效果:

[0018]

(1)通过对rsa、ecc和sm2算法的分析,将所有需要硬件实现的数学算法划分为底层算法、中层算法和顶层算法,并将所有算法单元整合成协处理器,其支持4096位及以下的rsa模幂运算、sm2所需的256/257位双域椭圆曲线点乘计算、ecc不高于384位的双域椭圆曲

线点乘计算以及双域模乘、模逆运算,兼容性好;

[0019]

(2)资源消耗可定制,通过改变蒙哥马利模乘电路中并行计算单元的数量,可以在电路的计算速度、面积、功耗之间做平衡,满足多种不同场合的需求。

附图说明

[0020]

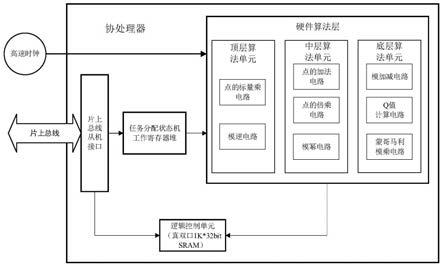

图1为本发明实施例提供的用于公钥密码算法加速的协处理器的架构示意图;

[0021]

图2为本发明实施例提供的蒙哥马利模乘电路的结构示意图;

[0022]

图3为本发明实施例提供的计算单元的一轮执行过程的示意图;

[0023]

图4为本发明实施例提供的计算单元的结构示意图;

[0024]

图5为本发明实施例提供的蒙哥马利模乘电路的数据流示意图;

[0025]

图6为本发明实施例提供的协处理器应用场景示意图;

[0026]

图7为本发明实施例提供的测试256位素数域椭圆曲线点乘的结果;

[0027]

图8为本发明实施例提供的测试257位二元扩域椭圆曲线点乘的结果;

[0028]

图9为本发明实施例提供的计算4096位rsa私钥运算的结果;

[0029]

图10为本发明实施例提供的计算素数域和二元扩域模逆运算的结果。

具体实施方式

[0030]

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

[0031]

在本发明中,本发明及附图中的术语“第一”、“第二”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

[0032]

图1为本发明实施例提供的用于公钥密码算法加速的协处理器的架构示意图。参阅图1,结合图2-图10,对本实施例中用于公钥密码算法加速的协处理器进行详细说明。

[0033]

参阅图1,用于公钥密码算法加速的协处理器包括:底层算法单元、中层算法单元、顶层算法单元、和逻辑控制单元。

[0034]

底层算法单元包括模加减电路、q值计算电路和蒙哥马利模乘电路。中层算法单元包括点的加法电路、点的倍乘电路和模幂电路,可调用底层算法单元。顶层算法单元包括模逆电路和点的标量乘电路,可调用中层算法单元和底层算法单元。

[0035]

逻辑控制单元根据操作命令控制底层算法单元、中层算法单元和顶层算法单元,以实现4096位及以下任意长度的rsa算法中模幂操作、sm2算法中椭圆曲线的多倍点操作以及ecc算法中椭圆曲线的多倍点操作。

[0036]

进一步地,根据本发明的实施例,模加减电路可被点的加法电路和点的倍乘电路调用;q值计算电路可被操作命令调用;蒙哥马利模乘电路可被操作命令、点的加法电路、点的倍乘电路和模幂电路调用;点的加法电路和点的倍乘电路可被点的标量乘电路调用;模幂电路可被操作命令和模逆电路调用;模逆电路被操作命令和点的标量乘电路调用;点的标量乘电路被操作命令调用。

[0037]

用于公钥密码算法加速的协处理器(以下简称为协处理器)可以对rsa公钥密码算

法的加密、解密等操作进行加速。rsa公钥密码算法的加密和解密原理如下:

[0038]

(1)密钥的生成

[0039]

(1.1)随机选取两个不同的大素数p和q,计算模数n=p

×

q。由欧拉函数可知,与n互素且不大于n的整数个数为个。

[0040]

(1.2)选取一个公钥ke,满足且与互素。通常,为了减少大多数终端设备加密和验签的计算量,公钥会选择比较短小的比特串,如3、17、65537等。

[0041]

(1.3)计算满足(kd×

ke)的kd,将其作为私钥。公开公钥{n,ke},保密私钥{n,kd}。

[0042]

(2)加密方法

[0043]

对于明文比特串p,其满足条件p《n,且p的比特宽度小于n的比特宽度,则有:

[0044][0045]

(3)解密方法

[0046]

对于密文比特串,将其进行分割处理后,某组密文为c,则其解密过程为:

[0047][0048]

协处理器能计算上述算法中的和操作,且支持的模数n的最大比特宽度为4096位,从而达到加速rsa算法计算的目的。

[0049]

协处理器能对ecc公钥密码算法的加密和解密操作进行加速,典型的素数域ecc公钥密码算法的加解密原理如下:

[0050]

(1)密钥的生成

[0051]

(1.1)选择一个素数域gf(p)和一条定义在素数域上的椭圆曲线e

p

(a,b):y2=x3+ax+b。随机取一个点g为基点,要求基点g的阶n尽量大(接近素数p)。选择的椭圆曲线,基点g和它的阶n为公钥参数的部分。

[0052]

(1.2)随机生成一大数k,要求k大于1且小于n,计算点的标量乘p=kg。随机数k为私钥,p=kg为公钥部分。

[0053]

(2)加密方法

[0054]

对于明文序列(m1,m2),随机生成一大数w,要求w大于等于1且小于n,计算点的标量乘wp=(x,y)。如果x、y中有一个为0,则需要重新选取w。wp计算完成后,利用素数域运算法则计算:

[0055]

c0=wg,c1=m1·

x,c2=m2·y[0056]

由此,得到密文序列(c0,c1,c2)。

[0057]

(3)解密方法

[0058]

得到密文序列(c0,c1,c2)后,基于以下方式计算明文序列:

[0059]

(x,y)=kc0,m1=c1·

x-1

,m2=c2·

y-1

[0060]

协处理器能计算上述算法中的c0=wg和(x,y)=kc0涉及的点乘运算;求x-1

、y-1

的模逆运算;以及计算c1、c2、m1、m2的模乘运算,且最高支持384位素数域和二元扩域椭圆曲线。

[0061]

协处理器能对sm2公钥密码算法的加密和解密操作进行加速,其加解密原理如下:

[0062]

(1)密钥的生成

[0063]

(1.1)从素数域gf(p)和二元域gf(2m)中选择一个运算域,之后根据运算域选择一条定义在其上的椭圆曲线e(a,b),依照国密标准,素数p通常选择256位大素数,二元域多项式通常选择gf(2

257

),并据此选择三项式x

257

+x

12

+1。

[0064]

(1.2)选取基点g,要求g的阶n接近#gf(p)或#gf(2m)。随机生成一大数db∈[2,n-1]作为私钥,计算公钥pb=dbg=(xb,yb)。将公钥pb和椭圆曲线参数、基点g、阶n,以及余因子或公开。

[0065]

(2)加密方法

[0066]

假设有一长度为klen的明文串m需要加密,其具体加密过程为:随机生成一数k∈[1,n-1],计算c1=(x1,y1)=kg;计算s=(xs,ys)=hpb,如果s是无穷远点,则报错并结束;计算p=(x2,y2)=kpb;调用sm3实现的kdf函数,计算t=kdf

klen

(x2,y2),若t=0,则返回最初步骤重新选择随机数;计算c2=m

⊕

t;计算c3=hash(x2,m,y2);得到密文c=(c1,c2,c3)。

[0067]

(3)解密方法

[0068]

假设有一密文c=(c1,c2,c3),且已知klen为c2的长度,具体解密过程为:验证c1=(x1,y1)是否为给定椭圆曲线上的点,若否,则报错并结束;计算s=hc1,若s是无穷远点,则报错并结束;计算p=(x2,y2)=dbc1,调用kdf函数执行t=kdf

klen

(x2,y2),若t=0,则报错并结束;计算m=c2⊕

t和u=hash(x2,m,y2),若u=c3,则m为所求明文,否则报错并退出。

[0069]

协处理器能计算上述算法中的素数域256位椭圆曲线的点乘操作和二元扩域257位椭圆曲线的点乘操作。

[0070]

本实施例中,通过对rsa、ecc和sm2算法的分析,将所有需要硬件实现的数学算法划分为底层算法、中层算法和顶层算法,并将所有算法单元整合成协处理器,其支持4096位及以下的rsa模幂运算、sm2所需的256/257位双域椭圆曲线点乘计算、ecc不高于384位的双域椭圆曲线点乘计算以及双域模乘、模逆运算。

[0071]

本实施例中,第一乘数a、第二乘数b和模数n分别按照32位一组分为w+1个元素后输入蒙哥马利模乘电路,输入蒙哥马利模乘电路的第一乘数a、第二乘数b和模数n为:

[0072]

a={aw,a

w-1

,a

w-2

,a

w-3

,...,a1,a0},aw=0

[0073]

b={bw,b

w-1

,b

w-2

,b

w-3

,...,b1,b0},bw=0

[0074]

n={nw,n

w-1

,n

w-2

,n

w-3

,...,n1,n0},nw=0

[0075]

蒙哥马利模乘电路的输入还包括:预计算参数q、r=2

32w

。其中,,k为模数比特宽度。蒙哥马利模乘电路的输出为:

[0076]

s=montmul(a,b,r,n)=(abr-1

)mod n=(sw,s

w-1

,...,s1,s0),sw=0

[0077]

根据本发明的实施例,蒙哥马利模乘电路用于执行操作s1-操作s8,如图3所示。其中,第一参数t、第二参数u、s的初始值均为0。

[0078]

操作s1,计算第一参数t:

[0079]

t=(ai×

b0+s0)&(0xffff_ffff)

[0080]

其中,i的初始值为0,ai为第一乘数a分组后的第i+1个元素,b0为第二乘数b分组后的第1个元素,s0为当前模乘结果s的第1个元素。

[0081]

操作s2,计算第二参数u:

[0082]

u=(q

×

t)&(0xffff_ffff)

[0083]

其中,q为预计算参数

[0084]

操作s3,计算第三参数z:

[0085]

z=s0+d+ai×

b0+u

×

n0[0086]

其中,d为初始值为0的第四参数,n0为模数n分组后的第1个元素。

[0087]

操作s4,更新第四参数d:

[0088]

d=z>>32

[0089]

操作s5,更新第三参数z:

[0090]

z=sj+d+ai×bj

+u

×

nj[0091]

其中,j的初始值为1,sj为当前模乘结果s的第j+1个元素,bj为第二乘数b分组后的第j+1个元素,nj为模数n分组后的第j+1个元素。

[0092]

操作s6,更新s

j-1

和第四参数d:

[0093]sj-1

=z&(0xffff_ffff)

[0094]

d=z>>32

[0095]

操作s7,对j进行加一处理,重复执行操作s5-操作s6,直至j=w+1。

[0096]

操作s8,对i进行加一处理,重复执行操作s1-操作s7,直至i=w。

[0097]

根据本发明的实施例,蒙哥马利模乘电路包括计算单元(calculation unit,cu)。参阅图4,计算单元包括:第一wallace树形双域流水线乘法器、第二wallace树形双域流水线乘法器、第一双域加法器、第二双域加法器、第二双域加法器和第四双域加法器。计算单元还包括计算参数寄存器、操作数延时寄存器堆、计算结果延时寄存器堆和控制状态机等。

[0098]

第一wallace树形双域流水线乘法器的输入端连接内部计算参数寄存器和/或计算单元取到的操作数,输出端连接第一双域加法器和第三双域加法器的输入端以及内部计算参数寄存器。第一双域加法器的输入端和输出端还均连接到内部计算参数寄存器。

[0099]

第二wallace树形双域流水线乘法器的输入端连接内部计算参数寄存器和计算单元取到的操作数,输出端连接第三双域加法器的输入端。第三双域加法器的输出端连接到第四双域加法器的输入端。

[0100]

第二双域加法器的输入端连接到内部计算参数寄存器,输出端连接到第四双域加法器的输入端。第四双域加法器的输出端连接到计算结果延时寄存器堆。

[0101]

计算参数寄存器包含了存储中间参数ai、q、n0、b0、t、bj、u、nj、z、d、s0的寄存器;操作数延时寄存器堆用于将操作数bj和nj进行延时后送给下一级计算单元;计算结果延时寄存器堆用于将计算单元的计算结果s

j-1

进行延时后送给下一级计算单元或同步fifo;控制状态机用于控制计算单元的执行过程,包括乘法器的输入选择和使能,寄存器数据的刷新和相关控制信号的发出等。

[0102]

第一wallace树形双域流水线乘法器用于计算ai×

b0、q

×

t和ai×bj

。第二wallace树形双域流水线乘法器用于计算u

×

n0和u

×

nj。

[0103]

第一双域加法器用于根据ai×

b0的计算结果计算操作s1中的第一参数t。第二双域加法器用于计算s0+d和sj+d。第三双域加法器用于将ai×

b0的计算结果与u

×

n0的计算结果相加,以及将ai×bj

的计算结果与u

×

nj的计算结果相加。

[0104]

第四双域加法器,用于将s0+d的计算结果与第三双域加法器输出的ai×

b0+u

×

n0的计算结果相加以计算操作s3中第三参数z,以及将sj+d的计算结果与第三双域加法器输

出的ai×bj

+u

×

nj的计算结果相加以更新操作s5中第三参数z,并执行操作s4和操作s6中更新第四参数d的操作。

[0105]

根据本发明的实施例,第一wallace树形双域流水线乘法器和第二wallace树形双域流水线乘法器为32比特宽度的三级流水线乘法器;第一双域加法器、第二双域加法器、第三双域加法器和第四双域加法器为64比特宽度的双域行波加法器。

[0106]

参阅图2,蒙哥马利模乘电路还包括cu主控电路和fifo。cu主控电路用于从sram中取得需要的操作数,并送给计算单元。fifo为同步fifo,用于暂存一次计算过程中最终的迭代结果s。每个计算单元的功能为执行一次32位字的高基蒙哥马利算法的外部循环;cu主控电路的功能为控制整个模乘计算的过程,包括取操作数、送操作数、判断计算结束等。

[0107]

根据本发明的实施例,计算单元的数量为一个或多个。当计算单元的数量为多个时,多个计算单元按照顺序依次执行一轮操作s1-操作s7。以图5中示出的蒙哥马利模乘电路中计算单元的数量为5个为例,cu主控电路从sram中取得ai、a

i+1

、a

i+2

、a

i+3

、a

i+4

,分别送到这5个计算单元,再根据计算单元的执行过程从sram中取操作数b和n送入第一个计算单元中。每个计算单元使用完操作数b和n后,会将操作数进行延时处理,连同当前计算单元计算的结果s一起送给下一级计算单元,作为计算的操作数。图中计算单元cu5计算的结果s需要暂存进同步fifo,待下一次循环发起时使用。

[0108]

通过利用多个(如5个)计算单元构成模乘电路,使得计算单元主控仅需取b和n一次,即可完成上述算法中操作2的多轮(如5轮)for循环,大大减少了模乘运算消耗的时间。

[0109]

根据本发明的实施例,q值计算电路用于计算预计算参数q,预计算参数q满足:

[0110][0111]

其中,n0为模数n的最低32比特。

[0112]

根据本发明的实施例,素数域中,点的加法电路和点的倍乘电路在雅可比-仿射混合坐标系中分别进行点的加法运算和点的倍乘运算;二元扩域中,点的加法电路和点的倍乘电路在洛佩兹达哈卜-仿射混合坐标系中分别进行点的加法运算和点的倍乘运算。

[0113]

根据本发明的实施例,模逆电路采用费马小定理算法实现双域模逆运算,最大模数比特宽度为4096位。

[0114]

本实施例中,蒙哥马利模乘电路用于计算素数域和二元扩域的大数模乘;模加减电路用于计算素数域和二元扩域的大数模加减,并且能够在不求补码的条件下完成有限域中的加减法运算;点的加法电路用于计算素数域和二元扩域椭圆曲线上的两点的相加;点的倍乘电路用于计算素数域和二元扩域椭圆曲线上的某点的双倍点;模幂电路用于计算素数域和二元扩域的大数的模幂,优选使用r-l扫描快速幂算法实现;点的标量乘电路用于计算素数域和二元扩域椭圆曲线点的多倍点问题,优选使用l-r扫描法调用点的加法和点的倍乘算法实现;模逆电路用于计算素数域和二元扩域中的元素的逆元素。

[0115]

参阅图1,本实施例中,协处理器还包括片上总线从机接口。片上总线从机接口用于输入操作数、计算参数和操作命令,输出计算结果和标志信号。协处理器和处理器通过片上总线从机接口进行数据传输。处理器向协处理器写入计算参数后,再向协处理器对应工作寄存器写指令,使能计算,在计算完成后,从协处理器中预设的存储区域取回计算结果。

[0116]

参阅图6,示出了协处理器的应用场景,pc机通过jtag连接到fpga开发板,烧录fpga电路固件和处理器执行的程序;处理器的片上总线接口先连接到总线互联器的从接口

上,配置总线上的主从设备均为一个,总线互联器上的主接口连接到外围总线转换器上,进而连接到协处理器的片上总线从接口,协处理器的高速时钟由片上总线时钟经锁相环倍频得到。协处理器内部的sram和fifo使用fpga上的资源实现。

[0117]

本实施例中,令处理器执行一段包含了测试的输入参数和对应的调用协处理器的驱动函数,处理器通过执行测试程序,将相应数据通过片上总线送入协处理器中运算,运算完毕后取出放在自身的内存空间中,并按顺序打印到串口上,上位机通过监听串口上的数据得到最终的计算结果,和标准用例进行比对。素数域256位椭圆曲线点乘的测试用例如表1所示。协处理器计算素数域256位椭圆曲线点乘的测试结果如图7所示。

[0118]

表1

[0119]

参数值模数p0x8542d69e4c044f18e8b92435bf6ff7de457283915c45517d722edb8b08f1dfc3椭圆系数a0x787968b4fa32c3fd2417842e73bbfeff2f3c848b6831d7e0ec65228b3937e498乘数k0x4c62eefd6ecfc2b95b92fd6c3d9575148afa17425546d49018e5388d49dd7b4f基点坐标xg0x435b39cca8f3b508c1488afc67be491a0f7ba07e581a0e4849a5cf70628a7e0a基点坐标yg0x75ddba78f15feecb4c7895e2c1cdf5fe01debb2cdbadf45399ccf77bba076a42结果坐标xr0x64d20d27d0632957f8028c1e024f6b02edf23102a566c932ae8bd613a8e865fe结果坐标yr0x58d225eca784ae300a81a2d48281a828e1cedf11c4219099840265375077bf78

[0120]

二元扩域257位椭圆曲线点乘的测试用例如表2所示,协处理器计算二元扩域257位椭圆曲线点乘的测试结果如图8所示。

[0121]

表2

[0122]

参数值模多项式px0x20000000000000000000000000000000000000000000000000000000000001001椭圆系数a0x0椭圆参数b0x00e78bcd09746c202378a7e72b12bce00266b9627ecb0b5a25367ad1ad4cc6242b乘数k0x6d3b497153e3e92524e5c122682dbdc8705062e20b917a5f8fcdb8ee4c66663d基点坐标xg0x00a67941e6de8a61805f7bcff0985bb3bed986f1c297e4d8880d82b821c624ee57基点坐标yg0x0193ed5a6707b5908781b860841085f52eefa7fe329a5c811843533a874d027271结果坐标xr0x0083e628cf701ee3141e8873fe55936adf24963f5dc9c6480566c80f8a1d8cc51b结果坐标yr0x01524c647f0c0412defd468bda3ae0e5a80fcc8f5c990fee11602929232dcd9f36

[0123]

4096位rsa私钥运算的测试用例如表3所示,协处理器计算4096位rsa私钥运算的结果如图9所示。

[0124]

表3

[0125]

参数值模数p0x8542d69e4c044f18e8b92435bf6ff7de457283915c45517d722edb8b08f1dfc3操作数a0x64866219af67a447e4058a3ac7b19b4b9326654587d2b759a2cf3f3f b38c97e9求逆结果a-1

0x15291d983bec040eebd7e8afd2afdbcd3e19ef47e27b5b4b9dd48bc8 e5e96dd1

[0126]

素数域和二元扩域模逆运算的测试用例如表4所示,协处理器计算素数域和二元扩域模逆运算的结果如图10所示,图中左侧为素数域模逆运算结果,右侧为二元扩域模逆运算结果。

[0127]

表4

[0128]

参数值模多项式px0x20000000000000000000000000000000000000000000000000000000000001001操作数ax0x138ca30549efb3ad4ad0b64877e422bac1159c96a3bfce2b8ac0c3ce28dec695a求逆结果ax-1

0x1162974ca6a5d256fc82a3b90c2f33d2e4dfb8981d181812c4460e26d2bf18366

[0129]

结合以上测试,本实施例中的协处理器,工作在100mhz的高速时钟和25mhz的apb总线时钟下时,执行一次素数域256位椭圆曲线的点乘运算耗时约30ms,执行一次二元扩域257位椭圆曲线的点乘运算耗时约21.4ms,执行一次4096位rsa私钥运算耗时约744.4ms,执行一次4096位公钥运算耗时约5.8ms,具有极快的处理速度。

[0130]

本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1