在堆叠量子计算设备中的集成电路元件的制作方法

在堆叠量子计算设备中的集成电路元件

1.本技术是申请日为2017年12月12日、申请号为201780088359.0、发明名称为“在堆叠量子计算设备中的集成电路元件”的发明专利申请的分案申请。

技术领域

2.本公开涉及在堆叠量子计算设备中的集成电路元件。

背景技术:

3.量子计算是一种相对新的计算方法,它利用诸如基本状态和纠缠的叠加的量子效应以比经典数字计算机更有效地执行某些计算。与以比特形式(例如,“1”或“0”)存储和操纵信息的数字计算机相反,量子计算系统可以使用量子比特(qubit)操纵信息。量子比特可以指代使能多种状态(例如,处于“0”和“1”状态两者的数据)的叠加的量子设备和/或指代在多种状态下的数据本身的叠加。根据传统术语,量子系统中“0”和“1”状态的叠加可以表示为例如α

│

0》+β

│

1》。数字计算机的“0”和“1”状态分别类似于量子比特的

│

0》和

│

1》基本状态。值

│

α

│2表示量子比特处于

│

0》状态的概率,而值

│

β

│2表示量子比特处于

│

1》基本状态的概率。

技术实现要素:

4.一般地,在一些方面,本公开涉及一个或多个设备,设备包括第一芯片和第二芯片,第一芯片包括超导量子比特,其中超导量子比特包括超导量子干涉器件(superconducting quantum interference device,squid)区域、控制区域和读出区域,并且第二芯片键合到第一芯片,其中第二芯片包括与squid区域重叠的第一控制元件、从控制区域横向移位且不与控制区域重叠的第二控制元件、以及与读出区域重叠的读出器件。

5.设备的实施方式可以包括一个或多个以下特征。例如,在一些实施方式中,读出器件包括谐振器元件和焊盘元件,其中谐振器元件电耦合到焊盘元件,并且焊盘元件与读出区域重叠,而谐振器不与读出区域重叠。

6.在一些实施方式中,焊盘元件与读出区域对称地对准。

7.在一些实施方式中,面向第二芯片并被焊盘元件重叠的读出区域的表面面积小于面向第一芯片的焊盘元件的表面面积。

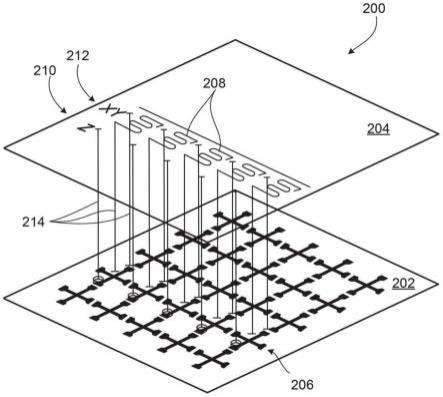

8.在一些实施方式中,焊盘元件可操作以电容地耦合到读出区域。

9.在一些实施方式中,第一芯片包括超导体接地面,其边缘与超导量子比特的控制区域对准,使得该边缘包括凹陷区域,在该凹陷区域中超导体接地面的一部分被移除,并且控制元件在凹陷区域上方对准。

10.在一些实施方式中,面向第一芯片的第二控制元件的表面面积小于面向第二芯片的凹陷区域的表面面积。

11.在一些实施方式中,第二控制元件可操作以电容地耦合到控制区域。

12.在一些实施方式中,第二元件可操作以激励超导量子比特。

13.在一些实施方式中,第一控制元件包括偏置线圈,其中偏置线圈包括布置成环状的超导体材料层,并且其中squid区域包括布置成环形的squid。

14.在一些实施方式中,环状包括内部环状边缘和外部环状边缘,其中内部环状边缘在环形的内部区域内对准,并且外部环状边缘在环形的内部区域外对准。

15.在一些实施方式中,内部环状边缘和定义环形的内部区域的环形的边缘之间的横向距离至少为2微米,并且外部环状边缘和由环形的内部区域定义的环形的边缘之间的横向距离至少为2微米。

16.在一些实施方式中,环状包括内部环状边缘和外部环状边缘,其中外部环状边缘在环形的内部区域内对准。

17.在一些实施方式中,外部环状边缘和定义环形的内部区域的环形的边缘之间的横向距离至少为2微米。

18.在一些实施方式中,第一控制元件可操作以调谐超导量子比特。

19.在一些实施方式中,第一控制元件可操作以电感地耦合到squid区域。

20.在一些实施方式中,第一芯片凸块键合到第二芯片。

21.在一些实施方式中,第一芯片和第二芯片之间存在间隙,其中第一芯片和第二芯片之间的间隙的高度为1-10微米。

22.在一些实施方式中,第一控制元件、第二控制元件和读出器件包括超导体材料。

23.在一些实现方式中,超导量子比特是transmon量子比特、通量量子比特或gmon量子比特。

24.一般地,在一些方面,本公开的主题可以体现在操作量子计算系统的方法中,其中操作量子计算系统包括操作量子计算设备。量子计算设备包括,例如,包括超导量子比特的第一芯片以及键合到第一芯片的第二芯片,其中超导量子比特包括squid区域、控制区域和读出区域,,其中第二芯片包括与squid区域重叠的第一控制元件、从控制区域横向移位且不与控制区域重叠的第二控制元件、以及与读出区域重叠的读出器件。操作量子计算设备可以包括使用量子计算设备相干处理存储在超导量子比特中的量子信息。操作量子计算系统还可以包括从量子计算系统获得输出,并且使用经典电路元件处理输出。

25.根据另一些方面,提供了一种设备,该设备包括:包括量子比特的第一芯片;以及键合到所述第一芯片的第二芯片,所述第二芯片包括读出器件,其中所述读出器件包括在所述读出器件的第一端的第一读出元件,并且包括在所述读出器件的第二端的第二读出元件,其中所述第一读出元件直接地与所述量子比特重叠,并且其中所述第二读出元件从所述量子比特横向移位且不直接地与所述量子比特重叠。

26.根据另一些方面,提供了一种设备,该设备包括:包括量子比特的第一芯片,其中所述量子比特包括第一控制区域和第二控制区域,所述第一控制区域包括超导量子干涉器件(squid);以及键合到所述第一芯片的第二芯片,所述第二芯片包括第一控制元件和第二控制元件,其中所述第一控制元件被布置成电感地耦合到所述第一控制区域,以及其中所述第二控制元件被布置成电容地耦合到所述第二控制区域。

27.可以实施本说明书中描述的主题的特定实施例,以实现一个或多个以下优点。例如,在一些实施例中,本文公开的设备和方法增加了芯片未对准容限,以保持量子比特相干性和量子比特耦合强度,同时减少堆叠量子计算设备(例如倒装芯片架构)中的杂散耦合效

应。额外地,在一些实施例中,本文公开的设备和方法通过3d集成允许增加量子比特密度(例如,从超导量子比特的一维链到超导量子比特的二维阵列)和/或增加量子比特耦合。此外,在一些实施例中,本文公开的设备和方法可以减少可能由沉积的电介质材料引起的量子电路元件中的能量损耗和耗散。

28.一个或多个实施例的细节在附图和以下描述中阐述。从说明书、附图和权利要求书中,其他特征和优点将是显而易见的。

附图说明

29.图1是示出二维量子比特阵列的示例的示意图。

30.图2是示出包括第一芯片和第二芯片的堆叠量子计算设备的示例的示意图。

31.图3a-3b是示出示例堆叠量子计算设备的不同视图的示意图。

32.图3c是示出堆叠量子计算设备的第二芯片的俯视图的示意图。

33.图4a是示出形成在第二芯片上的读出器件的俯视图的示意图。

34.图4b是示出形成在第一芯片上的超导量子比特的读出区域的俯视图的示意图。

35.图4c是示出在第一芯片的读出区域上方对准第二芯片的读出器件的第二芯片的俯视图的示意图。

36.图5a是示出形成在第二芯片上的第一控制元件的俯视图的示意图。

37.图5b是示出第一芯片上超导量子比特的超导量子干涉器件(squid)区域的俯视图的示意图。

38.图5c是示出在第一芯片的squid区域上方对准第二芯片的第一控制元件的第二芯片的俯视图的示意图。

39.图6a是示出形成在第二芯片上的第二控制元件的俯视图的示意图。

40.图6b是示出超导量子比特的控制区域和第一芯片上的凹陷区域的俯视图的示意图。

41.图6c是示出在第一芯片的凹陷区域上方对准第二芯片的第二控制元件的第二芯片的俯视图的示意图。

42.图7是示出堆叠量子计算设备的第二芯片到第一芯片的俯视图的光学显微照片。

具体实施方式

43.量子计算需要相干地处理存储在量子计算机的量子比特(qubits)中的量子信息。超导量子计算是其中量子计算电路元件部分由超导体材料形成的量子计算技术的有希望的实施方式。超导量子计算机通常是多级系统,其中只有前两级被用作计算基础。在某些实施方式中,量子电路元件(例如,量子计算电路元件),诸如量子比特,在非常低的温度下工作,从而可以实现超导性,并且从而热波动不会导致能级之间的转换。额外地,可能优选的是,量子计算电路元件以低能量损耗和耗散操作(例如,量子计算电路元件表现出高品质因数,q)。低能量损耗和耗散可以有助于避免例如量子退相干(decoherence)。

44.在某些类型的量子计算处理器中,诸如量子退火器,量子处理器的量子比特以可控的方式可操作地耦合在一起,使得每个量子比特的量子状态影响与其耦合的其他量子比特的相应的量子状态。取决于处理器设计,所选架构可能会限制可用于耦合的量子比特的

密度和总数,且从而限制处理器执行需要大量量子比特的复杂问题的能力。此外,在某些量子计算设计中,量子比特可能由于与两级系统的相互作用而遭受能量损耗和退相干。两级系统(two-level systems,tls)是固有地存在于电介质衬底中的材料缺陷,源于电介质衬底中原子的两种配置之间的隧穿效应,或者在一些实施方式中,是固有地存在于材料层之间的界面处的材料缺陷。例如,在使用由超导体材料形成的量子比特的量子计算机中,来自例如沉积电介质、量子计算机与其通信的经典电路元件以及来自经典电路元件和量子电路元件之间的连接的有损非超导体材料的存在会导致增加的退相干。为了在量子处理器(诸如具有超导体量子电路元件的量子退火器)中增加量子比特密度并扩大可用于耦合的量子比特数量,可以使用3d集成来构造处理器和相关联的电路元件。也就是说,代替在沿一维和/或二维(例如,x和/或y方向)延伸的芯片的单个平面内制造处理器的量子电路元件,量子电路元件也可以形成在沿第三维(例如,z方向)耦合在一起的多个芯片中。一种在不引入有损处理/电介质的情况下实现3d集成的方式是使用凸块键合来耦合芯片,其中芯片通过例如超导体凸块键合件彼此连接。在一些实施方式中,除了芯片的物理耦合之外,凸块键合件可以用于将来自不同芯片的组件电耦合在一起。可替换地,凸块键合件可以单独用于将不同芯片物理耦合在一起。通过使用超导体凸块键合件进行耦合,有可能实现能量损耗和退相干的减少,否则能量损耗和退相干会在有损非超导体材料中发生。

45.在堆叠量子计算设备的制造过程中,对准是一个挑战,特别是位于单独芯片上的相互作用元件之间的对准,这些元件可以通过凸块键合件的使用来电连接和机械连接。

46.本公开涉及用于耦合堆叠量子计算设备的设备和方法。特别地,在一些实施方式中,本公开涉及提供布置成堆叠的多个芯片,其中堆叠中的第一芯片包括量子比特的二维阵列,并且堆叠中的至少第二芯片包括用于耦合到第一芯片中的量子比特的控制元件。

47.图1是示出超导量子比特的二维阵列100的示例的示意图。超导量子比特的阵列100可以是用于执行量子计算操作的量子计算系统(例如,量子退火器)的一部分。在图1所示的示例中,每个超导量子比特是xmon量子比特,通常以具有四个臂的“加号”的形状示出。量子比特100可以包括但不限于其他类型的量子比特,诸如通量量子比特、transmon量子比特和gmon量子比特。图1描绘了超导量子比特的四乘四阵列100,但是可以以一维(one-dimensional,1d)或二维(two-dimensional,2d)阵列来实施任何数量的量子比特。在一些实施方式中,操作包括超导量子比特的阵列(诸如超导量子比特的阵列100)的量子计算系统需要将阵列的超导量子比特耦合在一起。例如,最近的相邻量子比特102a和102b可以通过它们的相邻臂彼此耦合。类似地,2d阵列中的内部量子比特(例如,量子比特102c和102d)中的每一个可以直接耦合到四个最近的相邻量子比特。例如,量子比特102c可以与量子比特102b、102d、102e和102f耦合。

48.随着2d阵列中量子比特数量的增加,快速地耦合到量子比特变得非常具有挑战性。例如,在诸如阵列100的量子比特阵列中,每个内部量子比特可能需要进行7个单独的连接(例如,到每个最近的相邻量子比特的4个连接和用于读出控制、z控制和xy控制的3个连接)。随着阵列中量子比特数量的增加,用于提供布线的空间减少。一种选择是使用传统互补金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)技术布线量子比特,诸如在多层沉积电介质中形成布线。然而,这种电介质与导致量子比特退相干的高损耗相关联。

49.解决量子比特布线的另一种方式是将布线和其他控制元件定位在耦合到包含量子比特的芯片的单独芯片上。例如,用于阵列100中的每个超导量子比特的各个控制元件(例如,z控制和xy控制)的布线和读出谐振器可以从其上形成量子比特的芯片移动到单独的第二芯片。在一些实施方式中,包含量子比特阵列100的第一芯片使用例如超导体凸块键合件(诸如铟)电连接和机械连接到包含布线和量子比特控制元件的第二芯片。

50.图2是示出包括第一芯片202和第二芯片204的堆叠量子计算设备200的示例的示意图。第一芯片202包括超导量子比特的二维阵列206。示例阵列206中的每个超导量子比特是xmon量子比特,尽管也可以代替地使用其他量子比特。第二芯片204包括读出器件208和控制元件210、212。第一芯片202和第二芯片204中的每一个还可以包括用于执行数据处理操作的一个或多个电路元件。

51.第一芯片202的超导量子比特可以形成在衬底上。第一芯片的衬底可以由例如低损耗和单晶电介质(诸如单晶硅或蓝宝石)形成。低损耗电介质可以部分地通过在微波频率(1-10ghz)处具有1e-5或小于1e-5的小损耗正切来定义。可以替代地使用其他材料用于衬底。

52.第二芯片204的读出器件208可以包括例如读出谐振器。控制元件210、212可以包括例如第一控制元件210(例如,z控制)和第二控制元件212(例如,xy控制)。当控制脉冲施加到z控制元件时,超导量子比特z控制元件可操作以调谐该控制元件耦合到的超导量子比特的操作频率。当控制脉冲施加到xy控制元件时,超导量子比特xy控制元件可操作以激励xy控制元件耦合到的超导量子比特。读出器件可操作以通过探测谐振器元件的频率来读出读出器件电容地耦合到的超导量子比特的状态。

53.类似于第一芯片202,第二芯片204还可以包括由适合量子电路的低损耗电介质材料(诸如单晶硅或蓝宝石)形成的衬底。衬底的厚度可以在例如大约10微米和大约1000微米之间。

54.第一芯片202可以通过键合件214(例如,凸块键合件)电和/或机械地键合到第二芯片。

55.图3a-3b是示出堆叠量子计算设备的示例的不同视图的示意图。图3a示出了第一芯片302在第二芯片304的顶部对准并且使用凸块键合件306电连接和/或机械连接的堆叠量子计算设备300的截面图。凸块键合件306可以包括超导体材料,以避免可能位于例如第一芯片302上的量子比特的能量损耗和退相干。例如,用作凸块键合件306的适合的超导体材料包括但不限于具有薄层金的铟、铅、铼、钯或铌。

56.凸块键合件306的厚度可以设置成使得第一芯片302和第二芯片304以间隙308隔开。间隙308的近似高度可以在基于用于沉积和/或移除材料以形成凸块键合件306(和/或可能影响距离的其他组件)的(多个)沉积技术以及用其测量间隙高度的(多个)计量技术的准确度和/或精度限制的不确定性范围内。在一些实施方式中,第一芯片302和第二芯片304之间的间隙的高度至少为5微米。

57.图3b示出了其中第二芯片304在第一芯片302上方对准的堆叠量子计算5设备布局320的第二芯片304的俯视图的示意图。第一芯片302包括超导量

58.子比特322,该超导量子比特322包括读出区域324、超导量子干涉器件(squid)区域326和控制区域328。超导量子比特322的读出区域324对应于围绕超导量子比特322的中

心定义的超导量子比特322的区域,并且遵循

59.虚线轮廓内的超导量子比特322的中心部分的轮廓。例如,关于图3b所示的0示例,超导量子比特322是xmon型量子比特,其呈现具有四个长臂的十字

60.形形状并且额外地包括从超导量子比特322的中心分支出来的左上象限中的较短臂的一部分(例如,对应于超导量子比特的squid环状)。当第一芯片和第二芯片关于彼此对准时,读出区域324可以被成形为覆盖超导量子比特322

61.的这些区域:包括中心部分、四个臂中的每一个臂的一部分,并且可选地包5括对应于超导量子比特322的squid环状的分支的一部分。下面参照图4a至图4c更详细地讨论读出区域324。

62.超导量子比特322的squid区域326对应于超导量子比特322的、包括虚线轮廓内的超导量子比特322的中心分支出来的左上象限中的较短臂的一

63.部分(例如,对应于squid环状)的区域。下面参照图5a至图5c更详细地0讨论squid区域326。

64.超导量子比特322的控制区域328对应于超导量子比特322的区域(例如,包括超导量子比特322的一个臂的一部分的区域)。控制区域328邻近凹陷区域329,该凹陷区域329形成在面向控制区域328的接地面的边缘内,其中

65.直接邻近超导量子比特322的超导体接地面的“标签(tab)”部分已经被移5除。例如,关于图3b所示的示例,超导量子比特322是xmon型量子比特,

66.并且其中凹陷区域329是邻近超导量子比特322的臂中的一个臂的超导体接地面的已经被移除的一部分。下面参照图6a至图6c更详细地讨论控制区域328和凹陷区域329。

67.尽管量子比特322被示出为xmon型量子比特,但是也可以替代地使用0其他量子比特,每个量子比特还包括对应的读出区域、squid区域和控制区

68.域,如这里详细描述的。

69.第二芯片304包括读出器件330,该读出器件包括电耦合到焊盘(pad)元件334的谐振器元件332。第二芯片304还可以包括布线元件336。凸块键合件(例如,306)接触第一芯片302和第二芯片304。额外地,第二芯片304可以包括第一控制元件338(例如,z控制元件)和第二控制元件340(例如,xy控制元件)。

70.在一些实施方式中,第二芯片304上的焊盘元件334定向在第二芯片304上,使得当第一芯片302和第二芯片304对准时(例如,如图3a所示),焊盘元件334与第一芯片302上的对应的超导量子比特322的读出区域324对称地对准,使得焊盘元件334可以电磁地耦合(例如,电容地)到第二芯片的读出区域330。在一些实施方式中,如果焊盘元件334和读出区域324具有相同的形状,它们可以对称地对准,使得它们的中心彼此重合,并且它们的边缘(或者,当边缘弯曲时,它们边缘的切线)基本上彼此平行设置。额外地,第二芯片304上的读出器件330的谐振器元件332被定向在第二芯片304上,使得当第一芯片302和第二芯片304对准时(例如,如图3a所示),第一芯片302上的超导量子比特322不直接位于谐振器元件332下方。参照图4a至图4c讨论读出器件的更多细节。

71.在一些实施方式中,第一控制元件338布置在第二芯片304上,使得第一芯片302上的超导量子比特322的squid区域326相对于第二芯片304上的第一控制元件338直接在下方对准。通过将squid区域326直接定位在第一控制元件338下方,第一控制元件338可以通过

squid区域326电磁地耦合(例如,电感地耦合)到量子比特。下面参照图5c更详细地讨论squid区域326相对于第一控制元件338的对准。

72.在一些实施方式中,第二控制元件340布置在第二芯片304上,使得第二控制元件340从超导量子比特的控制区域328横向移位,并且不与超导量子比特的控制区域328重叠。相反,第二控制元件340在第一芯片302上的超导量子比特322的凹陷区域329上方对准。通过将凹陷区域329直接定位在第二控制元件340下方,并将第二控制元件340从控制区域328移位,第二控制元件340可以通过控制区域328电磁地耦合(例如,通过边缘场的互电容)到量子比特。下面参照图6c更详细地讨论控制区域328相对于第二控制元件340的对准。

73.在一些实施方式中,如图3a所示,第一芯片302和第二芯片304之间的间隙308被设置成在第一芯片302和第二芯片304上的电路元件(例如,第一芯片302上的超导量子比特322的读出区域324和第二芯片304上的读出器件330)之间实现期望的电容或电感耦合。

74.例如,第一芯片302的器件表面和第二芯片304的结构元件表面之间的间隙308的高度可以被设置为在大约0.5μm和大约100μm之间(例如,在大约10μm和大约20μm之间、在大约1μm和10μm之间、在大约0.5μm和大约20μm之间、在大约0.5μm和大约15μm之间、在大约0.5μm和大约10μm之间、在大约0.5μm和大约5μm之间、或者在大约0.5μm和大约2.5μm之间)。

75.图3c是示出堆叠量子计算设备的第二芯片的俯视图350的示意图,其中第二芯片304通过将两个芯片键合在一起的凸块键合件(例如,超导体凸块键合件306)与第一芯片302对准。在图3c的示意图中,白色区域对应于超导体材料,阴影区域对应于衬底的暴露表面。在图3c的示意图中,第二芯片304的超导体层和衬底是透明的,并且第二芯片304上的各个电路元件被描绘为仅由暴露第二芯片的衬底的区域(例如,超导体层已经被移除的区域)定义的轮廓。

76.第一芯片302包括超导量子比特354,其中白色区域对应于超导体材料(例如,铝),以及黑色区域对应于衬底(例如,电介质衬底)的暴露表面。图3c中描绘的超导量子比特354是xmon型超导量子比特。也可以替代地使用其他量子比特类型,例如gmon、fluxmon或transmon量子比特。第一芯片302上的读出区域356、squid区域358、以及与超导量子比特354的控制区域360的边缘相邻的凹陷区域361由各个虚线轮廓识别。

77.第二芯片304包括读出器件362,该读出器件362包括电耦合焊盘元件364和谐振器元件366。焊盘元件364包括在超导量子比特354的中心上方对准的十字形超导体焊盘。如图3c所示,焊盘元件364被示为在读出区域356的虚线轮廓内对准的透明的十字形轮廓,然而,十字形轮廓的内部应理解为由超导体材料组成。谐振器元件366包括例如细长的超导体共面波导迹线。谐振器元件366的谐振频率/模式部分由其长度和有效介电常数确定。为了节省第二芯片304上的空间,谐振器元件366被布置成蛇形形状。

78.第二芯片304额外地包括第一控制元件368,当第一芯片302和第二芯片304对准并键合在一起时(例如,通过凸块键合件306),第一控制元件368与第一芯片302上的超导量子比特354的squid区域358重叠。在图3c中描绘了第一控制元件368,使得第一控制元件368的超导体层(例如,铝)是透明的,并且第一控制元件368的轮廓(例如,超导体材料已经被移除并且衬底被暴露的区域)被描绘为黑色。下面参照图5a和5c讨论第一控制元件368的进一步细节。

79.第二芯片304还包括第二控制元件370,当第一芯片302和第二芯片304对准并键合

在一起时(例如,通过凸块键合件306),第二控制元件370与第一芯片302上的超导量子比特354的凹陷区域361重叠。第二控制元件370在图3c中描绘,使得第二控制元件370的超导体层(例如,铝)是透明的,并且第二控制元件370的轮廓(例如,超导体材料已经被移除并且衬底被暴露的区域)以黑色描绘。下面参照图6a和6c讨论第二控制元件370的进一步细节。

80.图4a是示出示例性读出器件402的俯视图的示意图,该读出器件402形成在堆叠量子计算设备的第二芯片404上,并且当第一芯片(例如,图4b所示的第一芯片410)和第二芯片键合在一起时,该读出器件402将面向第一芯片。图4a中的白色区域对应于至少存在超导体材料层的区域,而灰色/黑色区域对应于不存在超导体材料并且衬底可以被暴露的区域。读出器件402(对应于图4a所示虚线区域内的元件)包括例如焊盘元件412和谐振器元件414,并且可以由超导体材料(例如,铝)制成。读出器件414的示例包括四分之一波长共面波导谐振器。

81.在一些实施方式中,谐振器元件414是分布式元件谐振器或集总元件谐振器,诸如由超导体材料(例如,铝)形成的共面波导谐振器,其中谐振器的频率部分地由谐振器长度来确定。

82.在堆叠量子计算设备的操作期间,焊盘元件412可以电磁地耦合(例如,电容地耦合)到第一芯片(例如,图4b中的第一芯片410)上的超导量子比特(例如,图4b中的超导量子比特408),其中量子比特直接位于焊盘元件412下方。然后可以在堆叠量子计算设备的操作期间通过探测谐振器元件414的频率来读取第一芯片410上的超导量子比特408。焊盘元件412可以具有各种表面区域几何形状,部分地取决于超导量子比特的各个形状和所需的电容量。例如,如图4b所示,超导量子比特408是xmon型量子比特,其呈现具有四个长臂的十字形形状,并且额外地包括从超导量子比特408的中心分支出来的右上象限中的较短臂的一部分(例如,对应于超导量子比特的squid环状)。图4a所示的焊盘元件412可以是十字形的,使得当第一芯片和第二芯片对准时,被焊盘元件412覆盖的超导量子比特408的区域包括中心部分、超导量子比特408的四个臂中的每一个臂的一部分。在一些实施方式中,对应于超导量子比特408的squid环状的分支的一部分也被焊盘元件412覆盖。在另一个示例中,对于gmon量子比特,焊盘元件可以具有正方形或矩形形状。

83.在一些实施方式中,图4a所示的谐振器元件414和焊盘元件412由第二芯片404上的相同层形成。在一些实施方式中,谐振器元件414和焊盘元件412形成在第二芯片404上的不同层中。

84.图4b是示出形成在第一芯片410上的示例性超导量子比特408的俯视图的示意图,其中第一芯片410将被键合到第二芯片404。白色区域对应于存在超导体材料的区域,而阴影区域对应于不存在超导体材料并且衬底可以被暴露的区域。第一芯片410包括超导量子比特408,诸如xmon量子比特,尽管也可以替代地使用其他类型的超导量子比特。在图4b所示的示例中,超导量子比特408的读出区域406对应于超导量子比特408的中心周围的区域并且遵循超导量子比特408的中心部分(包括超导量子比特408的四个臂中的每一个的至少一部分)的轮廓。额外地,在一些实施方式中,对应于从中心延伸到超导量子比特408的右上角的squid环状的分支407的一部分也包括在超导量子比特408的读出区域406中。

85.图4c是示出堆叠量子计算设备的第二芯片410的俯视图的示意图,该堆叠量子计算设备包括键合到第一芯片404的第二芯片410,使得与第二芯片上的电路元件对准的第一

芯片上的电路元件的轮廓可见。如图4c所示,包括焊盘元件412、谐振器元件414的读出器件402被对准,使得焊盘元件412直接位于第一芯片410上超导量子比特408的读出区域406的上方。相反,谐振器元件414横向移位,使得其不直接与第一芯片410上的超导量子比特408重叠。这种布置可以减少谐振器元件414和超导量子比特408之间不期望的耦合和/或干扰。

86.在堆叠量子计算设备的操作期间,读出器件402可以电磁地耦合到超导量子比特408位于读出区域406中的部分。例如,焊盘元件412可以电容地耦合到超导量子比特408的读出区域406。焊盘元件412和量子比特之间的电容量可以取决于焊盘元件412和量子比特408的相对大小、二者之间的重叠以及第一和第二芯片之间的间隙距离而变化。在一些实施方式中,焊盘元件412的维度可以被修改以实现特定电容。例如,调整焊盘元件412的维度,以实现量子比特408和焊盘元件412之间大约1到50毫微微法之间的电容。其他电容值也是可能的。

87.在一些实施方式中,包括在第一芯片上的超导量子比特408的读出区域406中的超导量子比特406的面向第二芯片上的焊盘元件412的表面面积(例如,在图4c中描绘的虚线轮廓内的超导量子比特408的面积)小于焊盘元件412面向第一芯片的表面面积。例如,十字形焊盘元件412的一个或多个各个臂的一个或多个维度(例如,宽度416)可以被扩大,以允许键合的第一芯片和第二芯片之间的未对准。也就是说,即使在第一芯片和第二芯片之间存在轻微的未对准,读出器件402和超导量子比特408之间的相互耦合的幅度保持基本上相同,因为焊盘元件402仍将在超导量子比特408的相同区域上方对准。示例性的未对准可以包括例如y方向上的几微米。因此,将焊盘元件412的臂上的宽度416增加几微米使得该宽度比读出区域406内超导量子比特408的臂的相应的宽度(例如,宽度420)大几微米允许了在第一和第二芯片的键合过程期间各个读出区域406和超导量子比特408的未对准。

88.在一些实施方式中,十字形焊盘元件412的一个或多个臂的长度(例如,长度422)可以改变,以调节量子比特408和焊盘元件412之间的电容。通常,焊盘元件412的表面面积和量子比特408的在读出区域406中的表面面积之间的重叠量部分地指示以平行板电容的形式的量子比特408和焊盘元件412之间的电容。

89.图5a是示出形成在第二芯片上的第一控制元件502(诸如图2中的控制元件210)的俯视图的示意图。白色区域对应于至少存在超导体材料层的区域,而阴影区域对应于不存在超导体材料并且衬底可以被暴露的区域。第一控制元件502可以包括例如量子比特z控制元件。当控制脉冲施加到z控制元件时,量子比特z控制元件可操作以调谐第一控制元件502耦合到的超导量子比特的操作频率。图5a所示的第一控制元件502包括由布置在衬底的表面上的超导体材料层形成的偏置线圈。由超导体层形成的偏置线圈包括耦合到接地面501的第一部分504、在堆叠量子计算设备的操作期间耦合到提供控制脉冲的源的第二部分506、以及第三环状部分508。

90.偏置线圈的环状部分508包括内部环状边缘503和外部环状边缘505。外部环状边缘505通过间隙507与超导体接地面501分开。如图5a所示,第一部分504和第二部分506中超导体材料的宽度509比环状部分508中超导体材料的宽度511窄得多。这减少了偏置线的足迹(footprint)。为了防止不期望的返回电流,在偏置线短路的地方连接接地连接。这可以使用凸块键合件来实现,诸如在图3c所示的偏置线区域390两侧的凸块键合件306。内部环状边缘503和外部环状边缘505形成在第二芯片上,使得当第一芯片和第二芯片对准并键合

在一起时(例如,内部环状边缘包含在squid区域510的内部环形区域512内),内部环状边缘在第一芯片上的超导量子比特的squid区域510内。外部环状边缘505被形成为使得当第一芯片和第二芯片对准时,第一芯片上的超导量子比特的squid区域510的内部环形区域512被第二芯片上的环状部分508的外部环状边缘505完全包含。

91.图5b是示出超导量子比特(诸如图2所示的超导量子比特206)的超导量子干涉器件(squid)区域510的示例的俯视图的示意图。白色区域对应于存在超导体材料层的区域,而阴影区域对应于不存在超导体材料并且第一芯片的衬底可以被暴露的区域。在图5b所示的示例中,squid区域510内的squid物理地耦合到超导量子比特的中心区域并从该中心区域延伸。squid区域510包括以大致环形布置的超导体材料层,其中超导体材料在多个位置被约瑟夫森(josephson)结514中断。约瑟夫森结514的超导体布线用黑色描绘。squid区域510的一部分可以由超导体接地面513形成。在本示例中,squid区域510因此具有其中不存在超导体的内部环形区域512。内部环形区域512的面积/周长由超导体材料的边缘516定义。

92.当将第一芯片对准第二芯片以提供堆叠量子计算设备时,第一控制元件502在对应的量子比特的squid区域510上方对准。在堆叠量子计算设备的操作期间,第一控制元件502可以电磁地耦合(例如,电感地耦合)到squid区域510内的squid。当施加控制脉冲到第一控制元件502时,电感耦合允许量子比特的操作频率被调谐。第一控制元件502和squid区域510的squid利用互感而相关联。例如,互感可以在大约0.1ph到大约100ph之间。

93.图5c是示出在squid区域510上方对准的第一控制元件502的俯视图的示意图。通常,对于超导体电路元件,电流主要沿着形成电路元件的超导体层的边缘流动。结果,形成第一控制元件偏置线圈508的超导体材料的边缘相对于形成squid内部环形区域512的超导体材料的位置的变化可能导致第一控制元件和squid区域之间的所期望的互感的变化,以及增加杂散互感,这可以导致量子比特退相干。这种变化可能是由于例如在键合过程期间第一芯片和第二芯片之间的未对准。

94.为了实现与squid区域510的高耦合以及减少杂散互感,并避免在键合时由未对准引起的所期望的互感的变化,第一控制元件502的偏置线圈508保持基本地对称。例如,通过将偏置线圈508的内部环状部分503提供为具有相对于偏置线圈508的外部环状边缘505对称的形状(例如,使得每个的杂散磁场相等且相反),来自环状部分508的杂散通量通过对称抵消来抵消自身,同时保持与squid区域510的高耦合。此外,squid区域510位于接地面附近并且远离超导量子比特的其他特征(例如,超导量子比特的读出区域或控制区域),使得来自这些其他特征(例如,除squid区域510之外的其他特征,或其他相邻超导量子比特)的通量的影响减小。

95.此外,偏置线圈的环状部分508的面积相对于squid区域510的内部环形区域512变大,以提供对未对准的一定的容限。也就是说,当第一和第二芯片之间存在未对准误差时,偏置线圈的内部环状边缘503的位置更有可能保持位于内部环形区域512正上方的位置。额外地,外部环状边缘505的位置更有可能保持远离内部环形区域512,使得由沿着外部环状边缘505行进的电流引起的杂散互感。例如,内部环状边缘503和内部环形区域512的边缘516之间的横向距离(例如,横向距离520)在约1微米至约10微米的范围内。额外地,在一些实施方式中,内部环形区域的边缘516和外部环状的边缘505之间的横向距离(例如,横向距

离522)在约1微米至约20微米的范围内。横向距离520和522的范围可以取决于堆叠量子计算设备配置的对准误差。例如,如果对准误差包括沿x轴或y轴2微米的未对准,横向距离520和522的范围可以设置为4微米。

96.在一些实施方式中,当第一芯片对准并键合到第二芯片时,偏置线圈508的内部环状边缘503和外部环状边缘505可以位于内部环形区域512内。在这种情况下,外部环状边缘505在内部环形区域512的边缘516内具有至少2微米的横向距离。

97.图6a是示出第二芯片上的第二控制元件602(诸如图2的第二控制元件212)的示例的俯视图的示意图。白色区域对应于存在超导体材料的区域,而阴影区域对应于不存在超导体材料并且衬底可以被暴露的区域。第二控制元件602可以包括例如量子比特xy控制元件。当施加控制信号到xy控制元件时,超导量子比特xy控制元件可操作以激励xy控制元件耦合到的量子比特。图6a所示的第二控制元件602包括焊盘元件604和布线元件606。焊盘元件604位于布线元件606的一端。布线元件606可以耦合到向xy控制元件提供控制信号的信号源。焊盘元件604和布线元件606形成在第二芯片上的超导体层(例如,超导体薄膜)中,其中在超导体层中焊盘元件604和布线元件606通过超导体层中的间隙607与超导体接地面601分离(例如,通过暴露衬底)。焊盘元件604包括焊盘元件长度605和焊盘元件宽度603。

98.图6b是示出第一芯片上的超导量子比特(诸如图2的超导量子比特206)的控制区域606的俯视图的示意图。一般地,超导量子比特的控制区域包括超导量子比特的这样的区域(例如,超导量子比特的臂的一部分):在该区域中,第一芯片上的超导量子比特可以由第二芯片上的第二控制元件602(例如,xy控制元件)激励,其中第二控制元件在第二控制元件602施加控制信号时耦合到第二芯片。在超导量子比特是xmon量子比特类型的示例中,超导量子比特的控制区域606包括超导量子比特的一个臂的至少一部分。

99.白色区域对应于存在超导体材料的区域,而阴影区域对应于不存在超导体材料并且衬底可以被暴露的区域。图6b中还示出了超导体接地面611。接地面611的边缘608平行于控制区域606的边缘610对准,并且通过超导体材料中的间隙613(例如,衬底暴露的区域)与边缘610分开。接地面611的边缘608还包括凹陷(或凹口或凹槽)区域612,在该区域中不存在超导体材料并且衬底可以被暴露。凹陷区域612包括凹陷区域长度614和凹陷区域宽度616,它们可以分别大于焊盘元件长度605和焊盘元件宽度603。

100.图6c是示出在图6a的凹陷区域612上方对准的图6a的第二控制元件602的俯视图的示意图。图6c中的示意图还示出了超导量子比特的控制区域606的轮廓,该控制区域606邻近图6b的凹陷区域612并且相对于第二控制元件602对准。还示出了第一芯片上的接地面611。如图6c所示,第二控制元件602的焊盘元件604从超导量子比特的控制区域606横向移位,并且不与超导量子比特的控制区域606重叠。相反,第二控制元件602在凹陷区域612上方对准。如图6c所示,通过从控制区域606横向移位第二控制元件602,可以避免显著的过度耦合(如果第二控制元件602直接放置在控制区域606上或者与控制区域606重叠,则可能发生这种过度耦合)。利用图6c所示的布置,第二控制元件602和超导量子比特的控制区域606通过第二控制元件602和超导量子比特的控制区域606之间的边缘场的互电容电容地耦合。例如,第二控制元件602和超导量子比特的控制区域606具有30埃(attofarads)的互电容,以实现超导量子比特的控制(例如,xy控制)。

101.在一些实施方式中,当第一芯片和第二芯片键合在一起时,第二控制元件602被对

准为完全在凹陷区域612的区域内。选择凹陷区域612的表面区域以考虑键合过程的未对准,使得第二控制元件602的边缘在凹陷区域612内完全对准。此外,在一些实施方式中,第二控制元件602的面向第一芯片(该第一芯片包括超导量子比特)的总表面面积小于面向包括第二控制元件612的第二芯片的凹陷区域612的总表面面积。例如,如图6a所示,焊盘元件604具有矩形形状,其具有定义焊盘元件604的总表面面积的长度605和宽度603。如图6b所示,在本示例中,凹陷区域612具有矩形形状,其具有定义凹陷区域612的总表面面积的长度614和宽度616。焊盘元件604和凹陷区域612可以替代地使用其他形状。通过提供具有小于面向第二芯片的凹陷区域的总表面面积的面向第一芯片的总表面面积的第二控制元件602,可以减少由于未对准而可能发生的杂散耦合。

102.图7是示出具有键合到第二芯片(诸如图2中的芯片204)的第一芯片(诸如图2中的芯片202)的示例性堆叠量子计算设备的俯视图的示意图。该视图通过第一芯片获得,其中第一芯片的超导体材料被描绘为透明的。如图7所示,xmon量子比特702提供在第一芯片上,并且包括超导量子比特702的读出区域704、squid区域706和控制区域708。凹陷区域710形成在面向控制区域708的接地面的边缘内。第二芯片的读出器件712与第一芯片的读出区域704对准。例如,读出器件714的焊盘元件714(例如,焊盘元件412)的一部分在读出区域704下方对准。额外地,第一控制元件720(例如,第一控制元件502)的偏置线圈718的环状部分716(例如,内部环状503)在squid区域706的内部环形区域(例如,内部环形区域512)内对准。此外,第二控制元件722(例如,控制元件602)在凹陷区域710内对准,使得控制元件的边缘在凹陷区域内对准并从量子比特移位。

103.超导(可替换地超导体)材料可以理解为在超导临界温度或低于超导临界温度时表现出超导特性的材料。超导材料的示例包括铝(超导临界温度为1.2开尔文)和铌(超导临界温度为9.3开尔文)。用于形成本文公开的设备的超导体材料可以具有例如约10纳米至约1000纳米范围内的厚度。

104.可用于形成量子计算电路元件的超导体材料的示例是铝。铝可以与电介质键合使用,以建立约瑟夫森结,约瑟夫森结是量子计算电路元件的常见组件。可以用铝形成的量子计算电路元件的示例包括电路元件,诸如超导体共面波导、量子lc振荡器、量子比特(例如通量量子比特或电荷量子比特)、超导量子干涉器件(squid)(例如射频squid或dc-squid)、电感器、电容器、传输线、接地面等。

105.对于本文公开的某些电路元件,诸如约瑟夫森结,可能需要引入一层或多层电介质材料。这种电介质材料层可以形成为具有例如约50纳米至约2000纳米范围内的厚度。

106.本文描述的工艺可能需要一种或多种材料的沉积,诸如超导体、电介质和/或金属。取决于所选择的材料,这些材料可以使用沉积工艺来沉积,诸如化学气相沉积、物理气相沉积(例如蒸发或溅射)、或外延技术以及其他沉积工艺。本文描述的工艺也可能需要在制造过程中从设备中移除一种或多种材料。取决于要移除的材料,移除工艺可以包括例如湿法蚀刻技术、干法蚀刻技术或剥离工艺。

107.本说明书中描述的量子主题和量子操作的实施方式可以在合适的量子电路中实施,或者更一般地,在量子计算系统中实施,包括本说明书中公开的结构及其结构等同物,或者在它们中的一个或多个的组合中实施。术语“量子计算系统”可以包括但不限于量子计算机、量子信息处理系统、量子密码系统或量子模拟器。

108.术语量子信息和量子数据是指由量子系统承载、保持或存储的信息或数据,其中最小的非平凡系统是量子比特,例如定义量子信息的单位的系统。应当理解,术语“量子比特”包括在对应的上下文中可以适当近似为两级系统的所有量子系统。这种量子系统可以包括例如具有两级或更多级的多级系统。举例来说,这样的系统可以包括原子、电子、光子、离子或超导量子比特。在许多实施方式中,计算基础状态用基态和第一激励状态来识别,然而应当理解,计算状态用更高级的激励状态来识别的其他设置也是可能的。应当理解,量子存储器是能够以高保真度和高效率长时间存储量子数据的器件,例如光用于传输以及物质用于存储和保存量子数据的量子特征(例如叠加或量子相干)的光-物质界面。

109.量子电路元件(例如,量子计算电路元件)包括用于执行量子处理操作的电路元件。也就是说,量子电路元件可以被配置成利用量子力学现象(诸如叠加和纠缠)以非确定性方式对数据执行操作。某些量子电路元件(诸如量子比特)可以被配置为同时表示和操作多于一种状态的信息。可以用本文公开的工艺形成的超导体量子电路元件的示例包括电路元件,诸如共面波导、量子lc振荡器、量子比特(例如,通量量子比特或电荷量子比特)、超导量子干涉器件(squid)(例如,射频squid或dc-squid)、电感器、电容器、传输线、接地面等。

110.相比之下,经典电路元件通常以确定性的方式处理数据。经典电路元件可以被配置为通过对数据执行基本的算术、逻辑和/或输入/输出操作来共同执行计算机程序的指令,其中数据以模拟或数字形式表示。在一些实施方式中,经典电路元件可用于通过电或电磁连接向量子计算电路元件发送数据和/或从量子计算电路元件接收数据。可以用本文公开的工艺形成的经典电路元件的示例包括快速单通量量子(rapid single flux quantum,rsfq)器件、互易量子逻辑(reciprocal quantum logic,rql)器件和ersfq器件,它们是不使用偏置电阻器的rsfq的节能版本。其它经典电路元件也可以用本文公开的工艺形成。

111.在使用超导体量子计算电路元件和/或超导体经典电路元件(诸如本文所述的电路元件)的量子计算系统的操作过程中,超导体电路元件在低温恒温器中被冷却到允许超导体材料呈现超导体特性的温度。

112.虽然本说明书包含许多具体的实施方式细节,但是这些细节不应被解释为对所要求保护的范围的限制,而是对特定于特定的实施方式的特征的描述。本说明书中在单独的实施方式的上下文中描述的某些特征也可以在单个实施方式中组合实施。相反,在单个实施方式的上下文中描述的各种特征也可以在多个实施方式中单独实施或以任何合适的子组合实施。此外,尽管上述特征可以被描述为在某些组合中起作用,并且甚至最初是这样要求保护的,但是在一些情况下,可以从该组合中删除所要求保护的组合中的一个或多个特征,并且所要求保护的组合可以指向子组合或子组合的变体。

113.类似地,尽管在附图中以特定顺序描绘了操作,但这不应理解为要求以所示的特定顺序或顺序执行这些操作,或者要求执行所有所示的操作,以获得期望的结果。例如,权利要求中列举的动作可以以不同的顺序执行,并且仍然获得期望的结果。在某些情况下,多任务处理和并行处理可能是有利的。此外,上述实施方式中各种组件的分离不应理解为在所有实施方式中都需要这种分离。

114.已经描述了许多实现方式。然而,应当理解,在不脱离本发明的精神和范围的情况下,可以进行各种修改。其他实施方式也在以下权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1