用于存储器装置的可配置数据保护电路系统的制作方法

本公开大体上涉及半导体存储器及方法,且更特定来说,涉及用于存储器装置的可配置数据保护电路系统的设备、系统及方法。

背景技术:

1、存储器装置通常被提供为计算机或其它电子系统中的内部半导体集成电路。存在许多不同类型的存储器,包含易失性及非易失性存储器。易失性存储器可能需要电力来维持其数据(例如,主机数据、错误数据等),且包含随机存取存储器(ram)、动态随机存取存储器(dram)、静态随机存取存储器(sram)、同步动态随机存取存储器(sdram)及晶闸管随机存取存储器(tram)等等。非易失性存储器可通过在不被供电时保留经存储数据来提供持久数据,且可包含nand快闪存储器、nor快闪存储器、铁电随机存取存储器(feram)及电阻可变存储器,例如相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)及磁阻式随机存取存储器(mram),例如自旋力矩转移随机存取存储器(stt ram)等等。

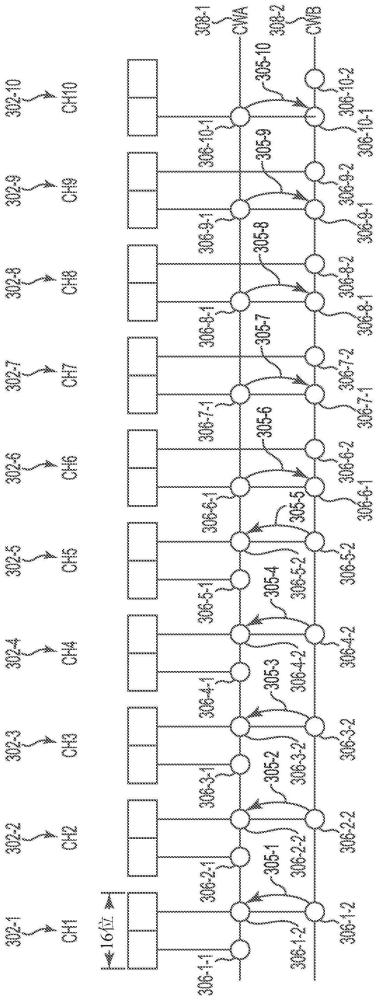

2、存储器控制器可通过多个通道与存储器装置通信。每一通道可具有对应于输入/输出链路(例如,dq引脚)的数量的特定宽度。因此,每通道的存储器装置的数量可取决于通道宽度及存储器装置的模式(例如,类型)。例如,一些存储器装置可为具有8个数据(例如,dq)引脚的x8存储器装置,而其它存储器装置可为具有16个数据引脚的x16存储器装置。

3、各种数据保护方案可被用来确保写入到存储器装置及从存储器装置读取的数据的完整性。例如,可被称为“芯片删除”方案的一些数据保护方案以允许在特定通道出故障(即,对应于所述通道的特定存储器裸片或芯片出故障)的情况下恢复用户数据的方式将用户数据及奇偶校验数据作为码字跨多个通道散布。

技术实现思路

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述多个通道中的每一者具有n个位的宽度,其中n是大于一的整数。

3.根据权利要求1所述的设备,其中从所述多个存储器装置传送的数据形成码字,每一码字包含来自所述多个存储器装置中的第一存储器装置的数据及来自所述多个存储器装置中的第二存储器装置的数据,其中所述第一存储器装置及所述第二存储器装置耦合到不同通道。

4.根据权利要求3所述的设备,其中所述码字中的每一者包含从耦合到每一通道的两个存储器装置中的一者传送的数据。

5.根据权利要求1至4中任一权利要求所述的设备,其中经配置以当所述数据保护电路系统处于第一操作模式时将i/o引脚映射到码字的编码器电路系统及解码器电路系统与经配置以当所述数据保护电路系统处于第二操作模式时将i/o引脚映射到码字的编码器电路系统及解码器电路系统是相同的。

6.根据权利要求1至4中任一权利要求所述的设备,其中所述第一操作模式是x8模式及x16模式中的一者且所述第二操作模式是所述x8模式及所述x16模式中的另一者。

7.根据权利要求1至4中任一权利要求所述的设备,其中所述数据保护电路系统是芯片删除电路系统。

8.根据权利要求1至4中任一权利要求所述的设备,其中所述多个通道中的每一者是低功率双倍数据速率5(lpddr5)通道。

9.一种方法,其包括:

10.根据权利要求9所述的方法,其中每一存储器通道具有相同通道宽度。

11.根据权利要求9至10中任一权利要求所述的方法,其进一步包括当芯片删除电路系统以所述第二模式进行配置时,单独存取来自所述数个存储器装置中的第一存储器装置的数据及来自所述数个存储器装置中的第二存储器装置的数据。

12.一种设备,其包括:

13.根据权利要求12所述的设备,其中所述多个多路复用器包含耦合到第一解码器的所述多路复用器的第一群组及耦合到第二解码器的所述多路复用器的第二群组。

14.根据权利要求13所述的设备,其中当所述芯片删除电路系统处于第二操作模式时,所述多个多路复用器的所述第一群组耦合到第一多个通道且所述多个多路复用器的所述第二群组耦合到第二多个通道。

15.根据权利要求12至14中任一权利要求所述的设备,其中所述多个符号中的每一符号基于所述芯片删除电路系统是处于第一模式还是第二模式而路由到不同多路复用器。

16.根据权利要求12至14中任一权利要求所述的设备,其中排中的存储器装置的数目由所述排中的所述多个存储器装置的模式来确定。

17.根据权利要求16所述的设备,其中当所述多个存储器装置处于第一模式时,每一排包含每通道的一个存储器装置,且其中当所述多个存储器装置处于所述第二操作模式时,每一排包含每通道的两个存储器装置。

18.根据权利要求12至14中任一权利要求所述的设备,其中每一偶数码字包括偶数数据符号且每一奇数码字包括奇数数据符号。

19.根据权利要求12至14中任一权利要求所述的设备,其中所述芯片删除电路系统的模式确定哪些通道提供数据符号及哪些通道提供奇偶校验符号。

技术总结

本公开涉及与可配置数据保护电路系统相关的系统、设备及方法。一种存储器包含:多个存储器装置;及存储器控制器,其能够经由多个通道耦合到所述存储器。所述通道包括所述多个存储器装置的相应子集。所述存储器控制器包括数据保护电路系统,所述数据保护电路系统用以:响应于所述多个存储器装置具有对应于第一输入/输出(I/O)宽度的第一操作模式而适应数个码字的第一码字配置;及响应于所述多个存储器装置具有对应于第二I/O宽度的第二操作模式而适应所述数个码字的第二码字配置;以及在所述多个存储器装置的所述第一操作模式与所述多个存储器装置的所述第二操作模式之间切换。

技术研发人员:M·斯福尔津,P·阿马托

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!