存储器装置和操作其的方法与流程

以下描述涉及具有存储器中计算(imc)的存储器装置。

背景技术:

1、也称为乘法-累加(mac)运算的向量-矩阵乘法运算可以是各种技术领域中的应用的性能的核心。例如,可执行mac运算以用于多层神经网络的机器学习和认证。输入信号可被认为形成输入向量,并且可以是例如要由神经网络处理的图像、字节流或其他数据集的数据。例如,可将输入信号乘以神经网络的输入层的权重,并且可从累加的mac运算结果获得输出向量。输出向量可被提供作为神经网络的后续层的输入向量。可在一系列层中迭代地执行mac运算,并且可因此主要通过mac运算的性能来确定神经网络的处理性能。mac运算可通过存储器中计算(imc)来实现。

技术实现思路

1、提供本

技术实现要素:

以简化的形式介绍在下面的具体实施方式中进一步描述的构思的选择。本发明内容不意在标识所要求保护的主题的关键特征或必要特征,也不意在用于帮助确定要求保护的主题的范围。

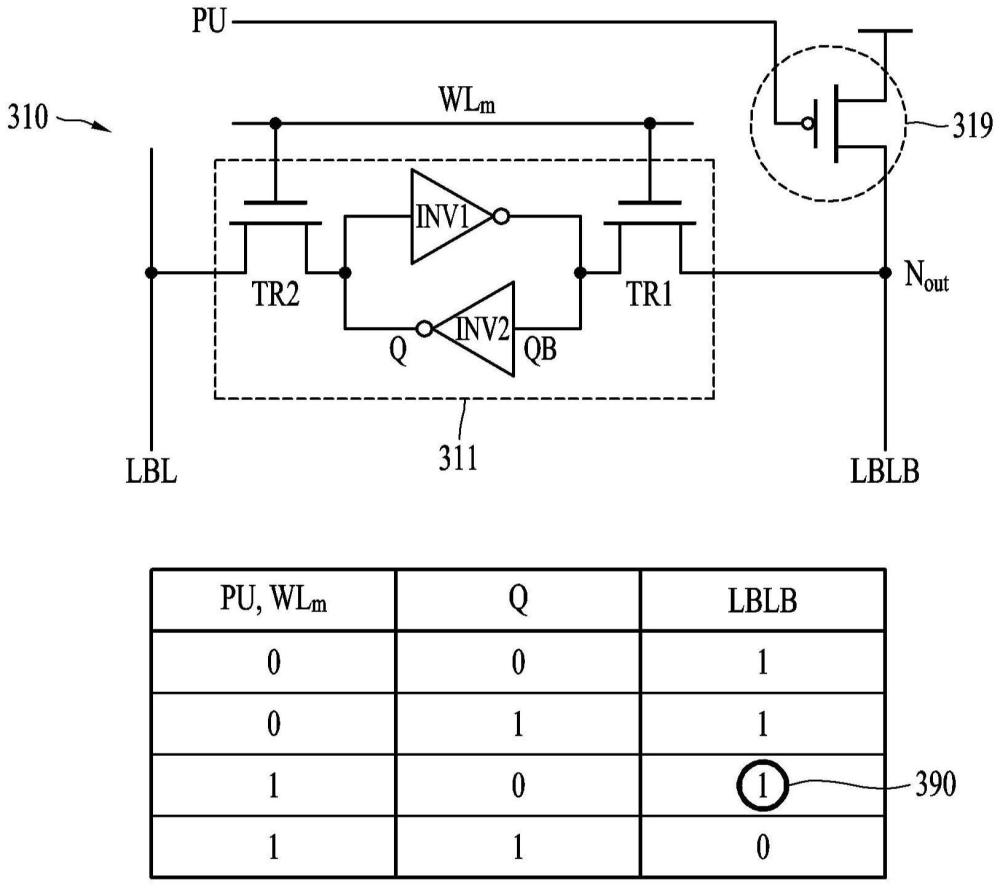

2、在一个总体方面,一种存储器装置包括:乘法单元,包括:存储器单元,包括一对反相器,所述一对反相器包括第一反相器和第二反相器,每个反相器包括输入和输出,其中,第一反相器的输入在所述一对反相器的第一端处连接到第二反相器的输出,并且其中,第一反相器的输出在所述一对反相器的第二端处连接到第二反相器的输入,第一晶体管,连接到所述一对反相器的第一端,以及第二晶体管,连接到所述一对反相器的第二端,值被存储在所述一对反相器的第二端;以及开关元件,连接到存储器单元的输出端,开关元件被配置为响应于输入值而执行开关,并且输出与输入值和存储的所述值之间的乘法结果对应的信号。

3、开关元件可被配置为当连接在电源电压与存储器单元的输出端之间时:响应于1的逻辑值被接收作为输入值而被截止;并且响应于0的逻辑值被接收作为输入值而被导通。

4、开关元件可被配置为上拉晶体管,上拉晶体管被配置为在栅极端子处接收输入值。

5、第一晶体管和第二晶体管可各自是n型金属氧化物半导体(nmos)晶体管,并且其中,上拉晶体管是p型金属氧化物半导体(pmos)晶体管。

6、所述存储器装置可被配置为:从第一操作和第二操作之间选择一个操作并执行选择的操作,其中,第一操作可包括:响应于在一系列乘法运算中的一些乘法运算中通过字线施加小于电源电压的电压,将上拉晶体管的输出端处的电压驱动到电源电压,并且每次根据供应给所述存储器装置的输入来输出乘法运算结果,并且第二操作可包括:在每个乘法运算的预充电阶段中将上拉晶体管的输出端处的电压驱动到电源电压,并且在评估阶段中执行乘法运算。

7、所述存储器装置还可配置为:基于所述存储器装置的操作频率或泄漏,从第一操作和第二操作之间选择所述一个操作。

8、所述存储器装置还可包括:加法器,连接到乘法单元的输出端并被配置为将从乘法单元输出的信号的翻转值进行相加。

9、所述存储器装置还可包括:全局位线和开关,用于通过访问乘法单元的存储器单元来对存储器单元的权重进行读取操作或写入操作。

10、乘法单元可包括:连接到相同上拉晶体管的多个存储器单元。

11、所述存储器装置还可包括:输入/字线驱动器,被配置为:从存储器单元之中选择要用于目标乘法运算的存储器单元。

12、输入/字线驱动器可包括:解码电路,被配置为:从输入信号和从指定要用于目标乘法运算的存储器单元的信号解码出提供给乘法单元的输入值。

13、所述存储器装置还可被配置为:激活连接到包括在一个乘法单元中的存储器单元之中的存储对应于目标运算的值的存储器单元的字线,并且将连接到存储器单元之中的除了激活的字线的存储器单元之外的存储器单元的字线去激活。

14、所述存储器装置还可被配置为:针对多个运算之中的第一运算从存储器单元之中选择第一存储器单元,并且通过所述同一上拉晶体管输出对应于乘法结果的信号;并且针对所述多个运算之中的第二运算从存储器单元之中选择第二存储器单元,并且通过所述同一上拉晶体管输出对应于乘法结果的信号。

15、所述存储器装置还可包括:乘法单元,包括乘法单元,并且可被配置为:在乘法单元中的每个中与其他乘法单元并行地执行乘法运算;并且在所述同一加法器中将所述多个乘法单元之中的与同一列线连接的乘法单元的输出进行相加。

16、乘法单元可连接到一对本地位线,其中,包括在乘法单元中的存储器单元之中的第一存储器单元可连接到第一本地位线,并且所述多个存储器单元之中的第二存储器单元可连接到第二本地位线。

17、第一存储器单元可连接到第一本地位线并且可具有与神经网络的权重对应的值,并且连接到第二本地位线的第二存储器单元可具有权重的翻转值。

18、所述存储器装置还可包括:累加器,存储被配置为将乘法单元的乘法结果进行相加的加法器的输出,并将相加的结果进行累加。

19、所述存储器装置还可包括:输出寄存器,被配置为:存储从累加器输出的最终乘法运算结果。

20、所述存储器装置还可被配置为:当接收到对应于单个位或多个位的最后位的输入信号时,将输入信号的累加器运算结果存储在输出寄存器中。

21、所述存储器装置还可包括:存储控制器,被配置为:控制乘法单元、输入/字线驱动器、读取/写入电路、加法器、累加器和输出寄存器。

22、所述存储器装置还可被配置为:响应于已经过去预设时段或者在每个乘法单元中执行使用另一存储器单元的乘法运算,对上拉晶体管的输出端执行用于预充电的操作。

23、在一个总体方面,一种操作存储器装置的方法包括:由存储器单元通过字线接收输入值,存储器单元包括两个反相器和两个晶体管,所述两个反相器在相对于彼此相反的方向上彼此连接,所述两个晶体管连接到所述两个反相器的两端;由连接到存储器单元的输出端的上拉晶体管在栅极端子处接收输入值;以及从上拉晶体管的输出端输出与输入值和存储在存储器单元中的权重之间的乘法结果对应的信号。

24、在一个总体方面,一种存储器装置包括:上拉晶体管,具有栅极并连接到输出线;以及存储器单元,包括一对反相器和单元晶体管,所述一对反相器在相反方向上的它们的相应端处彼此连接,使得所述一对反相器具有第一端和第二端,单元晶体管具有栅极并且连接到所述一对反相器的第一端和输出线;并且响应于具有相同逻辑值的输入被施加到上拉晶体管的栅极和单元晶体管的栅极,被配置为向输出线输出与所述输入和存储在存储器单元中的二进制值之间的二进制乘法结果对应的逻辑值。

25、对应于二进制乘法结果的逻辑值可以是与非结果。

26、上拉晶体管可以是p型金属氧化物半导体(pmos)晶体管,并且单元晶体管可以是n型金属氧化物半导体(nmos)晶体管。

27、乘法结果可每个时钟周期被输出。

28、乘法结果可仅每两个时钟周期被输出。

29、单元晶体管可以是第一单元晶体管,并且存储器单元还可包括:第二单元晶体管,具有栅极并连接到所述一对反相器的第二端,其中,具有所述相同逻辑值的输入被施加到第二单元晶体管的栅极。

30、输出线可以是还包括第二输出线的第一输出线。

31、单元晶体管可以是第一单元晶体管,并且存储器单元还可包括第二单元晶体管,第二单元晶体管具有栅极并连接到所述一对反相器的另一端和第二输出线。

32、上拉晶体管可以是第一上拉晶体管,并且所述存储器装置还可包括连接到第二输出线的第二上拉晶体管。

33、存储器单元可以是连接到第一输出线和第二输出线的多个存储器单元中的一个。

34、存储器单元可以是连接到输出线的多个存储器单元中的一个。

35、根据以下具体实施方式、附图和权利要求,其他特征和方面将是清楚的。

- 还没有人留言评论。精彩留言会获得点赞!