基于PSE效应的器件漏电流模型及其提取方法与流程

本发明涉及半导体集成电路制造领域,特别是涉及一种基于pse效应的器件漏电流模型及其提取方法。

背景技术:

1、集成电路向着小型化、集约化、高集成度、低压低功耗低成本的趋势发展,低功耗设计成为电路设计的重要指标。而随着工艺节点的缩小,静态漏电在芯片整体功耗中所占比重越来越大。因此,准确全面的表征器件漏电特性至关重要。

2、mosfet中引发静态功耗的泄漏电流主要有:源到漏的亚阈泄漏电流,栅泄漏电流,发生在栅漏交叠区的栅致漏极泄漏(gidl)电流。在这些电流中,当电路中器件处于关闭或者等待状态时,gidl电流在泄露电流中占主导地位。因此,准确全面的表征gidl漏电流模型对于高性能静态功耗的设计场景具有重要意义。

3、随着器件特征尺寸的不断减小,先进工艺中器件布局越来越密集,版图布局复杂度不断提升,这些都导致器件周围的环境对器件自身的电学特性影响越来越大,即版图依赖效应(lde效应)。为了保证器件版图布局的一致性,器件周围往往会有dummy器件,多晶硅栅(poly)周围会有伪栅(dummy poly)。而伪栅与器件沟道的不同距离会导致栅间距效应(pse效应),即注入的离子在光阻材料上发生了散射,散射离子进入到沟道,影响到边缘区域的掺杂浓度,进而对器件的阈值电压、迁移率都有影响。距离器件沟道的不同距离的伪栅对gidl漏电流大小有着明显的规律性影响。然而,目前现有的gidl漏电流模型并没有关于pse效应的表征。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种基于pse效应的器件漏电流模型及其提取方法,用于解决现有的gidl漏电流模型对于gidl漏电流的表征不准确的问题。

2、为实现上述目的及其他相关目的,本发明提供一种基于pse效应的器件漏电流模型,器件漏电流模型用于仿真半导体器件的漏电流;

3、所述器件漏电流模型的漏电流包括主函数及辅函数,且所述主函数与所述辅函数相乘;

4、其中,所述器件漏电流模型的主函数是根据所述半导体器件的沟道区宽度、沟道区长度、栅源电压及工作温度而确定的gidl漏电流函数,所述辅函数是根据伪栅与所述半导体器件的沟道区之间的距离而确定的函数,且所述伪栅设于所述半导体器件的两侧,并与所述半导体器件的栅极平行。

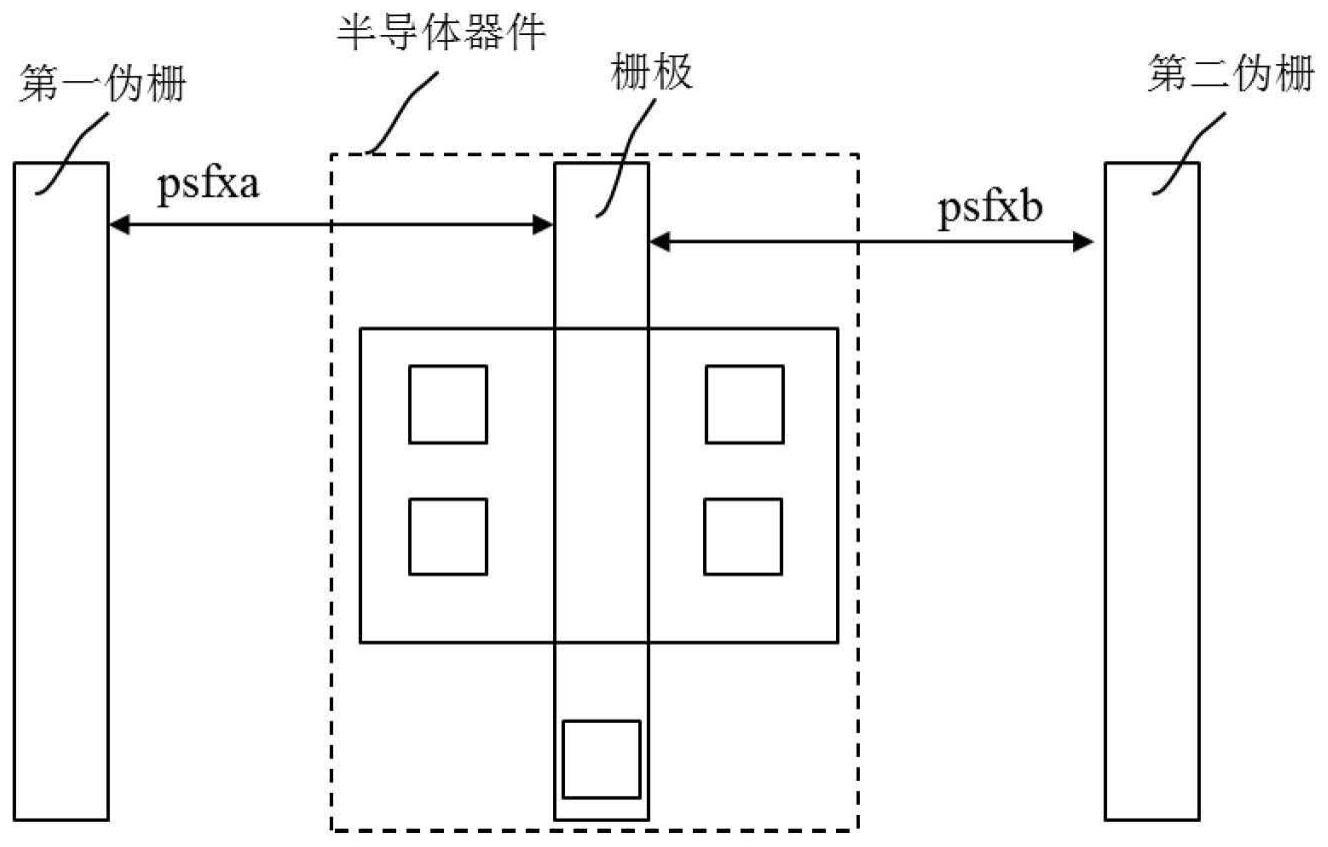

5、可选地,所述辅函数的参数包括第一距离及第二距离,其中,所述第一距离为第一伪栅与所述半导体器件的沟道区之间的距离,所述第二距离为第二伪栅与所述半导体器件的沟道区之间的距离,且所述第一伪栅与所述第二伪栅分别位于所述半导体器件的两侧。

6、可选地,所述辅函数的参数还包括所述沟道区长度及所述沟道区宽度。

7、可选地,所述辅函数的公式为:

8、

9、其中,pwr()表示幂函数;psfxa表示所述第一距离;psfxb表示所述第二距离;w表示所述沟道区宽度;l表示所述沟道区长度;α、β、γ1、a1、b1、c1、d1、b1、c1、d1均为拟合系数。

10、可选地,通过改变所述第一距离及所述第二距离中的至少一个,对所述器件漏电流模型形成的漏电流曲线和实际测量的漏电流曲线进行拟合而得到所述拟合系数。

11、可选地,所述器件漏电流模型的漏电流的公式为:

12、idoff=f(w,l,vgs,t)*f(psfxa,psfxb)

13、其中,idoff表示所述漏电流,f(w,l,vgs,t)为所述主函数的公式,w表示所述沟道区宽度,l表示所述沟道区长度,vgs表示所述栅源电压,t表示所述工作温度。

14、相应的,本发明还提供一种基于pse效应的器件漏电流模型的提取方法,所述方法包括:

15、建立所述半导体器件的漏电流模型,其中,所述漏电流模型的漏电流包括主函数与辅函数,且所述主函数与所述辅函数相乘,所述辅函数根据伪栅与所述半导体器件的沟道区之间的距离来确定,且所述伪栅设于所述半导体器件的两侧,并与所述半导体器件的栅极平行;

16、根据不受所述伪栅影响的所述半导体器件对所述主函数进行系数拟合;

17、通过改变所述伪栅与所述半导体器件的沟道区之间的距离来进行拟合以得到所述辅函数的拟合系数。

18、可选地,所述辅函数的参数包括第一距离及第二距离,其中,所述第一距离为第一伪栅与所述半导体器件的沟道区之间的距离,所述第二距离为第二伪栅与所述半导体器件的沟道区之间的距离,且所述第一伪栅与所述第二伪栅分别设于所述半导体器件的两侧。

19、可选地,通过改变所述伪栅与所述半导体器件的沟道区之间的距离来进行拟合以得到所述辅函数的拟合系数的方法:

20、改变所述第一距离或所述第二距离中的至少一个,对所述半导体器件漏电流模型形成的漏电流曲线和实际测量的漏电流曲线进行拟合以得到所述拟合系数。

21、可选地,所述辅函数的参数还包括所述沟道区长度及所述沟道区宽度。

22、可选地,所述辅函数的公式为:

23、

24、其中,pwr()表示幂函数;psfxa表示所述第一距离;psfxb表示所述第二距离;w表示所述沟道区宽度;l表示所述沟道区长度;α、β、γ1、a1、b1、c1、d1、b1、c1、d1均为拟合系数。

25、可选地,所述器件漏电流模型的漏电流的公式为:

26、idoff=f(w,l,vgs,t)*f(psfxa,psfxb)

27、其中,idoff表示所述漏电流,f(w,l,vgs,t)为所述主函数的公式,w表示所述沟道区宽度,l表示所述沟道区长度,vgs表示所述栅源电压,t表示所述工作温度。

28、如上所述,本发明的基于pse效应的器件漏电流模型及其提取方法,为了测试出伪栅与器件沟道区之间的距离的变化(也就是pse效应)对器件漏电流的影响,首先会增加设计与之相关的测试版图。在增加的设计版图里,要注意包括下面几点:1、画与半导体器件沟道区不同距离的第一伪栅及第二伪栅;2、固定第一伪栅与沟道区之间的第一距离,改变第二伪栅与沟道区之间的第二距离;或固定第二伪栅与沟道区之间的第二距离,改变第一伪栅与沟道区之间的第一距离。然后,对根据设计版图制备的测试芯片进行测量,并对获取的测量数据进行分析,对于常规的器件漏电流模型拟合好后,开始调整与第一距离及第二距离相关的系数,这样就可以得到完整的与第一距离及第二距离相关的漏电流模型。设计者通过仿真模型去了解器件在伪栅与器件沟道区之间距离不同时的性能情况,使电路仿真结果更准确。

技术特征:

1.一种基于pse效应的器件漏电流模型,其特征在于,器件漏电流模型用于仿真半导体器件的漏电流;

2.根据权利要求1所述的基于pse效应的漏电流模型,其特征在于,所述辅函数的参数包括第一距离及第二距离,其中,所述第一距离为第一伪栅与所述半导体器件的沟道区之间的距离,所述第二距离为第二伪栅与所述半导体器件的沟道区之间的距离,且所述第一伪栅与所述第二伪栅分别位于所述半导体器件的两侧。

3.根据权利要求2所述的基于pse效应的漏电流模型,其特征在于,所述辅函数的参数还包括所述沟道区长度及所述沟道区宽度。

4.根据权利要求3所述的基于pse效应的漏电流模型,其特征在于,所述辅函数的公式为:

5.根据权利要求4所述的基于pse效应的漏电流模型,其特征在于,通过改变所述第一距离及所述第二距离中的至少一个,对所述器件漏电流模型形成的漏电流曲线和实际测量的漏电流曲线进行拟合而得到所述拟合系数。

6.根据权利要求5所述的基于pse效应的漏电流模型,其特征在于,所述器件漏电流模型的漏电流的公式为:

7.一种基于pse效应的器件漏电流模型的提取方法,其特征在于,所述方法包括:

8.根据权利要求7所述的基于pse效应的器件漏电流模型的提取方法,其特征在于,所述辅函数的参数包括第一距离及第二距离,其中,所述第一距离为第一伪栅与所述半导体器件的沟道区之间的距离,所述第二距离为第二伪栅与所述半导体器件的沟道区之间的距离,且所述第一伪栅与所述第二伪栅分别设于所述半导体器件的两侧。

9.根据权利要求8所述的基于pse效应的器件漏电流模型的提取方法,其特征在于,通过改变所述伪栅与所述半导体器件的沟道区之间的距离来进行拟合以得到所述辅函数的拟合系数的方法:

10.根据权利要求9所述的基于pse效应的器件漏电流模型的提取方法,其特征在于,所述辅函数的参数还包括所述沟道区长度及所述沟道区宽度。

11.根据权利要求10所述的基于pse效应的器件漏电流模型的提取方法,其特征在于,所述辅函数的公式为:

12.根据权利要求11所述的基于pse效应的器件漏电流模型的提取方法,其特征在于,所述器件漏电流模型的漏电流的公式为:

技术总结

本发明提供一种基于PSE效应的器件漏电流模型,器件漏电流模型用于仿真半导体器件的漏电流;所述器件漏电流模型的漏电流包括主函数及辅函数,且所述主函数与所述辅函数相乘;其中,所述器件漏电流模型的主函数是根据所述半导体器件的沟道区宽度、沟道区长度、栅源电压及工作温度而确定的GIDL漏电流函数,所述辅函数是根据伪栅与所述半导体器件的沟道区之间的距离而确定的函数,且所述伪栅设于所述半导体器件的两侧,并与所述半导体器件的栅极平行。通过本发明解决了现有的GIDL漏电流模型对于GIDL漏电流的表征不准确的问题。

技术研发人员:王晴雯,吴园园,张瑜

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!