一种数据清除系统及方法与流程

本发明涉及异步fifo,尤其涉及一种应用于异步先入先出的数据缓存器的数据清除系统及方法。

背景技术:

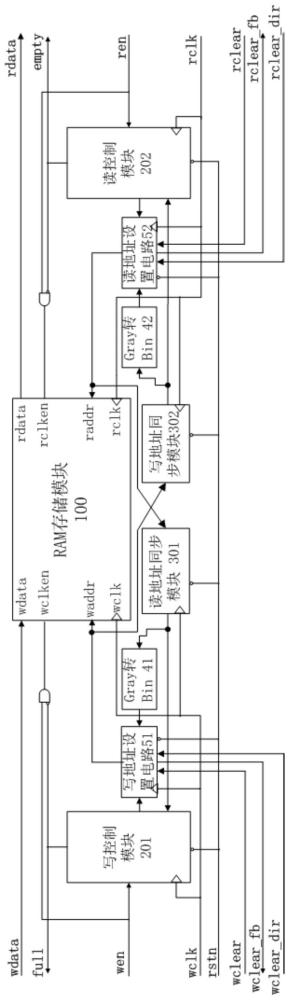

1、在现场可编程门阵列(field-programmable gate array,fpga)或专用集成电路(application specific integrated circuit,asic)设计中,先入先出(first in firstout,fifo)存储器常被用作数据缓冲或数据跨时钟同步的部件。fifo可以根据其读/写时钟的来源,被分为同步fifo和异步fifo。同步fifo的读/写时钟使用同一时钟源,而异步fifo的读/写时钟为不同的时钟源。异步fifo结构如图1所示,主要由双口ram存储模块、读/写控制模块及地址同步模块组成。而同步fifo由于其读/写时钟位于同一时钟域,因此不需要地址同步电路。

2、在某些应用场景下,fifo需要清除内部的数据,例如当fifo中被写入了无效数据,或者fifo的读取端未能及时完成数据读取。这种情况下,通常使用fifo的复位信号来清除其内部的数据。fifo通过空满信号来指示其内部的数据存储情况,当fifo中没有数据时,空信号就会有效。

3、然而,对于异步fifo,由于其读/写指针位于两个不同的时钟域内,因此在使用复位功能时存在一定的不便。为了解决这个问题,fifo通常会引出一个复位信号,通过这个复位信号可以同时复位读/写控制模块,如图2所示,为xilinx公司的fifo框图。然而,这样的复位信号只能来自读/写时钟域中的其中一个,对于另一个时钟域来说,这个复位信号是异步信号,直接用于复位可能会造成亚稳态。因此,fifo内部会对这个复位信号进行处理,xilinx公司的fifo复位时序如图3所示,通过将其分别同步至两个时钟域内,之后在两个时钟域内分别生效完成对fifo的复位。然而,这个过程需要保持读/写时钟的有效性,且在复位完成后仍需要等待一段时间才能进行读/写操作,这在某些情况下可能会影响fifo的使用效率。

技术实现思路

1、为了解决以上技术问题,本发明提供了一种应用于异步先入先出的数据缓存器的数据清除系统及方法。

2、本发明所解决的技术问题可以采用以下技术方案实现:

3、一种数据清除系统,应用于一异步先入先出的数据缓存器,包括:

4、清除信号接口,用于接收一清除信号;其中,所述清除信号位于第一时钟域,未接收到所述清除信号的时钟域为第二时钟域;

5、判断模块,连接所述清除信号接口,用于在接收到所述清除信号时判断所述第二时钟域的时钟信号是否有效;

6、地址设置模块,连接所述判断模块,用于在所述第二时钟域的时钟信号有效时,对所述第一时钟域的指针信号进行处理,直至与所述第二时钟域的指针信号相同;以及在所述第二时钟域的时钟信号无效时,将所述第一时钟域的地址信号同步为与所述第二时钟域的地址信号相同,以使所述第一时钟域的指针信号与所述第二时钟域的指针信号同步。

7、优选地,所述地址设置模块还用于在对所述第一时钟域的指针信号进行处理的同时,输出一用以指示清除状态的清除反馈信号。

8、优选地,所述第一时钟域为写时钟域,所述第二时钟域为读时钟域;

9、所述地址设置模块包括:

10、写地址设置电路,用于在所述读时钟域的读时钟信号有效时,对所述写时钟域的写指针信号以一预设步进递减处理,直至与所述读时钟域的读指针信号相同;以及在所述读时钟信号无效时,将所述写时钟域的写地址信号同步为与所述读时钟域的读地址信号相同,以使所述写指针信号与所述读指针信号同步。

11、优选地,所述写地址设置电路包括:

12、第一等号逻辑器,所述第一等号逻辑器的第一端连接所述读指针信号,所述第一等号逻辑器的第二端连接所述写地址信号;

13、第一触发器,所述第一触发器的输入端连接自身输出端,所述第一触发器的时钟端连接写时钟信号,所述第一触发器的清零端连接所述第一等号逻辑器的输出端,所述第一触发器的预置端连接所述清除信号,所述第一触发器的输出端输出的信号作为清除反馈信号;

14、第一与门,所述第一与门的第一输入端通过一第一反相器连接所述第一等号逻辑器的输出端,所述第一与门的第二输入端连接所述第一触发器的输出端,所述第一与门的输出端连接一补码计算器;

15、第一选择器,所述第一选择器的输入端分别连接写时钟使能信号和所述补码计算器的输出端,所述第一选择器的控制端连接所述第一触发器的输出端;

16、第一加法器,所述第一加法器的输入端分别连接所述第一选择器的输出端和所述写地址信号;

17、第二选择器,所述第二选择器的输入端分别连接所述第一加法器的输出端和所述读指针信号,所述第二选择器的控制端连接一地址清除信号;

18、第二触发器,所述第二触发器的输入端连接所述第二选择器的输出,所述第二触发器的时钟输入端连接所述写时钟信号,所述第二触发器的输出端用于输出所述写地址信号。

19、优选地,所述第一时钟域为读时钟域,所述第二时钟域为写时钟域;

20、所述地址设置模块包括:

21、读地址设置电路,用于在所述写时钟域的写时钟信号有效时,对所述读时钟域的读指针信号以一预设步进递增处理,直至与所述写时钟域的写指针信号相同;以及在所述写时钟信号无效时,将所述读时钟域的读地址信号同步为与所述写时钟域的写地址信号相同,以使所述写指针信号与所述读指针信号同步。

22、优选地,所述读地址设置电路包括:

23、第三触发器,所述第三触发器的输入端连接所述写指针信号,所述第三触发器的时钟端连接读时钟信号,所述第三触发器的使能端连接所述清除信号;

24、第二等号逻辑器,所述第二等号逻辑器的第一端连接所述第三触发器的输出端,所述第二等号逻辑器的第二端连接所述读地址信号;

25、第四触发器,所述第四触发器的输入端连接自身输出端,所述第四触发器的时钟端连接所述读时钟信号,所述第四触发器的清零端连接所述第二等号逻辑器的输出端,所述第四触发器的预置端连接所述清除信号,所述第四触发器的输出端输出的信号作为清除反馈信号;

26、第二与门,所述第二与门的第一输入端通过一第二反相器连接所述第二等号逻辑器的输出端,所述第二与门的第二输入端连接所述第四触发器的输出端;

27、或门,所述或门的输入端分别连接读时钟使能信号和所述第二与门的输出端;

28、第二加法器,所述第二加法器的输入端分别连接所述或门的输出端和所述读地址信号;

29、第三选择器,所述第三选择器的输入端分别连接所述第二加法器的输出端和所述写指针信号,所述第三选择器的控制端连接一地址清除信号;

30、第五触发器,所述第五触发器的输入端连接所述第三选择器的输出,所述第五触发器的时钟输入端连接所述读时钟信号,所述第五触发器的输出端用于输出所述读地址信号。

31、优选地,所述写指针信号以格雷码转二进制码形式输出;

32、所述读指针信号以格雷码转二进制码形式输出。

33、优选地,所述清除信号为单周期的脉冲信号。

34、优选地,所述数据缓存器包括ram存储模块、写控制模块和读控制模块、读地址同步模块和写地址同步模块;

35、所述ram存储模块的写数据端口连接写数据信号,写时钟使能端口连接写时钟使能信号,写地址端口连接写地址信号,写时钟端口连接写时钟信号,读数据端口连接读数据信号,读时钟使能端口连接读时钟使能信号,读地址端口连接读地址信号,读时钟端口连接读时钟信号;

36、所述写控制模块的写时钟端口连接所述写时钟信号,写使能端口连接写使能信号,写复位端口连接复位信号,读地址同步端口连接所述读地址同步模块的输出,写地址输出端口连接所述写地址设置电路,满信号输出端口用于输出满指示信号;

37、所述读地址同步模块的输入连接所述读地址信号,读同步时钟端连接所述写时钟信号,读同步复位端口连接所述复位信号;

38、所述读控制模块的读时钟端口连接所述读时钟信号,读使能端口连接读使能信号,读复位端口连接所述复位信号,写地址同步端口连接所述写地址同步模块的输出,读地址输出端口连接所述读地址设置电路,空信号输出端口用于输出空指示信号;

39、所述写地址同步模块的输入连接所述写地址信号,写同步时钟端连接所述读时钟信号,写同步复位端口连接所述复位信号。

40、本发明还提供一种数据清除方法,应用于如上述的数据清除系统,包括:

41、接收一清除信号;其中,所述清除信号位于第一时钟域,未接收到所述清除信号的时钟域为第二时钟域;

42、在接收到所述清除信号时判断所述第二时钟域的时钟信号是否有效;

43、在所述第二时钟域的时钟信号有效时,对所述第一时钟域的指针信号进行处理,直至与所述第二时钟域的指针信号相同;以及

44、在所述第二时钟域的时钟信号无效时,将所述第一时钟域的地址信号同步为与所述第二时钟域的地址信号相同,以使所述第一时钟域的指针信号与所述第二时钟域的指针信号同步。

45、本发明技术方案的优点或有益效果在于:

46、本发明通过在传统fifo的基础上增加了独立的清除信号接口,能够实现对fifo中存储内容的清除,且清除信号来自读/写时钟域中的其中一个,保证在清除时即使另一个时钟信号失效,清除操作也可以正常进行,拓展了fifo的使用范围。

- 还没有人留言评论。精彩留言会获得点赞!