基于强化学习的芯片版图设计方法、系统、装置与介质

本技术涉及集成电路,尤其是一种基于强化学习的芯片版图设计方法、系统、装置与存储介质。

背景技术:

1、现有技术中,芯片布局放置主要可以分为三类:基于分区的方法、基于随机的方法与基于优化的方法。基于分区的方法如其名,依照递归的思想,将芯片画布分为一个个区域,将大芯片画布的放置问题转化为小芯片画布上的放置问题,从而降低整体放置的复杂度。但是分区的方法往往很难考虑全局放置的质量,低质量早期分区会导致低质量全局放置解,很难扩展到现代大规模集成电路放置中。

2、基于随机的方法主要是由爬山算法兴起,进而发展到拥有跳出局部最优解能力的模拟退火算法,并成为基于随机算法的主流。模拟退火算法借鉴了冶金中的退火思想,旨在临时选择一个更差的解,以此跳出局部最优解。基于随机的方法在小规模电路方面实现了不错的效果,但由于其时间成本太过庞大,无法作用于大规模的电路。

3、基于优化的方法由近代提出,主要是将放置问题转化为一个优化问题,寻找多个目标中的一个加权最优解。例如google在标准单元放置中所使用的力导向算法,将电路器件之间建模为类弹簧系统,通过引力与斥力寻找器件之间的最佳距离。eplace,replace等方法与之类似,将电路系统建模为静电系统。这些方法大多基于cpus,计算的时间成本较高。dreamplace将电路系统建模为静电系统,同时基于深度学习框架pytorch使用gpu对放置过程进行加速,与前两种方法相比,在不降低放置性能的情况下实现了大幅加速。因此,相关技术中仍存在需要解决的技术问题。

技术实现思路

1、本技术的目的在于至少一定程度上解决现有技术中存在的技术问题之一。

2、为此,本技术实施例的一个目的在于提供一种基于强化学习的芯片版图设计方法、系统、装置与存储介质,该方法可以节约时间成本。

3、为了达到上述技术目的,本技术实施例所采取的技术方案包括:一种基于强化学习的芯片版图设计方法,包括:获取芯片画布的第一状态以及芯片画布需要布局的器件数量;将所述第一状态输入强化学习布局模型,得到第二状态、第一布局动作以及第一全局布线长度以及第一拥塞和密度的加权和;将当前得到的所述第二状态作为新的第一状态,并返回将所述第一状态输入强化学习布局模型,得到第二状态、第一布局动作以及第一全局布线长度以及第一拥塞和密度的加权和的步骤,直至所述第一布局动作的数量与所述器件数量相同,得到若干个布局动作、若干个第一全局布线长度以及若干个第一拥塞和密度的加权和;根据所述若干个布局动作、若干个第一全局布线长度以及若干个第一拥塞和密度的加权和,确定芯片版图。

4、另外,根据本发明中上述实施例的一种基于强化学习的芯片版图设计的方法,还可以有以下附加的技术特征:

5、进一步地,本技术实施例中,所述强化学习布局模型包括第一通道、第二通道、第三通道,第四通道、第五通道以及第六通道;所述第一通道以及所述第二通道用于生成版图被占用的结果;所述第三通道用于生成版图布局轨迹;第四通道用于生成当前要布局的器件的长度,所述第五通道用于生成当前要布局的器件的宽度,所述第六通道用于生成当前器件的编号。

6、进一步地,本技术实施例中,所述强化学习布局模型包括策略网络以及环境,所述将所述第一状态输入强化学习布局模型,得到第二状态、第一布局动作以及第一全局布线长度以及第一拥塞和密度的加权和这一步骤,具体包括:将所述第一状态送入强化学习的策略网络,得到第一动作;将所述第一状态和所述第一动作送入到所述环境,所述环境根据所述第一动作,对所述第一状态进行更改,得到第二状态并生成第一全局布线长度以及第一拥塞和密度的加权和。

7、进一步地,本技术实施例中,所述将所述第一状态和所述第一动作送入到所述环境,生成第一全局布线长度以及第一拥塞和密度的加权和这一步骤,具体包括:获取每个器件在连接线网时的节点数据;根据所述节点数据,确定第一全局布线长度以及第一拥塞和密度的加权和。

8、进一步地,本技术实施例中,所述根据所述节点数据,确定第一全局布线长度以及第一拥塞和密度的加权和这一步骤,具体包括:

9、将所述节点数据输入至计算公式,得到第一全局布线长度以及第一拥塞和密度的加权和;

10、所述计算公式包括:

11、

12、s.t.congestion(mx,my,mw,mh)≤cth and overlap(mx,my,mw,mh)=0,

13、其中p(i,j)为节点数据,x为x轴中的数据,y为y轴中的数据,conge stion(mx,my,mw,mh)为拥塞参数,cth为预设的参数,overlap(mx,my,mw,mh)为重叠参数。

14、进一步地,本技术实施例中,所述策略网络包括第一层网络、第二层网络、第三层网络、第四层网络以及全连接层,所述将所述第一状态送入强化学习的策略网络,得到第一动作这一步骤,具体包括:将所述第一状态送入所述四层网络,得到256x256x6的第一张量;将所述第一张量输入所述全连接层,得到256x256x1的第二张量;所述第二张量用于表征若干个动作策略;以动作概率最大的动作策略为第一动作。

15、进一步地,本技术实施例中,所述策略网络包括第一层网络、第二层网络、第三层网络、第四层网络以及全连接层,所述将所述第一状态送入强化学习的策略网络,得到第一动作这一步骤,具体包括:将所述第一状态送入所述四层网络,得到256x256x6的第一张量;将所述第一张量输入所述全连接层,得到256x256x1的第二张量;所述第二张量用于表征若干个动作策略;以动作概率最大的动作策略为第一动作。

16、进一步地,本技术实施例中,所述第一层网络包括16个卷积核、所述第二层网络包括32个卷积核、所述第三层网络包括64个卷积核、所述第四层网络包括6个卷积核。

17、另一方面,本技术实施例还提供一种基于强化学习的芯片版图设计系统,包括:

18、获取单元,用于获取芯片画布的第一状态;

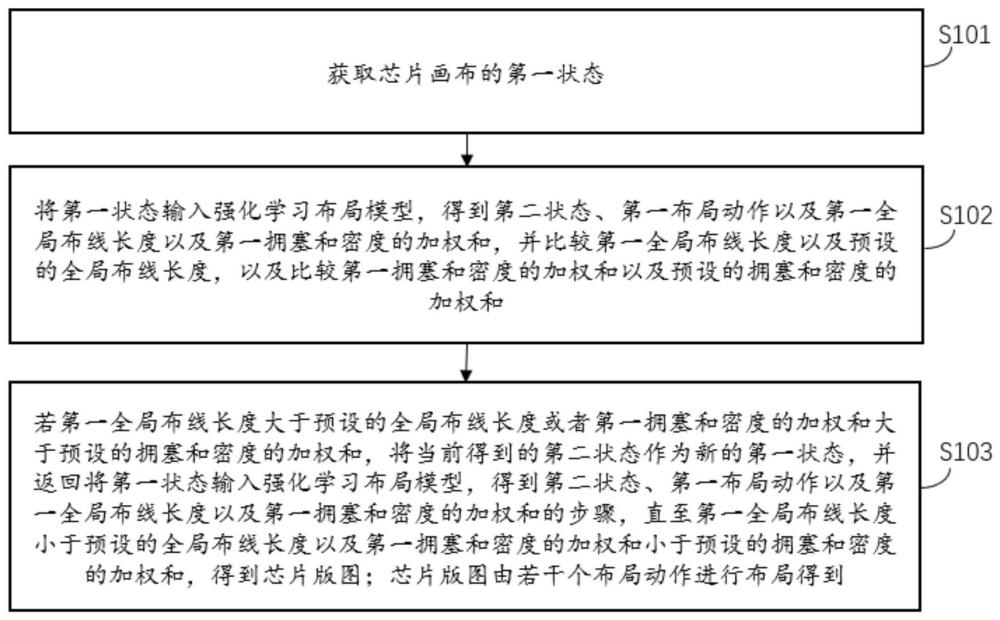

19、第一处理单元,用于将所述第一状态输入强化学习布局模型,得到第二状态、第一布局动作以及第一全局布线长度以及第一拥塞和密度的加权和,并比较第一全局布线长度以及预设的全局布线长度,以及比较第一拥塞和密度的加权和以及预设的拥塞和密度的加权和;

20、第二处理单元,用于若第一全局布线长度大于预设的全局布线长度或者第一拥塞和密度的加权和大于预设的拥塞和密度的加权和,将当前得到的第二状态作为新的第一状态,并返回将所述第一状态输入强化学习布局模型,得到第二状态、第一布局动作以及第一全局布线长度以及第一拥塞和密度的加权和的步骤,直至所述第一全局布线长度小于预设的全局布线长度以及第一拥塞和密度的加权和小于预设的拥塞和密度的加权和,得到芯片版图;所述芯片版图由若干个布局动作进行布局得到。

21、另一方面,本技术还提供一种基于强化学习的芯片版图设计装置,包括:

22、至少一个处理器;

23、至少一个存储器,用于存储至少一个程序;

24、当所述至少一个程序被所述至少一个处理器执行,使得所述至少一个处理器实现如

技术实现要素:

中任一项所述一种基于强化学习的芯片版图设计方法。

25、此外,本技术还提供一种存储介质,其中存储有处理器可执行的指令,所述处理器可执行的指令在由处理器执行时用于执行如上述任一项所述一种基于强化学习的芯片版图设计方法。

26、本技术的优点和有益效果将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到:

27、本技术可以获取芯片画布的第一状态;将第一状态输入强化学习布局模型,得到第二状态、第一布局动作以及第一全局布线长度以及第一拥塞和密度的加权和,并比较第一全局布线长度以及预设的全局布线长度,以及比较第一拥塞和密度的加权和以及预设的拥塞和密度的加权和;若第一全局布线长度大于预设的全局布线长度或者第一拥塞和密度的加权和大于预设的拥塞和密度的加权和,将当前得到的第二状态作为新的第一状态,并返回将第一状态输入强化学习布局模型,得到第二状态、第一布局动作以及第一全局布线长度以及第一拥塞和密度的加权和的步骤,直至第一全局布线长度小于预设的全局布线长度以及第一拥塞和密度的加权和小于预设的拥塞和密度的加权和,得到芯片版图;芯片版图由若干个布局动作进行布局得到,本技术通过强化学习模型快速得到芯片版图布局设计,可以应用于大规模的电路的版图布局设计,可以节约的布局的时间成本。

- 还没有人留言评论。精彩留言会获得点赞!