指令处理方法、处理器核、处理器、计算设备及存储介质与流程

本说明书涉及计算机应用,具体地说,涉及计算机应用下的指令处理技术,更具体地说,涉及一种指令处理方法、处理器核、处理器、计算设备及存储介质。

背景技术:

1、乱序超标量处理器(out-of-order superscalar processor,ooo处理器),是一种高性能的处理器架构,可以在每个时钟周期获取当前pc(program counter,程序计数器)之后的多个指令,并能够在内部并行地一次性乱序执行多条指令,从而最大程度地利用处理器的资源并提高指令级并行度。

2、但目前,乱序超标量处理器中访问延迟是制约整体性能的关键因素之一,有必要提供一种指令处理方法以降低访问延迟,从而提高指令处理效率,改善处理器性能。

技术实现思路

1、本说明书实施例提供了一种指令处理方法、处理器核、处理器、计算设备及存储介质,实现了降低指令处理过程中的访问延迟的目的,从而提高了指令处理效率,改善了处理器性能。

2、为实现上述技术目的,本说明书实施例提供了如下技术方案:

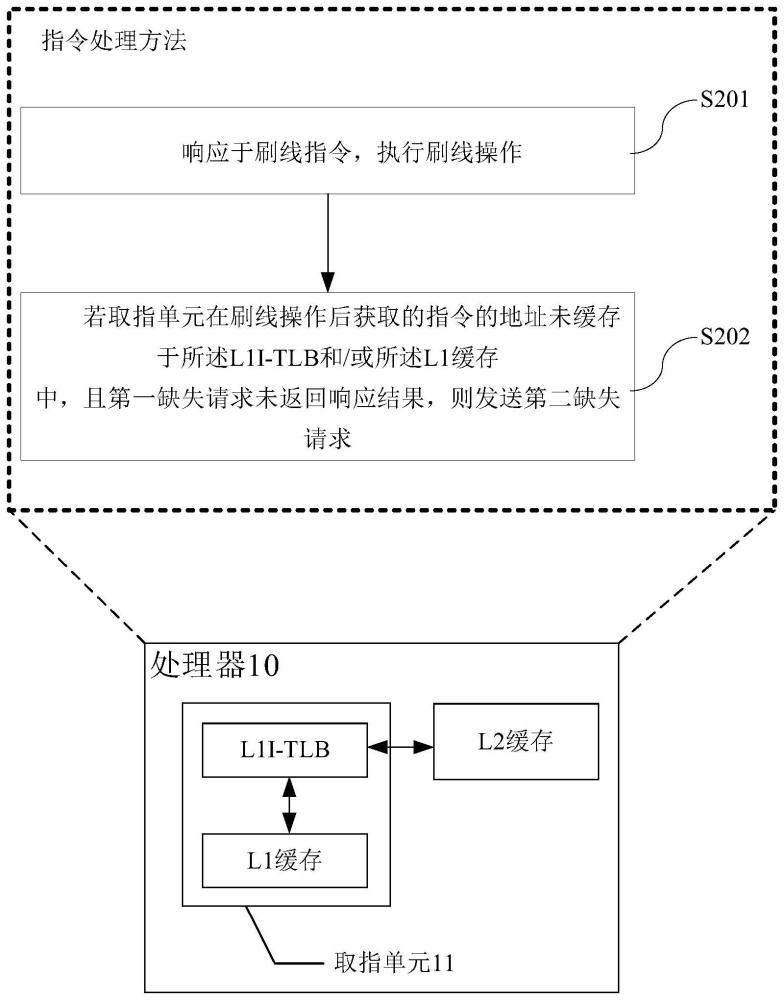

3、第一方面,本说明书的一个实施方式提供一种指令处理方法,应用于处理器,所述处理器包括取指单元、l1缓存和l2缓存,所述取指单元包括一级指令快表l1i-tlb,所述指令处理方法包括:

4、响应于刷线指令,执行刷线操作;

5、若取指单元在刷线操作后获取的指令的地址未缓存于所述l1i-tlb和/或所述l1缓存中,且第一缺失请求未返回响应结果,则发送第二缺失请求;

6、所述第一缺失请求和所述第二缺失请求的身份标识不同;所述第一缺失请求用于请求所述l2缓存返回所述取指单元在刷线操作之前获取的指令的地址;所述第二缺失请求用于请求所述l2缓存返回所述取指单元在刷线操作之后获取的指令的地址。

7、在一个实施方式中,所述l2缓存包括缺失状态处理寄存器mshr;

8、所述第二缺失请求携带有优先返回标识,所述优先返回标识用于指示所述mshr优先处理所述第二缺失请求。

9、在一个实施方式中,所述优先返回标识具体用于指示所述mshr将所述第二缺失请求调序到mshr队列的最前端,所述mshr队列包括多个依序排列的待处理请求。

10、在一个实施方式中,所述第一缺失请求携带有第一页表标识,所述第一页表标识用于标记所述第一缺失请求所请求的指令的地址所在的内存页表;所述第二缺失请求携带有第二页表标识,所述第二页表标识用于标记所述第二缺失请求所请求的指令的地址所在的内存页表;

11、所述发送第二缺失请求之前,还包括:

12、若所述第一页表标识与所述第二页表标识相同,则等待所述第一缺失请求返回响应结果;若所述第一页表标识与所述第二页表标识不同,则进入发送第二缺失请求的步骤。

13、在一个实施方式中,所述发送第二缺失请求之后,还包括:

14、发送携带有目标身份标识的移除请求,所述目标身份标识包括所述第一缺失请求的身份标识,所述移除请求用于指示所述l2缓存将未返回的所述第一缺失请求从mshr队列中移除,所述mshr队列包括多个依序排列的待处理请求。

15、在一个实施方式中,所述指令处理方法还包括:

16、接收所述第二缺失请求的响应结果,根据所述第二缺失请求的响应结果,计算刷线操作后获取的指令的物理地址;所述响应结果携带有与所述第二缺失请求相同的身份标识。

17、在一个实施方式中,所述处理器还包括:内存管理单元;所述内存管理单元与所述l1i-tlb通过交互接口建立有通信连接,所述交互接口具有身份状态标识;每次请求的发送与响应结果的接收均会使所述身份状态标识的取值在第一取值和第二取值之间变化;

18、所述发送第二缺失请求包括:

19、若所述身份状态标识为第一状态,则通过所述交互接口向所述内存管理单元发送携带有第一取值的身份标识的第二缺失请求;

20、若所述身份状态标识为第二状态,则通过所述交互接口向所述内存管理单元发送携带有第二取值的身份标识的第二缺失请求。

21、第二方面,本说明书的一个实施方式提供一种处理器核,包括:取指单元和l1缓存,所述取指单元包括一级指令快表l1i-tlb,其中,所述取指单元被配置为:

22、响应于刷线指令,执行刷线操作,若在刷线操作后获取的指令的地址未缓存于所述l1i-tlb和/或所述l1缓存中,且第一缺失请求未返回结果,则发送第二缺失请求;

23、所述第一缺失请求和所述第二缺失请求的身份标识不同;所述第一缺失请求用于请求l2缓存返回所述取指单元在刷线操作之前获取的指令的地址;所述第二缺失请求用于请求所述l2缓存返回所述取指单元在刷线操作之后获取的指令的地址。

24、第三方面,本说明书的一个实施方式提供一种处理器,包括:l2缓存和至少一个处理器核;所述处理器核包括如上述任一项所述的处理器核。

25、第四方面,本说明书的一个实施方式提供一种指令处理装置,所述指令处理装置包括:

26、刷线单元,用于响应于刷线指令,执行刷线操作;

27、请求单元,用于若取指单元在刷线操作后获取的指令的地址未缓存于所述l1i-tlb和/或所述l1缓存中,且第一缺失请求未返回响应结果,则发送第二缺失请求;

28、所述第一缺失请求和所述第二缺失请求的身份标识不同;所述第一缺失请求用于请求所述l2缓存返回所述取指单元在刷线操作之前获取的指令的地址;所述第二缺失请求用于请求所述l2缓存返回所述取指单元在刷线操作之后获取的指令的地址。

29、第五方面,本说明书的一个实施方式还提供了一种计算设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如上所述的指令处理方法。

30、第六方面,本说明书的一个实施方式还提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上所述的指令处理方法。

31、第七方面,本说明书实施例提供了一种计算机程序产品或计算机程序,所述计算机程序产品包括计算机程序,所述计算机程序存储在计算机可读存储介质中;所述计算机设备的处理器从所述计算机可读存储介质读取所述计算机程序,所述处理器执行所述计算机程序时实现上述的指令处理方法的步骤。

32、从上述技术方案可以看出,本说明书实施例提供的指令处理方法在刷线操作后,取指单元在刷线操作后获取的指令的地址未缓存于所述l1i-tlb和/或所述l1缓存中,且在刷线操作前发送的第一缺失请求的响应结果还未返回的情况下,无需等待第一缺失请求的响应结果返回,即可通过向l2缓存发送身份标识不同的第二缺失请求的方式,请求l2缓存返回新的指令的地址,以尽快获取正确指令的地址。如此,减少了在指令处理过程中等待第一缺失请求的响应结果返回所需的时间,即减少了在刷线操作后发生l1i-tlb未命中和/或l1缓存未命中(即取指单元重新获取的指令的地址未缓存于所述l1i-tlb和/或所述l1缓存中)的情况下的等待时间,从而实现了降低指令处理过程中的访问延迟的目的,提高了指令处理效率,改善了处理器性能。

- 还没有人留言评论。精彩留言会获得点赞!