一种休眠唤醒电路、方法、芯片及电子设备与流程

本发明涉及集成电路,具体是涉及一种休眠唤醒电路、方法、芯片及电子设备。

背景技术:

1、现有的芯片在进入休眠状态时,其内部的电路大部分处于断电状态,而唤醒电路可以正常工作,当有唤醒事件触发时,唤醒电路触发芯片唤醒使芯片恢复正常工作状态。

2、现有的唤醒电路一般采用gpio电平或边沿唤醒,只要芯片连接的外设发送命令(即使不是唤醒命令),或者存在外部干扰信号,芯片也会被唤醒进入正常工作状态,然后检测是否为唤醒命令,如是,则保持正常工作状态,否则恢复休眠状态。芯片在被唤醒后即使检测到不是唤醒命令再进入休眠状态,芯片的平均休眠电流也增大,导致芯片的功耗增加。

技术实现思路

1、本发明的第一目的是提供一种可以降低芯片平均休眠电流的休眠唤醒电路。

2、本发明的第二目的是提供一种包括上述休眠唤醒电路的芯片。

3、本发明的第三目的是提供一种包括上述芯片的电子设备。

4、本发明的第四目的是提供一种可以降低芯片平均休眠电流的休眠唤醒方法。

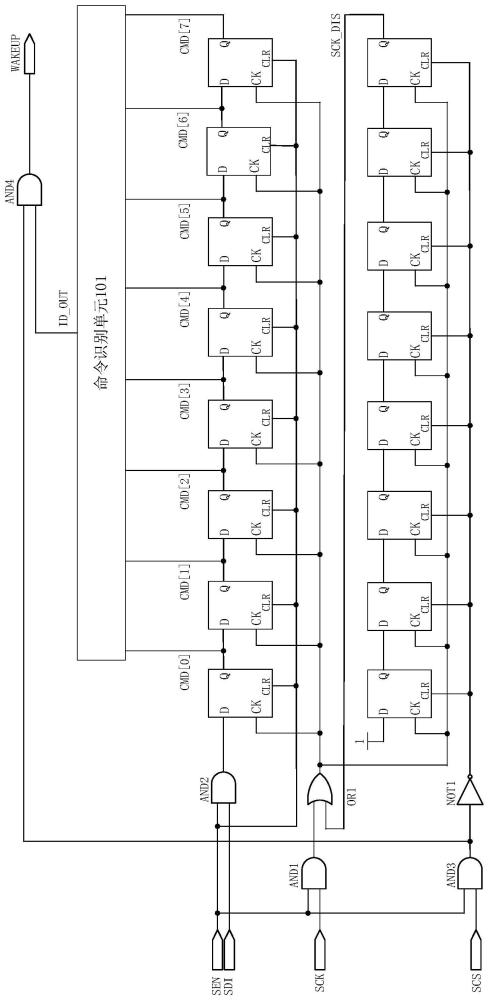

5、为了实现上述的第一目的,本发明提供的一种休眠唤醒电路,中,包括:输入端子、时钟控制寄存单元、命令寄存单元、命令识别单元和输出端子,输入端子分别连接时钟控制寄存单元和命令寄存单元,命令寄存单元连接命令识别单元,命令识别单元连接输出端子;输入端子包括唤醒使能端、命令接收端、时钟端,时钟控制寄存单元包括多个串联的时钟控制寄存器,命令寄存单元包括多个串联的命令寄存器,时钟控制寄存器和命令寄存器均为d触发器;时钟控制寄存器和命令寄存器的ck端与时钟端连接,时钟控制寄存单元中的第一个时钟控制寄存器的d端获取第一电平信号,时钟控制寄存单元中的最后一个时钟控制寄存器的q端连接时钟端,命令寄存单元中的第一个命令寄存器的d端连接命令接收端,每一个命令寄存器的q端连接命令识别单元,命令识别单元连接输出端子;唤醒使能端获取到唤醒使能信号以及时钟端获取到时钟信号时,命令接收端获取当前唤醒命令,命令寄存单元开始存储当前唤醒命令,当时钟控制寄存单元中的最后一个时钟控制寄存器的q端输出第二电平信号时,命令寄存单元停止存储当前唤醒命令,命令识别单元比较确定当前唤醒命令和预设唤醒命令匹配后使输出端子输出唤醒信号。

6、由上述方案可见,本发明的命令接收端从外部的唤醒设备接收到当前唤醒命令时,命令识别单元确定当前唤醒命令和预设唤醒命令匹配后使输出端子输出唤醒信号。本发明与现有的使用gpio电平或边沿唤醒相比,只有在接收到特定的唤醒命令时才会触发芯片唤醒,可以降低芯片的平均休眠电流,且当芯片连接的外设设备发送非唤醒命令或是芯片接收到外部干扰信号时,唤醒休眠电路不予响应使得芯片继续保持休眠状态,保持系统稳定性。

7、进一步的方案是,第一与门和第一或门,第一与门的第一输入端连接唤醒使能端,第一与门的第二输入端连接时钟端,第一与门的输出端连接第一或门的第一输入端,第一或门的第二输入端连接时钟控制寄存单元中的最后一个时钟控制寄存器的q端,第一或门的输出端分别连接每一个时钟控制寄存器的ck端和每一个命令寄存器的ck端。

8、由此可见,时钟控制寄存器的ck端和命令寄存器的ck端获取到相同的信号,使得当前唤醒命令的获取更稳定。

9、进一步的方案是,每一个命令寄存器的clr端连接唤醒使能端。

10、由此可见,可以根据唤醒使能端的唤醒使能信号同步清零命令寄存单元保存的当前唤醒命令。

11、进一步的方案是,第一电平信号为高电平信号,第二电平信号为高电平信号。

12、由此可见,时钟控制寄存单元可以通过输出高电平信号结束当前输入命令的获取。

13、进一步的方案是,第二与门,第二与门的第一输入端连接唤醒使能端,第二与门的第二输入端连接命令接收端,第二与门的输出端连接命令寄存单元中第一个命令寄存器的d端。

14、进一步的方案是,每一个时钟控制寄存器的clr端连接唤醒使能端。

15、进一步的方案是,第三与门、第一非门、第四与门,输入端子还包括片选端;第三与门的第一输入端连接唤醒使能端,第三与门的第二输入端连接片选端,第三与门的输出端连接第一非门的输入端,第一非门的输出端连接每一个时钟控制寄存器的clr端,第四与门的第一输入端连接所述第三与门的输出端,所述第四与门的第二输入端连接所述命令识别单元,所述第四与门的输出端连接所述输出端子。

16、由此可见,连接的外部唤醒设备可以通过spi通信的方式唤醒芯片。

17、为了实现上述的第二目的,本发明提供的一种芯片,其中,包括上述的休眠唤醒电路,芯片用于从连接的外部设备获取唤醒命令。

18、为了实现上述的第三目的,本发明提供的一种电子设备,包括壳体,其中:所述壳体内包括上述的芯片。

19、为了实现上述的第四目的,本发明提供一种休眠唤醒方法,应用于的休眠唤醒电路,其中,包括以下步骤:唤醒使能端获取到唤醒使能信号以及时钟端获取到时钟信号时,命令接收端获取当前唤醒命令,命令寄存单元开始存储当前唤醒命令,当时钟控制寄存单元中的最后一个时钟控制寄存器的q端输出第二电平信号时,命令寄存单元停止存储当前唤醒命令,命令识别单元比较确定当前唤醒命令和预设唤醒命令匹配后使输出端子输出唤醒信号。

20、由上述方案可见,本发明实现只有接收到特定的唤醒命令时才唤醒芯片,从而降低芯片的平均休眠电流,降低芯片功耗。

技术特征:

1.一种休眠唤醒电路,其特征在于,包括:

2.如权利要求1所述的休眠唤醒电路,其特征在于,还包括:

3.如权利要求1所述的休眠唤醒电路,其特征在于:

4.如权利要求1所述的休眠唤醒电路,其特征在于:

5.如权利要求1所述的休眠唤醒电路,其特征在于,还包括:

6.如权利要求1所述的休眠唤醒电路,其特征在于,还包括:

7.如权利要求1至5任一项所述的休眠唤醒电路,其特征在于,还包括:

8.一种芯片,其特征在于,包括:

9.一种电子设备,包括壳体,其特征在于:

10.一种休眠唤醒方法,应用于上述权利要求1至7任意一项所述的休眠唤醒电路,其特征在于,包括以下步骤:

技术总结

本发明提供一种休眠唤醒电路、方法、芯片及电子设备,其中,电路包括:输入端子、时钟控制寄存单元、命令寄存单元、命令识别单元和输出端子,输入端子连接时钟控制寄存单元和命令寄存单元,命令寄存单元连接命令识别单元,命令识别单元连接输出端子;输入端子包括唤醒使能端、命令接收端、时钟端;时钟控制寄存器和命令寄存器的CK端与时钟端连接,时钟控制寄存单元中的第一个时钟控制寄存器的D端获取第一电平信号,时钟控制寄存单元中的最后一个时钟控制寄存器的Q端连接时钟端,命令寄存单元中的第一个命令寄存器的D端连接命令接收端,每一个命令寄存器的Q端连接命令识别单元,命令识别单元连接输出端子。本发明可以降低芯片的平均休眠电流。

技术研发人员:杨一聪,朱国钟,陈昊

受保护的技术使用者:珠海市凌珑宇芯科技有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!