一种基于eDRAM的高密度高可靠性存内计算电路

本发明涉及神经形态电路、存储器内计算电路、edram电路等领域,尤其涉及高密度高可靠性存内计算电路设计领域,具体涉及一种基于edram的高密度高可靠性存内计算电路。

背景技术:

1、随着人工智能和大数据应用的迅猛发展,对于处理大规模数据的需求愈发迫切。传统冯诺依曼计算机架构在存储器和处理器之间存在瓶颈,导致数据传输效率不高,难以满足当今大规模数据处理的要求。人工智能算法的日益复杂和数据量的爆炸性增长进一步强调了对高效存储和处理的需求。

2、存内计算技术将存储器和处理器结合,能够大幅减少数据传输的需求,提高计算效率。现有的存内计算技术可以根据信号类型简单的分为数字型存内计算和模拟型存内计算。以静态随机存取存储器(static random access memory,sram)为代表的数字存算具有速度快、可靠性高等优点,但是也面临着制造成本高、密度低、能耗大等问题。以非易失性存储器为代表的模拟存算具有密度高、功耗低等优点,但受限于当前工艺,模拟存算的可靠性还需要进一步提高。嵌入式动态随机存取存储器(embedded dynamic random accessmemory,edram)具有高密度、低功耗和高可靠性等优点,可以用于实现高密度高可靠性存内计算电路。

技术实现思路

1、本发明的目的在于针对目前冯诺依曼架构瓶颈,以及存内计算技术高密度与高可靠性难以兼容等难题,提供一种基于edram的高密度高可靠性的存内计算电路,用于神经形态芯片中的关键性乘累加操作,实现大规模并行计算,从而在提高硬件计算效率保证高可靠性。

2、本发明的技术方案是:

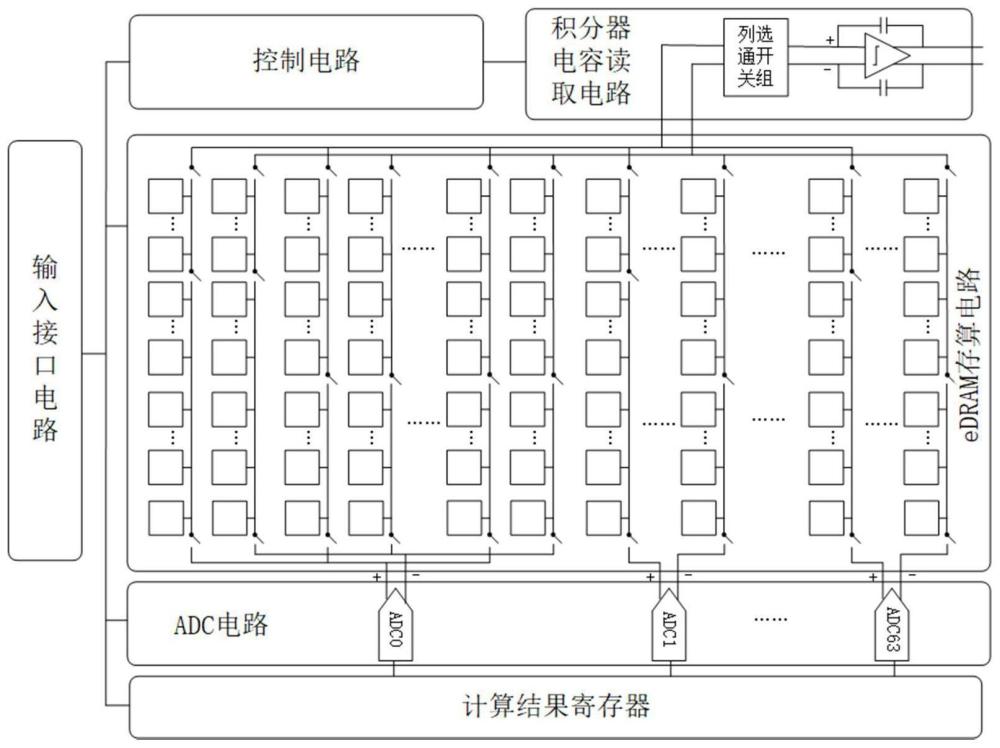

3、一种基于edram的高密度高可靠性存内计算电路,包括edram存算电路、adc电路、计算结果寄存器、控制电路和积分器电容读取电路;

4、所述的控制电路用于控制所述存内计算电路的工作模式,所述工作模式为计算模式或电容读取模式;

5、所述的edram存算电路包括由多个基本单元组成的阵列,edram存算电路内部存有预先写入的权重;在计算模式下,所述的edram存算电路根据内部存储的权重对外部输入的原始数据进行乘累加操作,并将计算结果输入到adc电路;

6、所述的adc电路用于接收edram存算电路的计算结果,并将计算结果转换为数字信号;

7、所述的计算结果寄存器用于存储adc电路转换后的计算结果;

8、所述积分器电容读取电路用于在电容读取模式下读取edram存算电路每个基本单元的实际电容值,根据实际电容值矫正计算结果。

9、进一步的,所述的基本单元由三个场效应管m1、m2、m3和一个电容构成,m1的漏极和m2的基极相连,相连处形成权重存储节点,m1的基极为基本单元的写入控制端,用于接收行选通信号,m1的源极为基本单元的权重写入端,用于写入权重;m2的漏极与m3的漏极和电容的一端相连,相连处形成电容参考节点,电容的另一端为基本单元的结果输出端,其电压代表该基本单元的计算结果,m2的源极为基本单元的数据输入端,用于在计算过程中输入原始数据;m3的源极接电源电压,m3的基极为基本单元的计算控制端,用于控制计算过程中电容参考节点电压复位。

10、进一步的,所述权重为一个多位二进制数,edram存算电路中基本单元的列数为权重位数的两倍,每两列基本单元存储权重的同一位;所述原始数据为多个一位二进制数,edram存算电路中基本单元的行数与原始数据的数量相等,多个原始数据同时输入各行基本单元。

11、更进一步的,所述edram存算电路在进行所述乘累加操作前需要预先写入权重,在写入权重时,基本单元的写入控制端接低电平,数据输入端接高电平,计算控制端接低电平,权重的按位依次从各列基本单元的权重写入端输入,并存储在基本单元的权重存储节点;在进行所述乘累加操作时,基本单元的写入控制端接高电平,权重写入端悬空,计算控制端接高电平,原始数据从数据输入端反相输入。

12、进一步的,所述的edram存算电路中,每一行所述edram单元的写入控制端连接同一个字线,数据输入端连接同一个源线,计算控制端连接同一个电容复位线;每一列所述edram单元权重写入端连接同一个写入位线,结果输出端连接同一个读取位线;

13、所述字线用于接收所述edram存算电路的行选通信号,所述源线用于输入代表原始数据的电压,所述电容复位线用于复位电容参考节点的电压,所述写入位线用于写入权重值,所述读取位线用于输出代表edram存算电路计算结果的各位的模拟电压。

14、更进一步的,所述的读取位线上同时设置复位开关s2、列加权开关s3和电荷重分配开关s4,复位开关s2连接至地,列加权开关s3用于实现对不同读取位线赋权重的不同位,电荷重分配开关s4连接edram存算电路和adc电路,用于实现电荷重分配和adc采样;

15、在进行乘累加操作时,复位开关s2首先闭合使读取位线电压复位,读取位线连接的所有基本单元的计算控制端接高电平,基本单元根据其存储的权重对原始数据进行加权计算,最后复位开关s2断开,各列基本单元进行电荷重分配,电压稳定后,读取位线上的电压即为乘累加操作的计算结果,也为edram存算电路的计算结果。

16、更进一步的,所述的adc电路由多个差分逐次逼近型adc构成,每个差分逐次逼近型adc的正采样端口和负采样端口分别连接8个读取位线,在计算过程中差分逐次逼近型adc采样电容参与电荷重分配,计算结束后差分逐次逼近型adc将读取位线上的模拟电压转换为数字信号。

17、进一步的,所述的积分器电容读取电路由列选通开关组和积分器构成,列选通开关组连接所述的edram存算电路,依次对edram存算电路的各列基本单元进行选通,每次选通存储了权重同一位的2列基本单元,所述积分器由运算放大器和积分电容构成,对所选通的2列基本单元的计算结果进行积分后输出,从而读取对应的实际电容值。

18、进一步的,所述存内计算电路还包括输入/输出接口电路,用于接收原始数据并传送到edram存算电路中,也用于读出计算结果寄存器中存储的计算结果。

19、本发明旨在解决现有技术中存储和计算电路之间的瓶颈问题,通过改进edram结构和引入创新性的电路设计,实现了更高的集成度和更可靠的存内计算电路。通过本发明,不仅可以有效提高数据存储密度,还能够在计算过程中保持高可靠性,为未来高性能计算和人工智能领域的应用提供了全新的解决方案。

20、本发明的有益效果是:

21、本发明提供一种基于edram的高密度高可靠性存内计算电路,相较于传统的冯诺依曼结构具有存储器和处理器紧密结合的优点,可以避免数据在存储器和处理器之间反复传输,从而大幅提高计算效率;相较于目前的存内计算电路,本发明提出了一种适用于存内计算的edram基本单元及计算电路,通过电容充放电过程实现乘累加计算,利用列加权技术和电荷重分配技术实现不同权重位和不同输入位的加权,结构简单,控制容易,有效解决现有存内计算电路高密度和高可靠性难以兼容的问题。

- 还没有人留言评论。精彩留言会获得点赞!