集成电路系统、组件、设备及内存管理方法与流程

本公开涉及内存,尤其涉及一种集成电路系统、组件、设备及内存管理方法。

背景技术:

1、在片上系统(system on chip,soc)的软件设计中,通过使用虚拟地址空间,程序可以使用相邻的虚拟地址来访问物理内存中不相邻的大内存缓冲区,也可以使用一系列虚拟地址来访问大于可用物理内存的内存缓冲区。因此,在一个soc系统中,软件普遍运行在虚拟地址空间。软件调用soc上的主设备访问内存时,会使用虚拟地址下发给从设备,由从设备里的地址翻译模块进行虚拟地址到物理地址的翻译。虚拟地址到物理地址的映射关系由页表决定,页表由软件提前建立好放在内存当中。因此,地址翻译模块在进行地址翻译之前,需要从内存中读取对应的页表,然后再进行地址翻译。

2、为了缓解地址翻译模块从内存中读页表的延时,通常在地址翻译模块中设置一定大小的缓存空间,来进行页表的缓存。但是随着soc设计规模的不断扩大,地址翻译模块的数量也逐渐增加,传统的页表缓存模式下,每个地址翻译模块会无差别缓存所需的页表,那么会出现一个页表同时占用多个地址翻译模块的缓存空间的情况,造成缓存空间的浪费。

技术实现思路

1、本公开的目的是提供一种集成电路系统、组件、设备及内存管理方法,解决了现有技术中地址翻译模块缓存空间浪费的技术问题。

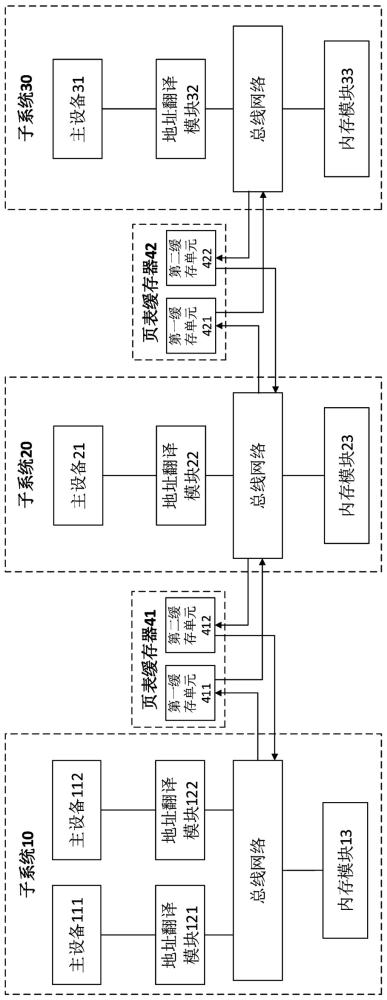

2、根据本公开的一个方面,提供一种集成电路系统,包括多组主设备和多组地址翻译模块,对应的一组主设备、一组地址翻译模块属于一个子系统,集成电路系统还包括位于子系统边界处的页表缓存器,子系统包括还包括内存模块;地址翻译模块包括页表缓存单元;

3、地址翻译模块,被配置为:在接收到其所在的第一子系统中对应的主设备发出的待翻译的目标地址且翻译目标地址所需的至少一个页表在对应的页表缓存单元中未命中时,判断未命中的至少一个页表对应的内存模块是否为第一子系统的内存模块;若是,则从第一子系统的内存模块中请求对应的页表;否则,从位于第一子系统连接第二子系统的连接路径上的一页表缓存器或第二子系统的内存模块中请求对应的页表,第二子系统为未命中的至少一个页表对应的内存模块所在的子系统,位于连接路径上的页表缓存器为位于连接路径上的子系统边界处的页表缓存器;其中,从第一子系统的内存模块中请求到的页表被缓存于地址翻译模块对应的页表缓存单元中,从第二子系统的内存模块中请求到的页表被缓存于位于连接路径上的至少一页表缓存器中;

4、根据请求到的页表,对接收到的目标地址进行地址翻译。

5、在一些实施例中,上述集成电路系统中,地址翻译模块,被配置为从位于第一子系统连接第二子系统的连接路径上的一页表缓存器或第二子系统的内存模块中请求对应的页表,包括:

6、地址翻译模块,被配置为根据目标地址生成页表读取请求,并将页表读取请求发送至第一子系统连接第二子系统的连接路径上最靠近第一子系统的页表缓存器;

7、任一页表缓存器,被配置为在接收到页表读取请求时,判断当前页表缓存器中是否有页表读取请求命中的页表,若是,则通过连接路径将命中的页表返回给发出页表读取请求的地址翻译模块,否则,判断第二子系统是否为与当前页表缓存器直接连接的子系统;

8、若是,则从第二子系统的内存模块中请求对应的页表,并通过连接路径将请求到的页表返回给发出页表读取请求的地址翻译模块;

9、否则,将接收到的页表读取请求发送至连接路径上最靠近当前页表缓存器的下一个页表缓存器。

10、在一些实施例中,上述集成电路系统中,页表读取请求还携带第二子系统的子系统标识;

11、页表缓存器,被配置为判断第二子系统是否为与当前页表缓存器直接连接的子系统,包括:

12、页表缓存器,被配置为根据页表读取请求携带的子系统标识,判断页表读取请求对应的第二子系统是否为与当前页表缓存器直接连接的子系统。

13、在一些实施例中,上述集成电路系统中,页表缓存器,还被配置为在接收到的页表读取请求携带的子系统标识对应的第二子系统为与当前页表缓存器具有预设绑定关系的子系统,且接收到连接路径返回的该页表读取请求所请求的页表时,对该页表进行缓存。

14、在一些实施例中,上述集成电路系统中,页表读取请求还携带对应的页表级数;

15、页表缓存器,还被配置为在接收到的页表读取请求携带的页表级数等于对应的预设值,且接收到连接路径返回的该页表读取请求所请求的页表时,对该页表进行缓存。

16、在一些实施例中,上述集成电路系统中,页表读取请求还携带对应的页表读标识;

17、页表缓存器,还被配置为在接收到的页表读取请求携带对应的页表读标识,且接收到连接路径返回的该页表读取请求所请求的页表时,对该页表进行缓存。

18、在一些实施例中,上述集成电路系统中,页表缓存器,还被配置为在接收连接路径返回的页表时,根据该页表中的物理地址,判断该页表对应的子系统是否为与当前页表缓存器具有预设绑定关系的子系统,若是,则对该页表进行缓存。

19、在一些实施例中,上述集成电路系统中,页表缓存器包括第一缓存单元和第二缓存单元;

20、第一缓存单元,被配置为在接收到连接路径沿第一方向发来的页表读取请求时,判断当前第一缓存单元中是否有页表读取请求命中的页表;在接收到连接路径沿第二方向返回的页表,且该页表对应的子系统为与当前第一缓存单元具有预设绑定关系的子系统时,对该页表进行缓存;

21、第二缓存单元,被配置为在接收到连接路径沿第二方向发来的页表读取请求时,判断当前第二缓存单元中是否有页表读取请求命中的页表;在接收到连接路径沿第一方向返回的页表且该页表对应的子系统为与当前第二缓存单元具有预设绑定关系的子系统时,对该页表进行缓存。

22、在一些实施例中,上述集成电路系统中,子系统还包括互连网络;

23、在一些实施例中,上述集成电路系统中,主设备访问其所在的子系统的内存模块所需要的延时小于预设阈值。

24、在一些实施例中,上述集成电路系统中,至少一子系统包括至少两个主设备。

25、在一些实施例中,上述集成电路系统中,子系统中的地址翻译模块与主设备一一对应。

26、在一些实施例中,上述集成电路系统中,集成电路系统为numa系统。

27、根据本公开的另一方面,提供一种电子组件,包括上述任一实施例的集成电路系统。

28、根据本公开的另一方面,提供一种电子设备,包括上述任一实施例的电子组件。

29、根据本公开的另一方面,提供一种内存管理方法,应用于集成电路系统中的地址翻译模块,集成电路系统包括多组主设备和多组地址翻译模块,对应的一组主设备、一组地址翻译模块属于一个子系统,集成电路系统还包括位于子系统边界处的页表缓存器,子系统还包括内存模块;地址翻译模块包括页表缓存单元;上述方法包括:

30、在接收到所在的第一子系统中对应的主设备发出的待翻译的目标地址且翻译目标地址所需的至少一个页表在对应的页表缓存单元中未命中时,判断未命中的至少一个页表对应的内存模块是否为第一子系统的内存模块;若是,则从第一子系统的内存模块中请求对应的页表;否则,从位于第一子系统连接第二子系统的连接路径上的一页表缓存器或第二子系统的内存模块中请求对应的页表,第二子系统为未命中的至少一个页表对应的内存模块所在的子系统,位于连接路径上的页表缓存器为位于连接路径上的子系统边界处的页表缓存器;其中,从第一子系统的内存模块中请求到的页表被缓存于地址翻译模块对应的页表缓存单元中,从第二子系统的内存模块中请求到的页表被缓存于位于连接路径上的至少一页表缓存器中;

31、根据请求到的页表,对接收到的目标地址进行地址翻译。

- 还没有人留言评论。精彩留言会获得点赞!