一种门禁系统的制作方法

1.本技术涉及门禁系统的技术领域,尤其是涉及一种门禁系统。

背景技术:

2.随着社会的发展与进步,越来越多的人购买电动自行车以便于出行。但是,因电动自行车私自推进住宿处容易导致发生火宅爆炸的悲剧。现有的对电动自行车入户充电的行为是通过人力进行监控,容易出现监控人员疏忽而导致监控不到位,因此存在一定的改进空间。

技术实现要素:

3.为了实现监管电动自行车,及时提醒监管人员,防止电动自行车违规入户进行充电,本技术提供一种门禁系统。

4.本技术提供的一种门禁系统采用如下的技术方案:

5.一种门禁系统,包括天线传输电路、微控制电路、锁相环电路、电源电路、差分放大电路和功放电路,所述电源电路用于给智锂狗门禁系统供电,所述锁相环电路的输入端耦接于微控制电路以接收控制指令,所述功放电路耦接于锁相环电路,所述天线传输电路耦接于功放电路,所述差分放大电路的输入端耦接于天线传输电路,所述差分放大电路的输出端耦接于微控制电路,所述微控制电路的输出端串联有警报电路,当所述微控制电路输出启动信号时,所述警报电路启动输出警报信号。

6.通过采用上述技术方案,电源电路给智锂狗门禁系统的读写器提供工作电压,微控制电路发送控制指令至锁相环电路,锁相环电路接收到控制指令后,使锁相环锁定震荡频率,震荡频率锁定后,微控制电路发送调制信号至功放电路,功放电路接收经过调制的震荡频率并对其进行功率放大处理且输出至天线传输电路,天线传输电路输出寻标签指令载波信号,当贴有电子标签的电动自行车进入到安检区域时,天线传输电路接收电子标签激活后的反射信号并输出至差分放大电路,差分放大电路对反射信号进行放大滤波整形处理并输出至微控制电路,微控制电路接收到放大处理后的信号后进行解码并输出启动信号至警报电路,警报电路启动输出警报信号,实现监管电动自行车,防止电动自行车违规入户进行充电,预防安全事故发生。

7.可选的,所述天线传输电路包括芯片u3,所述芯片u3包括控制信号输入端、射频输入端和射频输出端,所述控制信号输入端耦接于微控制电路以输入控制信号,所述射频输入端耦接有天线端j1以输入无线射频信号,所述射频输出端耦接有天线切换开关ant以输出天线射频信号。

8.通过采用上述技术方案,芯片u3的控制信号输入端输入微控制电路输出的控制信号,芯片u3接收到控制信号后,芯片u3的射频输出端输出天线信号用于寻找特殊标签,芯片u3的射频输入端输入电子标签激活后反射的无线射频信号,实现天线射频信号的传输功能。

9.可选的,所述微控制电路包括芯片u7、第一反相器u13、第二反相器u21和存储芯片u8,所述芯片u7包括锁相信号输出端、控制信号输出端、放大信号输入端、启动信号输出端、数据输出端和调制信号输出端,所述第一反相器u13和第二反相器u21均包括输入端和输出端,所述存储芯片u8包括数据输入端,所述芯片u7的锁相信号输出端耦接于第二反相器u21的输入端,所述第二反相器u21的输出端耦接于锁相环电路,所述芯片u7的控制信号输出端耦接于芯片u3的控制信号输入端,所述第一反相器u13的输入端耦接于差分放大电路以接收经过放大处理的信号,所述芯片u7的放大信号输入端耦接于第一反相器u13的输出端以输入放大处理的信号,所述芯片u7的启动信号输出端耦接于警报电路以输出启动信号,所述芯片u7的数据输出端耦接于存储芯片u8的数据输入端,所述存储芯片u8用于存储数据,所述芯片u7的调制信号输出端耦接于功放电路以输出调制信号至功放电路。

10.通过采用上述技术方案,芯片u7接收到电源电路输出的供电电压后得电启动工作,芯片u7的锁相信号输出端输出锁相控制信号至第二反相器u21的输入端,第二反相器u21的输出端将锁相控制信号输出至锁相环电路,使锁相环电路锁定震荡频率,芯片u7的调制信号输出端输出调制信号至功放电路,使功放电路接收到调制信号后对锁定的震荡频率进行调制,第一反相器u13的输入端接收差分放大电路输出的经过放大整流处理的射频信号并通过输出端输出至芯片u7,芯片u7的放大信号输入端接收第一反相器u13输出端输出的放大整形的射频信号,芯片u7对其进行解码并转换成启动信号,当有电动自行车进入到安检区域内时,芯片u7的启动信号输出端输出启动信号至警报电路,使警报电路启动输出警报信号,存储芯片u8的数据输入端接收芯片u7的数据输出端输出的数据信号并将其存储,实现数据存储功能。

11.可选的,所述锁相环电路包括芯片u1和压腔震荡器u20,所述芯片u1包括震荡输入端、内部电荷泵输出端、锁相控制信号输入端和电源端,所述压腔震荡器u20包括六个引脚,所述芯片u1的电源端耦接于电源电路以接收供电电压,所述芯片u1的震荡输入端耦接于微控制电路以输入震荡频率,所述芯片u1的内部电荷泵输出端耦接于压腔振荡器u20的第一引脚以驱动压腔震荡器启动,所述芯片u1的锁相控制信号输入端耦接于第二反相器u21的输出端以接收锁相控制信号,所述压腔震荡器u20的第三引脚耦接于电源电路以输入工作电压,所述压腔震荡器u20的第四引脚耦接于功放电路。

12.通过采用上述技术方案,芯片u1的电源端输入启动电压,芯片u1得电启动,芯片u1的震荡输入端输入震荡频率,芯片u1的锁相控制信号输入端输入锁相控制信号,芯片u1接收到锁相控制信号后,对震荡频率进行锁定,芯片u1的内部电荷泵输出端驱动压腔震荡器u20启动,压腔震荡器u20将锁定后的震荡频率输出至功放电路并对其进行功放处理。

13.可选的,所述功放电路包括芯片u12和射频开关二极管e4,所述芯片u12包括电源输入端、射频输入端和射频输出端,所述芯片u12的电源输入端耦接于电源电路以输入供电电压,所述芯片u12的射频输入端耦接于射频开关二极管e4的一端,所述射频开关二极管e4的另一端耦接于锁相环电路以输入锁定的震荡频率,所述射频开关二极管e4的另一端还耦接于微控制电路以接收调制信号,所述芯片u12的射频输出端耦接于天线传输电路以输出经过调制锁定的震荡射频信号至天线传输电路。

14.通过采用上述技术方案,芯片u12的电源输入端输入工作电压,芯片u12得电启动,射频开关二极管e4呈闭合状态,芯片u12的射频输入端同时输入震荡评率和微控制电路输

出的调制信号,形成调制锁定的震荡频率输入至芯片u12,芯片u12对调制锁定的震荡频率进行功放处理并通过芯片u12的射频输出端输出放大的射频信号至天线传输电路,实现对震荡信号功放处理功能。

15.可选的,所述差分放大电路包括检波子电路和三级放大子电路,所述检波子电路的输入端耦接于天线传输电路的输出端,所述检波子电路的输出端耦接于三级放大子电路的输入端,所述三级放大子电路的输出端耦接于微控制电路。

16.通过采用上述技术方案,检波子电路接收到天线传输电路输出的微弱的电子标签激活后反射的无线射频信号,检波子电路将微弱的射频信号进行耦合滤波并输出至三级放大子电路,三级放大子电路接收到经过耦合滤波处理的微弱的射频信号后对其进行三级放大,将放大射频信号输出至微控制电路,实现耦合滤波放大射频信号功能。

17.可选的,所述电源电路包括芯片u2、芯片u5和芯片u6,所述芯片u2的输入端耦接于电源接口,所述芯片u2的输出端耦接于功放电路,所述芯片u5的输入端耦接于电源接口,所述芯片u5的输出端耦接于芯片u6的输入端,所述芯片u6的输出端分别耦接于微控制电路和天线传输电路,所述芯片u5的输出端还耦接于锁相环电路,所述芯片u5的输出端还耦接于警报电路。

18.通过采用上述技术方案,芯片u2的输入端从电源接口输入电压,芯片u2电源接口的电压转换成满足功放电路工作的工作电压,并通过芯片u2的输出端输出至功放电路,芯片u5的输入端将电源接口电压转换成供给锁相环电路驱动的电压,芯片u6将芯片u5的输出端输出的电压转换后输出至微控制电路和天线传输电路以供电,实现给系统中各电路供电功能。

19.可选的,警报电路包括蜂鸣器y3和第十八三极管q18,所述第十八三极管q18的基极耦接于芯片u7的启动信号输出端,所述第十八三极管q18的集电极与蜂鸣器y3串联后耦接于电源电路,所述第十八三极管q18的发射极接地。

20.通过采用上述技术方案,当警报电路接收到微控制电路输出的启动信号时,第十八三极管q18的基极输入高电平,第十八三极管q18导通,蜂鸣器y3通电发出响声,实现警报提醒功能。

21.综上所述,本技术包括以下至少一种有益技术效果:

22.1.通过微控制电路发送控制指令至锁相环电路,锁相环电路接收到控制指令后,使锁相环锁定震荡频率,震荡频率锁定后,微控制电路发送调制信号至功放电路,功放电路接收经过调制的震荡频率并对其进行功率放大处理且输出至天线传输电路,天线传输电路输出寻标签指令载波信号,当贴有电子标签的电动自行车进入到安检区域时,天线传输电路接收电子标签激活后的反射信号并输出至差分放大电路,实现自动监管电动自行车入户;

23.2.通过设置有差分放大电路,能够使天线传输电路识别到电子标签反射的微弱的射频信号进行滤波耦合放大,便于微控制电路接收反射的射频信号,更加精准的识别电动自行车,进一步防止电动自行车进入居住区;

24.3.通过门禁系统设置有警报电路,当有电动自行车进入到安检区域时,警报电路启动并输出警报提醒信号,具有警报提醒监控者功能。

附图说明

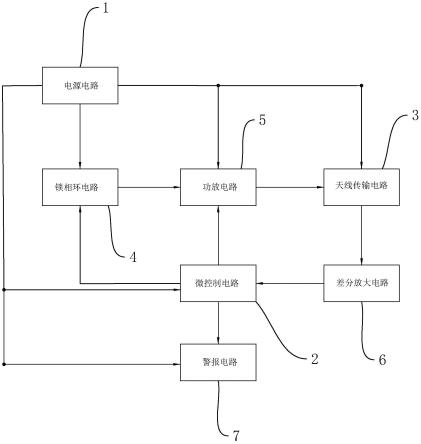

25.图1是本技术实施例一种门禁系统的结构框图。

26.图2是本技术实施例一种门禁系统的电源电路的电路图。

27.图3是本技术实施例一种门禁系统的天线传输电路的电路图。

28.图4是本技术实施例一种门禁系统的微控制电路的电路图。

29.图5是本技术实施例一种门禁系统的锁相环电路的电路图。

30.图6是本技术实施例一种门禁系统的功放电路的电路图。

31.图7是本技术实施例一种门禁系统的差分放大电路的电路图。

32.附图标记说明:1、电源电路;2、微控制电路;3、天线传输电路;4、锁相环电路;5、功放电路;6、差分放大电路;61、检波子电路;62、三级放大子电路;621、第一放大单元;622、第二放大单元;623、第三放大单元;7、警报电路。

具体实施方式

33.以下结合附图1-7对本技术作进一步详细说明。

34.本技术实施例公开一种门禁系统。

35.参照图1,一种门禁系统包括电源电路1、微控制电路2、天线传输电路3、锁相环电路4、功放电路5、差分放大电路6和警报电路7,电源电路1分别耦接于微控制电路2、天线传输电路3、锁相环电路4、功放电路5、差分放大电路6和警报电路7以提供工作电压,锁相环电路4耦接于微控制电路2以接收锁相控制信号,功放电路5耦接于锁相环电路4以接收锁定的震荡频率信号,功放电路5还耦接于微控制电路2以接收调制信号,天线传输电路3耦接于功放电路5,差分放大电路6的输入端耦接于天线传输电路3,差分放大电路6的输出端耦接于微控制电路2,警报电路7耦接于微控制电路2以接收启动信号,当警报电路7接收到启动信号时,警报电路7启动输出警报信号。

36.参照图2,电源电路1包括电源接口j2、型号为to-263a的芯片u2、型号为st1s06的芯片u4、型号为lm340s5的芯片u5和型号为ncp603的芯片u6和u9。芯片u2包括五个引脚,芯片u2的第二引脚为输入端,芯片u2的第四引脚为输出端,电源接口j2的正极端耦接有整流二极管d16,整流二极管d16的另一端耦接有第一百一十四电容c114,第一百一十四电容c114的另一端接地,整流二极管d16与第一百一十四电容c114的连接节点耦接于芯片u2的第二引脚,芯片u2的第一引脚耦接于第一百一十四电容c114,芯片u2的第三引脚接地,芯片u2的第四引脚耦接有第九十二电阻r92,第九十二电阻r92的另一端耦接有第九十一电阻r91,第九十一电阻r91的另一端接地,第九十二电阻r92与芯片u2的第四引脚的连接节点耦接有第一百一十三电容c113,第一百一十三电容c113的另一端接地,第一百一十三电容c113与芯片u2的第四引脚的连接节点输出pavcc电压,芯片u2的第五引脚耦接于第九十二电阻r92与第九十一电阻r91的连接节点。芯片u4包括七个引脚,芯片u4的第六引脚耦接于芯片u2的第四引脚,芯片u4的第五引脚耦接于第六引脚,芯片u4的第五引脚和第六引脚的连接节点耦接于芯片u4的第四引脚。芯片u4的第七引脚接地,芯片u4的第一引脚耦接有第八十一电阻r81,第八十一电阻r81的另一端接地。芯片u4的第一引脚还耦接有第八十二电阻r82,第八十二电阻r82的另一端耦接有第八十六电阻r86,第八十六电阻r86的另一端耦接于芯片u4的第四引脚。芯片u4的第二引脚接地,芯片u4的第三引脚耦接有第九电感l9,第

九电感l9的另一端耦接有第一百零四电容c104,第一百零四电容c104的另一端接地,第九电感l9与第一百零四电容c104的连接节点耦接有第一百零八电容c108,第一百零八电容c108的另一端接地,第九电感l9与第一百零四电容c104的连接节点还用于输出pa_vcc电压。

37.芯片u5包括四个引脚,芯片u5的第三引脚为输入端,芯片u6包括五个引脚,芯片u6的第一引脚为输入端,芯片u6的第五引脚为输出端,芯片u9与芯片u6结构相同。芯片u5的第三引脚耦接于整流二极管d16与第一百一十四电容c114的连接节点,芯片u5的第一引脚和第四引脚均接地,芯片u5的第二引脚分别耦接于芯片u6的第一引脚和芯片u9的第一引脚。芯片u5的第二引脚与芯片u6的第一引脚之间串联有第十四电感l14,第十四电感l14与芯片u5的第二引脚的连接节点耦接有第一百一十一电容c111,第一百一十一电容c111的另一端接地,第十四电感l14与芯片u5的第二引脚的连接节点还耦接有整流二极管d18,第十四电感l14与芯片u5的第二引脚的连接节点与整流二极管d18的连接节点输入5v电压,整流二极管d18的另一端耦接于锁相环电路4用于输出pllvcc电压。第十四电感l14与芯片u6的第一引脚的连接节点耦接有第一百一十五电容c115,第一百一十五电容c115的另一端接地,第一百一十五电容c115与第十四电感l14的连接节点耦接有第一百一十六电容c116,第一百一十六电容c116与第一百一十五电容c115的连接节点耦接有第一百一十七电容c117,第一百一十六电容c116的另一端接地,第一百一十七电容c117的另一端接地。芯片u6的第二引脚接地,芯片u6的第三引脚耦接于第一引脚,芯片u6的第五引脚用于输出vdd33电压。芯片u6的第四引脚耦接有第六十三电阻r63,第六十三电阻r63的另一端耦接于芯片u6的第五引脚,第六十三电阻r63与芯片u6的第四引脚的连接节点耦接有第八十九电阻r89,第八十九电阻r89的另一端接地。芯片u6的第五引脚还耦接有第八十七电容c87,第八十七电容c87与芯片u6的第五引脚的连接节点耦接有第三电容c3,第三电容c3与第八十七电容c87的连接节点耦接有第四电容c4,第八十七电容c87的另一端接地,第三电容c3的另一端接地,第四电容c4的另一端接地。

38.第一百一十六电容c116与第一百一十七电容c117的连接节点输出vcca电压,第一百一十六电容c116与第一百一十七电容c117的连接节点还耦接于芯片u9的第一引脚,芯片u9的第二引脚接地,芯片u9的第三引脚耦接于芯片u9的第一引脚,芯片u9的第四引脚耦接有第九十三电阻r93,第九十三电阻r93的另一端耦接于芯片u9的第五引脚。芯片u9的第五引脚输出电压v_wifi,芯片u5的第五引脚还耦接有第二电容c2,第二电容c2与芯片u5的第五引脚的连接节点耦接有第六十电容c60,第二电容c2的另一端接地,第六十电容c60的另一端接地。芯片u9的第四引脚与第九十三电阻r93的连接节点耦接有第九十四电阻r94,第九十四电阻r94的另一端接地。

39.参照图3,天线传输电路3包括型号为rf1450ds的芯片u3、天线端接口j1和接地端接口j3,天线端接口j1耦合于接地端接口j3,芯片u3包括十七个引脚,芯片u3的第三引脚和第四引脚为控制信号输入端,芯片u3的第六引脚、第八引脚、第十五引脚和第十三引脚为射频输出端,芯片u3的第十一引脚为射频输入端。芯片u3的第一引脚、第五引脚、第七引脚、第九引脚、第十引脚、第十二引脚、第十四引脚和第十七引脚均接地。芯片u3的第二引脚耦接有第七十四电阻r74,第七十四电阻r74的另一端耦接于电源电路1以输入vdd33电压。第七十四电阻r74与芯片u3的第二引脚的连接节点耦接有第七十五电容c75,第七十五电容c75

的另一端接地。芯片u3的第十六引脚耦接有第六十一电阻r61,第六十一电阻r61与芯片u3的第十六引脚的连接节点耦接有第一百零七电容c107,第一百零七电容c107的另一端接地,第六十一电阻r61的另一端耦接于电源电路1以输入vdd33电压。芯片u3的第三引脚耦接有第六十电阻r60,第六十电阻r60与芯片u3的第三引脚的连接节点耦接有第七十四电容c74,第六十电阻r60的另一端耦接于微控制电路2,第七十四电容c74的另一端接地。芯片u3的第四引脚耦接有第三十八电阻r38,第三十八电阻r38与芯片u3的第四引脚的连接节点耦接有第一百零五电容c105,第三十八电阻r38的另一端耦接于微控制电路2,第一百零五电容c105的另一端接地。芯片u3的第十一引脚耦接有第七十一电容c71,第七十一电容c71的另一端耦接有第八十二电容c82,第八十二电容c82的另一端耦接于天线端接口j1。第七十一电容c71与第八十二电容c82的连接节点耦接于差分放大电路6。芯片u3的射频输出端耦接有四个天线切换开关ant,每个天线切换开关ant包括三个接口。芯片u3的第十三引脚耦接有第一天线切换开关ant1,第一天线切换开关ant1的第一接口耦接有第二十九电容c29,第二十九电容c29的另一端耦接于芯片u3的第十三引脚,第一天线切换开关ant1的第二接口和第三接口均接地。芯片u3的第十五引脚耦接有第二线切换开关ant2,第二线切换开关ant2的第一接口耦接有第四十七电容c47,第四十七电容c47的另一端耦接于芯片u3的第十五引脚,第二线切换开关ant2的第二接口和第三接口均接地。芯片u3的第八引脚耦接有第三线切换开关ant3,第三线切换开关ant3的第一接口耦接有第五十二电容c52,第五十二电容c52的另一端耦接于芯片u3的第八引脚,第三线切换开关ant3的第二接口和第三接口均接地。芯片u3的第六引脚耦接有第四线切换开关ant4,第四线切换开关ant4的第一接口耦接有第七十二电容c72,第七十二电容c72的另一端耦接于芯片u3的第六引脚,第四线切换开关ant4的第二接口和第三接口均接地。

40.参照图4,微控制电路2包括型号为lpc2132的芯片u7、型号均为74hct14d第一反相器u13和第二反相器u21、型号为24c08的存储芯片u8、型号为sp3232e的232接口芯片u10、型号为max487e的485接口芯片u11、第一继电器k1、第二继电器k2、12pin接口y4、9pin接口j5和9pin接口j16。芯片u7包括六十四个引脚,芯片u7的第四引脚、第八引脚、第十二引脚和第十六引脚为锁相信号输出端;芯片u7的第二十二引脚和第二十六引脚为数据输出端;芯片u7的第四十引脚和第四十四引脚为控制信号输出端;芯片u7的第三十五引脚为放大信号输入端;芯片u7的第三十九引脚为启动信号输出端;芯片u7的第四十八引脚为调制信号输出端。第一反相器u13和第二反相器u21均包括十四个引脚,第一反相器u13和第二反相器u21的第一引脚、第三引脚、第五引脚、第九引脚、第十一引脚和第十三引脚均为为输入端,第一反相器u13和第二反相器u21的第二引脚、第四引脚、第六引脚、第八引脚、第十引脚和第十二引脚均为输出端。存储芯片u8包括八个引脚,存储芯片u8的第五引脚和第六引脚为数据输入端。485接口芯片u11包括八个引脚,232接口芯片u10包括十六个引脚。

41.芯片u7的第一引脚耦接于9pin接口j5的第三引脚,芯片u7的第二引脚耦接于9pin接口j5的第二引脚,芯片u7的第七引脚耦接于电源电路1以接收vdd33电压,芯片u7的第七引脚还耦接有第六十五电容c65,第六十五电容c65的另一端接地。芯片u7的第九引脚耦接于vapc电压,芯片u7的第十一引脚串联有第三十四电阻r34后耦接于电源电路1以接收vcca电压。第三十四电阻r34的另一端耦接有第四十二电阻r42,第四十二电阻r42的另一端耦接有第五tvs二极管tvs5,第五tvs二极管tvs5的另一端接地。第四十二电阻r42与第五tvs二

极管tvs5的连接节点耦接有第三十三电阻r33,第三十三电阻r33的另一端耦接有第十九三极管q19,第十九三极管q19的基极耦接于第三十三电阻r33,第十九三极管q19的集电极耦接于第三十四电阻r34与芯片u7的第十一引脚,第十九三极管q19的发射极接地。第四十二电阻r42与第五tvs二极管tvs5的连接节点还耦接有第五十七电阻r57,第五十七电阻r57的另一端耦接有第七十八电阻r78,第七十八电阻r78的另一端耦接于9pin接口j16的第七引脚。第五十七电阻r57与第七十八电阻r78的连接节点耦接有第六电阻r6,第六电阻r6的另一端耦接于12pin接口y4的第九引脚。

42.芯片u7的第十七引脚耦接于9pin接口j5的第五引脚,芯片u7的第二十三引脚耦接于电源电路1以输入vdd33电压,芯片u7的第二十四引脚耦接有第四十七电阻r47,第四十七电阻r47的另一端接地,芯片u7的第二十八引脚耦接有第七十电阻r70,第七十电阻r70的另一端耦接有第一光电耦合器,第一光电耦合器的第一接口耦接于第七十电阻r70,第一光电耦合器的第二接口和第三接口均接地,第一光电耦合器的第四接口耦接有第七十一电阻r71,第七十一电阻r71的另一端耦接于电源电路1以输入vcca电压。第七十一电阻r71与第一光电耦合器的第四接口的连接节点耦接于12pin接口y4的第八引脚,第七十一电阻r71与第一光电耦合器的第四接口的连接节点还耦接有第四tvs二极管tvs4,第四tvs二极管tvs4的另一端接地。芯片u7的第三十二引脚耦接有第四十三电阻r43,第四十三电阻r43的另一端耦接于电源电路1以输入vdd33电压;芯片u7的第三十二引脚耦接有第七十二电阻r72,第七十二电阻r72的另一端耦接有第二光电耦合器,第二光电耦合器的第一接口耦接于第七十二电阻r72,第二光电耦合器的第二接口和第三接口均接地,第二光电耦合器的第四接口耦接有第七十三电阻r73,第七十三电阻r73的另一端耦接于电源电路1以输入vcca电压,第二光电耦合器的第四接口与第七十三电阻r73的连接节点耦接于12pin接口y4的第七引脚,第二光电耦合器的第四接口与第七十三电阻r73的连接节点还耦接有第三tvs管tvs3,第三tvs管tvs3的另一端接地。

43.芯片u7的第三十三引脚耦接有短路线圈j8,短路线圈j8的另一端耦接有第五十八电阻r58,第五十八电阻r58的另一端耦接有放电管vdr3,放电管vdr3的另一端耦接于12pin接口y4的第五引脚。第五十八电阻r58与短路线圈j8的连接节点耦接有第一tvs二极管tvs1和第六tvs二极管tvs6,第一tvs二极管tvs1的另一端接地,第六tvs二极管tvs6的另一端耦接有第二tvs二极管tvs2,第二tvs二极管tvs2的另一端接地。短路线圈j8与第五十八电阻r58的连接节点还耦接于485接口芯片u11的第六引脚。芯片u7的第三十四引脚耦接有短路线圈j7,短路线圈j7的另一端耦接于485接口芯片u11的第七引脚。芯片u7的第三十六引脚耦接有第六十四电阻r64,第六十四电阻r64的另一端耦接于12pin接口y4的第一引脚,芯片u7的第三十九引脚耦接有警报电路7,警报电路7包括蜂鸣器y3和npn型第十八三极管q18,第十八三极管q18的基极耦接于芯片u7的第三十九引脚,第十八三极管q18的集电极耦接于蜂鸣器y3,第十八三极管q18的发射极接地,蜂鸣器y3的另一端耦接于电源电路1以输入vcca电压,蜂鸣器y3与第十八三极管q18的集电极的连接节点耦接于12pin接口y4的第三引脚。芯片u7的第四十引脚和第四十四引脚耦接于天线传输电路3,芯片u7的第四十一引脚耦接有第六十七电阻r67,第六十七电阻r67的另一端耦接于电源电路1以输入vdd33电压,芯片u7的第四十二引脚接地,芯片u7的第四十二引脚还耦接有第六十七电容c67,第六十七电容c67的另一端耦接于电源电路1以输入vdd33电压,芯片u7的第四十三引脚耦接于电源电

路1以输入vdd33电压。

44.芯片u7的第五十引脚接地,芯片u7的第五十引脚还耦接有第六十六电容c66,第六十六电容c66的另一端耦接于芯片u7的第五十一引脚,芯片u7的第五十一引脚耦接于电源电路1以输入vdd33电压,芯片u7的第五十一引脚还耦接有第一电阻r1,第一电阻r1的另一端耦接于芯片u1的第五十七引脚,芯片u7的第五十五引脚耦接于9pin接口j5的第四引脚,芯片u7的第五十八引脚耦接与存储芯片u8的第二引脚,芯片u7的第五十八引脚还耦接有第一百零三电容c103,第一百零三电容c103的另一端接地;芯片u7的第五十八引脚耦接于9pin接口j5的第一引脚,芯片u7的第五十八引脚还耦接有第五十九电阻r59,第五十九电阻r59的另一端接地;芯片u7的第六十一引脚耦接有第二十四电容c24,第二十四电容c24的另一端接地,芯片u7的第六十二引脚耦接有第十二电容c12,第十二电容c12的另一端耦接于锁相环电路4,芯片u7的第六十二引脚还耦接有晶振y1,晶振y1的另一端耦接于芯片u7的第六十一引脚。芯片u7的第六十二引脚与第十二电容c12的连接节点耦接有第七电阻r7和第五十电容c50,第七电阻r7的另一端接地,第五十电容c50的另一端接地;芯片u7的第六十三引脚耦接有第一电感l1,第一电感l1的另一端耦接于电源的电路以输入vdd33电压,芯片u7的第六十三引脚与第一电感l1的连接节点耦接有第六十八电容c68,第六十八电容c68的另一端接地,芯片u7的第六十三引脚与第一电感l1的连接节点还耦接有第五电容c5,第五电容c5的两端并联有第六电容c6,第六电容c6的两端并联有第七电容c7,第七电容c7与第六电容c6的连接节点耦接有第二电感l2,第二电感l2的另一端接地。

45.第一反相器u13的第三引脚耦接于芯片u7的第四十八引脚,第一反相器u13的第四引脚耦接于功放电路5,第一反相器u13的第五引脚耦接于差分放大电路6,第一反相器u13的第六引脚耦接于芯片u7的第三十五引脚,第一反相器u13的第六引脚还耦接有第十五电容c15,第食物电容c15的另一端接地,第一反相器u13的第七引脚接地,第一反相器u13的第十四引脚耦接有第四十八电容c48,第四十八电容c48的另一端接地,第四十八电容c48与第一反相器u13的第十四引脚的连接节点耦接有第八十七电阻r87,第八十七电阻r87的另一端耦接于5v电压,第四十八电容c48与第一反相器u13的第十四引脚的连接节点还耦接有第八十八电阻r88,第八十八电阻r88的另一端耦接于电源电路1以输入vdd33电压。

46.第二反相器u21的第一引脚耦接于芯片u7的第四十五引脚,第二反相器u21的第十一引脚耦接于芯片u7的第四引脚,第二反相器u21的第十三引脚耦接于芯片u7的第八引脚,第二反相器u21的第五引脚耦接于芯片u7的第十二引脚,第二反相器u21的第九引脚耦接于芯片u7的第十六引脚,第二反相器u21的第三引脚耦接于第二反相器u21的第二引脚,第二反相器u21的第六引脚耦、第八引脚、第十引脚和第十二引脚均接于锁相环电路4。第二反相器u21的第七引脚接地,第二反相器u21的第十四引脚耦接于pllvcc电压,第二反相器u21的第十四引脚还耦接有第十六电容c16,第十六电容c16的另一端接地。

47.存储芯片u8的第八引脚耦接于电源电路1以输入vdd33电压,存储芯片u8的第八引脚还耦接有第六十九电容c69,第六十九电容c69的另一端接地。存储芯片u8的第一引脚耦接有第七十六电阻r76,第七十六电阻r76的另一端接地,存储芯片u8的第一引脚与第七十六电阻r76的连接节点耦接有第四电阻r4,第四电阻r4的另一端耦接于存储芯片u8的第八引脚;存储芯片u8的第二引脚耦接有第六十七电阻r67,第六十七电阻r67的另一端耦接于芯片u7的第五十七引脚,第六十七电阻r67与存储芯片u8的第二引脚的连接节点耦接有第

九十电阻r90,第九十电阻r90的另一端接地;存储芯片u8的第三引脚耦接有第五电阻r5;存储芯片u8的第四引脚接地;存储芯片u8的第五引脚耦接于芯片u7的第二十六引脚,存储芯片u8的第五引脚还耦接有第三电阻r3,第三电阻r3的另一端耦接于存储芯片u8的第八引脚;存储芯片u8的第六引脚耦接于芯片u7的第二十二引脚,存储芯片u8的第六引脚还耦接有第二电阻r2,第二电阻r2的另一端耦接于存储芯片u8的第八引脚;存储芯片u8的第七引脚接地,存储芯片u8的第七引脚还耦接有第五十六电容c56,第五十六电容c56的另一端耦接于存储芯片u8的第八引脚。

48.232接口芯片u10的第一引脚耦接有第十电容c10,第十电容c10的另一端耦接于232接口芯片u10的第三引脚。232接口芯片u10的第二引脚耦接有第八电容c8,第八电容c8的另一端耦接于电源电路1以输入vdd33电压。232接口芯片u10的第四引脚耦接有第十一电容c11,第十一电容c11的另一端耦接于232接口芯片u10的第五引脚,232接口芯片u10的第六引脚耦接有第九电容c9,第九电容c9的另一端接地;232接口芯片u10的第七引脚耦接于12pin接口y4的第十一引脚,232接口芯片u10的第八引脚耦接于12pin接口y4的第十引脚;232接口芯片u10的第九引脚耦接于芯片u7的第二十一引脚,232接口芯片u10的第十引脚耦接于芯片u7的第十九引脚,232接口芯片u10的第十一引脚、第十三引脚和第十五引脚均接地,232接口芯片u10的第十六引脚耦接有第七十五电容c75,第七十五电容c75的另一端接地,232接口芯片u10的第十六引脚还耦接于电源电路1以输入vdd33电压。

49.485接口芯片u11的第一引脚耦接于芯片u7的第三十四引脚,485接口芯片u11的第三引脚耦接于第二引脚,485接口芯片u11的第二引脚耦接于芯片u7的第四十一引脚;485接口芯片u11的第四引脚耦接于芯片u7的第三十三引脚;485接口芯片u11的第五引脚接地,485接口芯片u11的第六引脚耦接有第六十五电阻r65,第六十五电阻r65的另一端耦接于9pin接口j16的第四引脚;485接口芯片u11的第七引脚耦接有第六十六电阻r66,第六十六电阻r66的另一端耦接于9pin接口j16的第三引脚,485接口芯片u11的第八引脚耦接于电源电路1以输入vcca电压,485接口芯片u11的第八引脚还耦接有第八十四电容c84,第八十四电容c84的另一端接地。

50.第一继电器k1包括八个引脚,第一继电器k1的第一引脚耦接有第十一tvs二极管tvs11,第十一tvs二极管tvs11的另一端耦接于电源电路1以输入vcca电压,第一继电器k1的第一引脚还耦接有npn型第二十三三极管q23,第二十三三极管q23的集电极耦接于第一继电器k1的第一引脚,第二十三三极管q23的发射极接地,第二十三三极管q23的基极耦接有第七十五电阻r75,第七十五电阻r75的另一端耦接于芯片u7的第二十九引脚,第一继电器k1的第五引脚和第六引脚接地,第一继电器k1的第八引脚耦接于电源电路1以输入vcca电压。

51.第二继电器k2包括八个引脚,第二继电器k2的第一引脚耦接有第十二tvs二极管tvs12,第十二tvs二极管tvs12的另一端耦接于电源电路1以输入vcca电压,第二继电器k2的第一引脚还耦接有npn型第二十二三极管q22,第二十二三极管q22的集电极耦接于第二继电器k2的第一引脚,第二十二三极管q22的发射极接地,第二十二三极管q22的基极耦接有第七十九电阻r79,第七十九电阻r79的另一端耦接于芯片u7的第三十引脚;第二继电器k2的第五引脚和第六引脚均接地,第二继电器k2的第八引脚耦接于电源电路1以输入vcca电压。

52.12pin接口y4的第二引脚耦接有第六十二电阻r62,第六十二电阻r62的另一端耦接于芯片u7的第十七引脚,12pin接口y4的第三引脚耦接于警报电路7,12pin接口y4的第四引脚接地,12pin接口y4的第五引脚耦接有防雷管gdt,防雷管gdt包括三个引脚,防雷管gdt的第二引脚耦接于12pin接口y4的第五引脚,防雷管gdt的第一引脚耦接于12pin接口y4的第六引脚,防雷管gdt的第三引脚接地。12pin接口y4的第六引脚还耦接有放电管vdr2,放电管vdr2的另一端耦接有第七十七电阻r77,第七十七电阻r77的另一端耦接于第六tvs二极管tvs6与第二tvs二极管tvs2的连接节点,第七十七电阻r77的另一端还耦接于485接口芯片u11的第七引脚。12pin接口y4的第十二引脚接地。

53.9pin接口j5的第八引脚耦接于电源电路1以输入v_wifi电压,9pin接口j5的第六引脚、第七引脚和第九引脚均接地。9pin接口j16的第一引脚、第二引脚和第八引脚均接地,9pin接口j16的第七引脚耦接于电源电路1以输入vcca电压。

54.参照图5,锁相环电路4包括型号为lmx2325的芯片u1和压腔震荡器u20,压腔震荡器u20包括六个引脚,芯片u1包括二十个引脚,芯片u1的第一引脚为震荡输入端,芯片u1的第六引脚为颞部电荷泵输出端,芯片u1的第五引脚为电源端,芯片u1的第十一引脚、第十三引脚、第十四引脚和第十九引脚为锁相控制信号输入端。芯片u1的第一引脚耦接于芯片u7的第六十三引脚,芯片u1的第四引脚耦接于第五引脚,芯片u1的第五引脚耦接有第四十五电阻r45,第四十五电阻r45的另一端耦接于电源电路1以输入pllvcc电压,第四十五电阻r45与芯片u1的第五引脚的连接节点耦接有第七十九电容c79,第七十九电容c79的另一端接地。芯片u1的第六引脚耦接有第二十九电阻r29,第二十九电阻r29的另一端偶额基有第三十电阻r30,第三十电阻r30的另一端耦接于压腔震荡器u20的第一引脚,第二十九电阻r29与芯片u1的第六引脚的连接节点耦接有第三十三电容c33,第三十三电容c33的另一端接地;第二十九电阻r29与第三十三电容c33的连接节点耦接有第三十一电阻r31,第三十一电阻r31的另一端耦接有第三十二电容c32,第三十二电容c32的另一端接地;第二十九电阻r29与第三十电阻r30的连接节点耦接有第三十电容c30,第三十电容c30的另一端接地;第三十电阻r30与压腔震荡器u20的第一引脚的连接节点耦接有第三十一电容c31,第三十一电容c31的另一端接地。芯片u1的第七引脚接地,芯片u1的第十引脚耦接有第六十一电容c61,第六十一电容c61的另一端耦接有第四十四电阻r44,第四十四电阻r44的另一端耦接于压腔震荡器u20的第四引脚;第六十一电容c61与第四十四电阻r44的连接节点耦接有第五十一电容c51,第五十一电容c51的另一端接地。芯片u1的第十一引脚耦接于第二反相器u21的第八引脚,芯片u1的第十三引脚耦接于第二反相器u21的第六引脚,芯片u1的第十四引脚耦接于第二反相器u21的第十二引脚,芯片u1的第十九引脚耦接于第二反相器u21的第十引脚。

55.压腔震荡器u20的第二引脚接地,压腔震荡器u20的第三引脚耦接有第六十二电容c62,第六十二电容c62的另一端接地,压腔震荡器u20的第三引脚还耦接于电源电路1以输入pllvcc电压,压腔震荡器u20的第五引脚和第六引脚均接地。压腔震荡器u20的第四引脚耦接有第二十电阻r20,压腔震荡器u20的第四引脚与第二十电阻r20的连接节点耦接有第二十一电阻r21,第二十一电阻r21的另一端接地,第二十电阻r20的另一端耦接有第二十电容c20,第二十电阻r20与第二十电容c20的连接节点耦接有第二十二电阻r22,第二十二电阻r22的另一端接地,第二十电容c20的另一端耦接于功放电路5。

56.参照图6,功放电路5包括型号为rpg5110g的芯片u12和射频开关二极管e4,芯片u12包括十六个引脚,芯片u12的第一引脚为电源输入端,芯片u12的第三引脚为射频输入端,芯片u12的第九引脚至第十二引脚为射频输出端。芯片u12的第一引脚耦接有第四电感l4,第四电感l4的另一端耦接于电源电路1以输入pa_vcc电压,芯片u12的第三引脚耦接有第八十五电容c85和第二十四电阻r24,第二十电阻r24与第八十五电容c85串联,第二十四电阻r24的另一端耦接于射频开关管e4,射频开关管e4的另一端分别耦接于锁相环电路4和第一反相器u13的第四引脚。芯片u12的第五引脚耦接有第八十五电阻r85,第八十五电阻r85的另一端耦接于电源电路1以输入pa_vcc电压,芯片u12的第六引脚耦接于第五引脚,芯片u12的第八引脚耦接有第一百电容c100,第一百电容c100的另一端接地。芯片u12的第九引脚、第十引脚、第十一引脚和第十二引脚相互并联,芯片u12的第十二引脚耦接有第十三电感l13,第十三电感l13的另一端耦接有第四十三电容c43,第四十三电容c43的另一端耦接于天线传输电路3。芯片u12的第十四引脚耦接于电源电路1以输入pa_vcc电压,芯片u12的第十五引脚耦接于第十六引脚,芯片u12的第十六引脚耦接有第八十三电阻r83,第八十三电阻r83的另一端耦接于vapc电压。

57.参照图7,差分放大电路6包括检波子电路61和三级放大子电路62,检波子电路61包括npn型第四三极管q4、npn型第五三极管q5、第三十五电容c35、第三十七电容c37、第三十八电容c38、第三十九电容c39、第四十电容c40、第四十一电容c41、第四十二电容c42、第四十九电容c49、电阻cd01、电阻cd02、第三电感l3、第五电感l5、第六电感l6、第七电感l7、第三十六电阻r36和第三十七电阻r37。第四三极管q4的基极耦接于电阻cd01,第四三极管q4的集电极耦接于第三十九电容c39,第三十九电容c39的另一端耦接于芯片u3的第十一引脚,第四三极管q4的发射极耦接于第六电感l6,第六电感l6的另一端耦接于第三十七电容c37,第三十七电容c37与第六电感l6的连接节点耦接于第三十八电容c38和第三十六电阻r36,第三十八电容c38的另一端接地,第三十六电阻r36的另一端接地,第三十七电容c37的另一端耦接于第三电感l3,第三十五电容c35耦接于第三十七电容c37与第三电感l3的连接节点,第三电感l3的另一端耦接于三级放大子电路62。

58.第五三极管q5的集电极耦接于第四十电容c40,第四十电容c40的另一端耦接于芯片u3的第十一引脚,第五三极管q5的发射极耦接于第七电感l7,第七电感l7的另一端耦接于第四十一电容c41,第四十一电容c41与第七电感l7的连接节点耦接于第四十二电容c42和第三十七电阻r37,第四十二电容c42的另一端接地,第三十七电阻r37的另一端接地,第四十一电容c41的另一端耦接于第五电感l5,第四十九电容c49耦接于第四十一电容c41与第五电感l5的连接节点,第五电感l5的另一端耦接于三级放大子电路62。

59.三级放大子电路62包括三个放大单元,第一放大单元621包括npn型第一三极管q1、pnp型第六三极管q6、npn型第七三极管q7、npn型第八三极管q8、npn型第九三极管q9、第八电阻r8、第九电阻r9、第十电阻r10、第十一电阻r11、第三十九电阻r39、第四十一电阻r41、第四十六电阻r46、第四十八电阻r48、第五十五电阻r55、第十三电容c13、第十四电容c14、第十九电容c19、第二十六电容c26、第三十四电容c34、第三十六电容c36、第五十三电容c53、第五十四电容c54、第七十八电容c78和第八十电容c80。第一三极管q1的基极耦接于第四十八电阻r48,第四十八电阻r48的另一端耦接于检波子电路61,第四十八电阻r48的另一端还耦接于第三十六电容c36,第三十六电容c36另一端接地;第一三极管q1的基极还耦

接于第五十四电容c54,第五十四电容c54的另一端接地,第五十四电容c54与第一三极管q1的基极连接节点耦接于第四十六电阻r46,第四十六电阻r46的另一端耦接于第五十三电容c53,第五十三电容c53的另一端接地,第五十三电容c53与第四十六电阻r46的连接节点耦接于5v电压。第一三极管q1的发射极分别耦接于第七三极管q7的基极和第八三极管q8的基极,第七三极管q7的集电极耦接于第七三极管q7的基极,第七三极管q7的发射极第八三极管q8的发射极均接地。第九三极管q9的基极耦接于检波子电路61,第三十四电容c34的一端耦接于第九三极管q9的基极,第三十四电容c34的另一端接地,第五十五电阻r55的一端耦接于第九三极管q9的基极,第五十五电阻r55的另一端耦接于第一三极管q1的基极。第九三极管q9的集电极耦接于第八电阻r8,第八电阻r8的另一端耦接于第十一电阻r11,第十一电阻r11的另一端耦接于5v电压;第九三极管q9的发射极耦接于第八三极管q8的集电极,第六三极管q6的基极耦接于检波子电路61,第六三极管q6的发射极耦接于第八三极管q8的集电极,第六三极管q6的集电极耦接于第十九电容c19,第十九电容c19的另一端耦接于第三十九电阻r39,第三十九电阻r39的另一端耦接于第二放大单元622;第十电阻r10与第十三电容c13串联,第十电阻r10的另一端耦接于第九三极管q9的集电极,第十三电容c13的另一端耦接于第六三极管q6的集电极;第十四电容c14的一端耦接于第九三极管q9的集电极,第十四电容c14的另一端耦接于第六三极管q6的集电极;第二十六电容c26与第四十一电阻r41串联,第二十六电容c26的另一端耦接于第九三极管q9的集电极,第四十一电阻r41的另一端耦接于第二放大单元622;第九电阻r9的一端耦接于第八电阻r8,第九电阻r9的另一端耦接于第六三极管q6的集电极,第七十八电容c78的一端耦接于第八电阻r8与第十一电阻r11的连接节点,第八十电容c80的一端耦接于第十一电阻r11,第七十八电容c78的另一端和第八十电容c80的另一端局接地。

60.第二放大单元622包括npn型第二三极管q2、npn型第十三极管q10、npn型第十一三极管q11、npn型第十二三极管q12、pnp型第十三三极管q13、第十二电阻r12、第十三电阻r13、第十四电阻r14、第十五电阻r15、第三十五电阻r35、第四十电阻r40、第四十九电阻r49、第五十电阻r50、第五十四电阻r54、第十七电容c17、第十八电容c18、第二十五电容c25、第二十七电容c27、第五十五电容c55、第五十七电容c57、第七十电容c70和第七十七电容c77。第二三极管q2的基极耦接于第五十电阻r50,第五十电阻r50的另一端耦接于第四十一电阻r41,第五十四电阻r54、第五十五电容c55和第五十七电容c57串联,第五十四电阻r54与第五十七电容c57的连接节点耦接于第二三极管q2的基极,第五十四电阻r54与第五十五电容c55的连接节点耦接于5v电压,第五十五电容c55的另一端和第五十七电容c57的另一端均接地,第二三极管q2的发射极耦接于第十三极管q10的基极和集电极,第十三极管q10的发射极接地,第十三极管q10的集电极耦接于第十二三极管q12的基极,第十二三极管q12的发射极接地,第十一三极管q11的基极耦接于第一放大单元621,第十一三极管q11的发射极耦接于第十二三极管q12的集电极,第十一三极管q11的集电极耦接于第十三电阻r13和第十五电阻r15,第十三电阻r13与第十五电阻r15串联,第十五电阻r15的另一端耦接于5v电压。第十三三极管q13的基极耦接于第一放大单元621,第十三三极管q13的发射极耦接于第十二三极管q12的集电极,第十三三极管q13的集电极与第二十五电容c25和第四十电阻r40串联后耦接于第三放大单元623。第十七电容c17与第十四电阻r14串联,第十七电容c17的另一端耦接于第十一三极管q11的集电极,第十四电阻r14的另一端耦接于第十三

三极管q13的集电极,第十八电容c18的一端接于第十一三极管q11的集电极,第十八电容c18的另一端第十三三极管q13的集电极,第二十七电容c27与第三十五电阻r35串联,二十七电容c27的另一端耦接于第十一三极管q11的集电极,第三十五电阻r35的另一端耦接于第三放大单元623。

61.第三放大单元623包括npn型第三三极管q3、npn型第十四三极管q14、npn型第十五三极管q15、npn型第十六三极管q16和pnp型第十七三极管q17、第十六电阻r16、第十七电阻r17、第十八电阻r18、第十九电阻r19、第二十八电阻r28、第五十一电阻r51、第五十二电阻r52、第五十三电阻r53、第六十三电阻r63、第二十一电容c21、第二十二电容c22、第二十八电容c28、第五十八电容c58、第五十九电容c59、第六十三电容c63和第六十四电容c64。第三三极管q3的基极耦接于第五十二电阻r52,第五十二电阻r52的另一端耦接于第二放大单元622,第五十八电容c58、第五十三电阻r53与第五十九电容c59串联,第五十八电容c58与第五十三电阻r53的连接节点耦接于第三三极管q3的基极,第五十三电阻r53与第五十九电容c59的连接节点耦接于5v电压。第三三极管q3的发射极耦接于第十四三极管q14的基极和集电极,第十四三极管q14的发射极接地,第三三极管q3的发射极还耦接于第十六三极管q16的基极,第十六三极管q16的发射极接地。第十五三极管q15的基极耦接于第二放大单元622,第十五三极管q15的发射极耦接于第十六三极管q16的集电极,第十五三极管q15的集电极与第十七电阻r17和第十九电阻r19串联,第十九电阻r19的另一端耦接于5v电压;第十七三极管q17的基极与第五十一电阻r51串联后耦接于第三三极管q3的基极,第十七三极管q17的基极还耦接于第二放大单元622,第十七三极管q17的发射极耦接于第十六三极管q16的集电极,第十七三极管q17的集电极耦接于第十六电阻r16,第十六电阻r16的另一端耦接于第十七电阻r17与第十九电阻r19的连接节点;第二十一电容c21与第十八电阻r18串联,第二十一电容c21的另一端耦接于第十五三极管q15的集电极,第十八电阻r18的另一端耦接于第十七三极管q17的集电极,第二十二电容c22的一端耦接于第十五三极管q15的集电极第二十二电容c22的,另一端耦接于第十七三极管q17的集电极,第二十八电容c28与第二十八电阻r28串联,第二十八电容c28的另一端耦接于第十五三极管q15的集电极,第二十八电阻r28的另一端接地,第二十八电阻r28与第二十八电容c28的连接节点耦接于微控制电路2的第一反相器u13的第五引脚。

62.本技术实施例一种门禁系统的实施原理为:

63.电源电路1给智锂狗门禁系统的读写器提供工作电压,微控制电路2发送控制指令至锁相环电路4,锁相环电路4接收到控制指令后,使锁相环锁定震荡频率,震荡频率锁定后,微控制电路2发送调制信号至功放电路5,功放电路5接收经过调制的震荡频率并对其进行功率放大处理且输出至天线传输电路3,天线传输电路3输出寻标签指令载波信号,当贴有电子标签的电动自行车进入到安检区域时,天线传输电路3接收电子标签激活后的反射信号并输出至差分放大电路6,差分放大电路6对反射信号进行放大滤波整形处理并输出至微控制电路2,微控制电路2接收到放大处理后的信号后进行解码并输出启动信号至警报电路7,警报电路7启动输出警报信号,实现监管电动自行车,防止电动自行车违规入户进行充电,预防安全事故发生。

64.以上均为本技术的较佳实施例,并非依此限制本技术的保护范围,故:凡依本技术的结构、形状、原理所做的等效变化,均应涵盖于本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1