设计电路的方法以及静态随机存取存储器器件与流程

1.本发明的实施例设计设计电路的方法以及静态随机存取存储器器件。

背景技术:

2.半导体集成电路(ic)行业经历了快速增长。ic材料和设计方面的技术进步已产生了几代ic,其中每一代都比前一代具有更小、更复杂的电路。然而,这些优势增加了加工和制造ic的复杂性,为实现这些优势,在ic加工和制造方面需要进行相似的发展。在ic发展的主流过程中,功能密度(即,每个芯片区互连器件的数量)已普遍增加,而几何尺寸(即,可使用制造工艺创建的最小元件)已减小。但这种主流发展需要通过在设施建立上进行巨额投资来遵循摩尔法则。因此,一直需要开发具有更小芯片面积、更低成本和更低漏电流的ic。

技术实现要素:

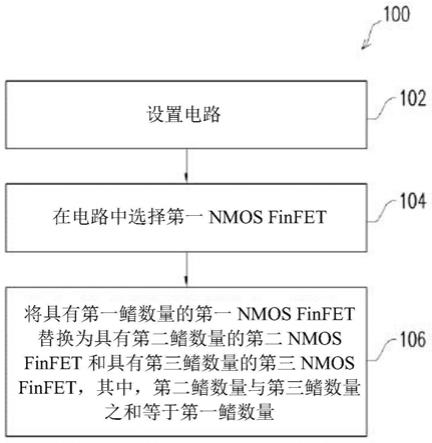

3.根据本发明实施例的一个方面,提供了一种设计电路的方法,包括:设置电路;选择电路中的第一nmos鳍式场效应晶体管(finfet);以及将具有第一鳍数量的第一nmos finfet替换为具有第二鳍数量的第二nmos finfet和具有第三鳍数量的第三nmos finfet,其中,第二鳍数量与第三鳍数量之和等于第一鳍数量。

4.根据本发明实施例的另一个方面,提供了一种设计电路的方法,包括:设置电路;选择电路中的第一pmos finfet和第二pmos finfet;以及将具有第一鳍数量的第一pmos finfet和具有第二鳍数量的第二pmos finfet替换为具有第三鳍数量的第三pmos finfet,其中,第一鳍数量与第二鳍数量之和等于第三鳍数量。

5.根据本发明实施例的又一个方面,提供了一种静态随机存取存储器器件,包括:存储器单元,包括:第一反相器;第二反相器,与第一反相器交叉耦合;第一存取晶体管,连接在第一反相器的第一数据节点和第一位线之间;第二存取晶体管,连接在第二反相器的第二数据节点和第二位线之间;写驱动器,包括:第一pmos finfet,具有与第一电力端子耦合的第一源极/漏极端子;第二pmos finfet,具有与第一pmos finfet的第二源极/漏极端子耦合的第一源极/漏极端子以及与第一位线耦合的栅极端子;第三pmos finfet,具有与第一电力端子耦合的第一源极/漏极端子;第四pmos finfet,具有与第三pmos finfet的第二源极/漏极端子耦合的第一源极/漏极端子以及与第二位线耦合的栅极端子;第一和第二nmos finfet,并联连接在第二pmos finfet的第二源极/漏极端子与第二电力端子之间,其中,第一pmos finfet的栅极端子以及第一nmos finfet和第二nmos finfet的栅极端子被连接,以接收第一写信号;第三和第四nmos finfet,并联连接在第四pmos finfet的第二源极/漏极端子以及第二电力端子之间,其中,第三pmos finfet的栅极端子以及第三和第四nmos finfet的栅极端子被连接,以接收第二写信号。

附图说明

6.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各方面。应该注意,

根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。另外,附图是说明性的,作为本发明的实施例的实例,并且不意图是限制性的。

7.图1是图示了按照一些实施例的示例方法的流程图。

8.图2a是图示了按照一些实施例的使用图1的方法进行的nmos鳍式场效应晶体管(finfet)的替换的示意图。

9.图2b是图示了按照一些实施例的使用图1的方法进行的nmos finfet的另一替换的示意图。

10.图3是图示了按照一些实施例的示例方法的流程图。

11.图4a是图示了按照一些实施例的使用图3的方法进行的pmos finfet的替换的示意图。

12.图4b是图示了按照一些实施例的使用图3的方法进行的pmos finfet的另一替换的示意图。

13.图5是图示了按照一些实施例的示例方法的流程图。

14.图6是图示了按照一些实施例的使用图5的方法进行的nmos finfet和多个pmos finfet的替换的示意图。

15.图7a是按照一些实施例的可以应用图5的方法的静态随机存取存储器(sram)器件的示意图。

16.图7b是图示了按照一些实施例的图5的方法的应用的示意图。

17.图7c是图示了按照一些实施例的与图7b对应的布局的示意图。

18.图7d是图示了按照一些实施例的图5的方法的应用的示意图。

19.图7e是图示了按照一些实施例的与图7d对应的布局的示意图。

20.图8是图示了按照一些实施例的应用图5的方法的包括反相器的电路的示意图。

21.图9是图示了按照一些实施例的应用图5的方法的包括字线驱动器的存储器件电路的示意图。

22.图10是图示了按照一些实施例的应用图5的方法的包括行解码器驱动器或列解码器驱动器的存储器件电路的示意图。

具体实施方式

23.以下公开内容提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可在各个实例中重复参考标号和/或字符。该重复是为了简单和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

24.而且,为了便于描述,在此可以使用诸如“在

…

之下”、“在

…

下方”、“下部”、“在

…

之上”、“上部”等空间相对术语,以描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的

不同方位。器件可以以其他方式定向(旋转90度或在其他方位上),而本文使用的空间相对描述符可以同样地作出相应的解释。

25.随着集成电路(ic)尺寸的减小,要费力克服这种尺寸减小所面临的问题。例如,鳍式场效应晶体管(finfet)的包括漏电流的性能因沟道长度的减小而劣化。诸如finfet之类的垂直半导体器件是半导体衬底表面上的三维结构。鳍从衬底的主体向上延伸,并且可以通过在衬底上沉积鳍材料、蚀刻衬底的非鳍区域或其组合来形成。finfet的沟道形成在该垂直鳍中,栅极设置在鳍上方(例如,包裹鳍)。将栅极包裹在鳍上增加了沟道区域与栅极之间的接触面积,并使栅极能够从两侧控制沟道。随着集成电路器件变小,器件之间的间隔或“间距”可能导致相邻器件之间有电磁干扰。因此,期望的是改善finfet的性能的新型方法和结构。具体地,电路设计者可以基于最小器件指和总鳍数量考虑来在高级finfet技术节点(例如,n10、n7、n5等)上实现电路设计。对于低功耗应用,如果电路设计中使用了错误的pmos或nmos鳍尺寸,则电路漏电流将更高。

26.按照一些实施例,提供了用于finfet半导体器件分组的方法。通常,对某些器件应用最佳的鳍分组设计,以在相同的饱和电流(idsat)速度操作中实现较低的漏电流(ioff)。具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比(saturation

‑

to

‑

leakage ratio),而具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。通过交换基于pmos和nmos属性的鳍尺寸选择,将使电路漏电流减小。在以下讨论的一些实施例中,在相同饱和电流速度操作中,通过交换鳍尺寸选择而不进行任何附加电路改变,可以使漏电流减小超过5%

‑

10%。

27.具体地,finfet具有与finfet的转动速度关联的饱和电流(idsat)和finfet的截止状态下的漏电流(ioff)。finfet的不同鳍尺寸可以造成不同的饱和

‑

漏比(idsat/ioff)特性,因为不同的鳍尺寸具有不同的包括压应力和拉应力的隔离应力,以下将对此进行详细描述。

28.对于n型finfet(也称为“nmos finfet”,本文可互换地使用),nmos finfet的源极/漏极可以包含拉应力材料。拉应力是所施加负荷引起的往往会使材料沿着施加负荷的轴线伸长的应力状态,换句话说,是通过拉动材料引起的应力。承受张力的截面面积相等的结构的强度与截面的形状无关。在一些实施例中,拉应力材料可以是与硅相比具有较小晶格常数的材料(例如,硼)。拉应力材料可以通过向nmos finfet的鳍结构施加拉应力来改善沟道区域中载流子的迁移率(即,nmos finfet的电子迁移率)。结果,具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比,因此在相同饱和电流条件下具有较低的漏电流。

29.另一方面,对于p型finfet(也称为“pmos finfet”,本文可互换地使用),pmos finfet的源极/漏极可以包含压应力材料。压应力(或压缩)是所施加负荷引起的作用于沿着所施加负荷的轴线减小材料(压缩构件)的长度的长度的应力状态,换句话说,它是引起该材料挤压的应力状态。在一些实施例中,压应力材料可以是与硅相比具有大晶格常数的材料(例如,硅

‑

锗)。压应力材料可以通过向pmos finfet的鳍结构施加压应力来改善沟道区域中载流子的迁移率(即,pmos finfet的空穴迁移率)。因此,具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比,因此在相同饱和电流条件下具有较低的漏电流。

30.如此,期望的是nmos finfet具有较小的鳍尺寸而pmos finfet具有较大的鳍尺寸,以便在相同饱和电流条件下具有较低的漏电流。因此,通过将一个具有大鳍尺寸(例如,3个鳍)的nmos finfet分解为多个具有较小鳍尺寸的nmos finfet(例如,一个具有2个鳍而另一个具有1个鳍),将使漏电流减小。该方法可以在电路设计期间应用于电路中的任何nmos finfet,以下将参考图1描述细节。另一方面,通过将多个鳍尺寸小的pmos finfet(例如,一个具有2个鳍而另一个具有1个鳍)分组为1个鳍尺寸较大的pmos finfet(例如,3个鳍),漏电流将减小。该方法可以在电路设计期间应用于电路中的任何nmos finfet,以下将参考图3描述细节。

31.图1是图示了按照一些实施例的示例方法100的流程图。在图1中示出的示例中,方法从步骤102开始,在步骤102中,设置电路。该电路可以是包括nmos finfet的任何电路。在一些非限制示例中,该电路是处理连续模拟信号的模拟电路。例如,模拟电路可以包括以下中的至少一种:差分放大器、运算放大器(op amp)、射频(rf)放大器、比较器、电流镜、模拟乘法器、模拟分频器、模数转换器(adc)、数模转换器(dac)、压控振荡器(vco)、i/q调制器和模拟开关多路复用器等。另一方面,在一些非限制示例中,该电路是处理离散数字信号的数字电路。例如,数字电路可以包括以下中的至少一种:逻辑与(and)门、逻辑与(and)门、反相器、逻辑与非(nand)门、逻辑或非(nor)门、触发器、多路复用器(即,数据选择器)、同步时序逻辑电路、异步时序逻辑电路等。

32.然后,方法100进行至步骤104,在步骤104中,选择第一nmos finfet。尽管理论上可以选择电路中的任何nmos finfet,但第一nmos finfet常常是基于与第一nmos finfet的饱和电流(idsat)和漏电流(ioff)关联的考虑因素来选择的。例如,第一nmos finfet可以是静态随机存取存储器(sram)器件的写驱动器中的nmos finfet(将在下面参考图7a描述其细节),因为写驱动器中的nmos finfet的漏电流对sram器件的总泄漏有显著贡献。应该注意,也可以选择电路中的除了第一nmos finfet以外的nmos finfet。换句话说,可以在步骤104中选择电路中的多个nmos finfet。

33.然后,方法100进行至步骤106,在步骤106中,第一nmos finfet被替换为第二nmos finfet和第三nmos finfet。具体地,第一nmos finfet具有第一鳍数量,第二nmos finfet具有第二鳍数量并且第三nmos finfet具有第三鳍数量。鳍数量越大,整体鳍结构越宽。第一鳍数量等于第二鳍数量与第三鳍数量之和。如此,替换后整体鳍结构的宽度不变。然而,第二nmos finfet与第三nmos finfet的总漏电流小于第一nmos finfet的漏电流,因为具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。

34.图2a是图示了按照一些实施例的使用图1的方法100进行的nmos finfet的替换的示意图。图2b是图示了按照一些实施例的使用图1的方法100进行的nmos finfet的另一替换的示意图。如图2a和图2b中所示,在图1中示出的步骤104中选择在电路209中的nmos finfet nm1。nmos finfet nm1具有栅极g1、源极s1和漏极d1。具体地,nmos finfet nm1具有3个鳍(即,栅极结构在三个平行鳍结构的上方并控制这3个鳍结构)。在图1中示出的步骤106中,nmos finfet nm1被替换为nmos finfet nm2和nmos finfet nm3。具体地,nmos finfet nm2具有1个鳍,而nmos finfet nm3具有2个鳍。nmos finfet nm2具有栅极g1、源极s1和漏极d1;nmos finfet nm3也具有栅极g1、源极s1和漏极d1。换句话说,nmos finfet nm2和nm3的栅极、源极和漏极被分别连接。如此,在图1中示出的步骤106中进行替换之后,

对应于整体鳍尺寸的总鳍数量是不变的(即,二者都是3个)。然而,nmos finfet nm2和nm3的总漏电流小于nmos finfet nm1的漏电流,因为具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。如此,在图1中示出的步骤106中进行替换之后,总漏电流减小。

35.可选地,如图2b中所示,nmos finfet nm1被替换为nmos finfet nm4、nmos finfet nm5和nmos finfet nm6。具体地,nmos finfet nm4具有1个鳍,nmos finfet nm5具有1个鳍并且nmos finfet nm6具有1个鳍。nmos finfet nm4具有栅极g1、源极s1和漏极d1;nmos finfet nm5也具有栅极g1、源极s1和漏极d1;nmos finfet nm6也具有栅极g1、源极s1和漏极d1。换句话说,nmos finfet nm4、nm5和nm6的栅极、源极和漏极被分别连接。如此,在图1中示出的步骤106中进行替换之后,对应于整体鳍尺寸的总鳍数量是不变的(即,二者都是3个)。然而,nmos finfet nm4、nm5和nm6的总漏电流小于nmos finfet nm1的漏电流,因为具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。如此,在图1中示出的步骤106中进行替换之后,总漏电流减小。

36.应该注意,方法100可以应用于电路中的任何nmos finfet并且图2a和图2b只是示例。在一个示例中,具有2个鳍的nmos finfet可以被替换为其中每个都具有1个鳍的两个nmos finfet。在一个示例中,具有4个鳍的nmos finfet可以被替换为:(1)其中每个都具有1个鳍的四个nmos finfet;(2)具有2个鳍的nmos finfet和其中每个都具有1个鳍的两个nmos finfet;(3)具有3个鳍的nmos finfet和具有1个鳍的nmos finfet;以及(4)其中每个都具有2个鳍的两个nmos finfet。在一个示例中,具有5个鳍的nmos finfet可以被替换为:(1)其中每个都具有1个鳍的五个nmos finfet;(2)具有2个鳍的nmos finfet和其中每个都具有1个鳍的三个nmos finfet;(3)具有3个鳍的nmos finfet和其中每个都具有1个鳍的两个nmos finfet;(4)具有4个鳍的nmos finfet和具有1个鳍的nmos finfet;(5)具有1个鳍的nmos finfet和其中每个都具有2个鳍的两个nmos finfet;以及(6)具有2个鳍的nmos finfet和具有3个鳍的nmos finfet。同样,图1中示出的该方法100可以应用于具有n个鳍的nmos finfet,其中,n是大于1的整数。如模拟结果所示,通过实现如图1中所示的方法100,在以下条件下:使用典型工艺;在0.75v下操作;在85℃的温度下,对于标准电压(例如,200mv)、低压(例如,150mv)和超低压(例如,100mv),漏电流可以分别降低7

‑

20%、10

‑

25%和10

‑

25%。

37.图3是图示了按照一些实施例的示例方法300的流程图。在图3中示出的示例中,方法300从步骤302开始,在步骤302中,设置电路。该电路可以是包含pmos finfet的任何电路。在一些非限制示例中,该电路是处理连续模拟信号的模拟电路。例如,模拟电路可以包括以下中的至少一种:差分放大器、运算放大器(op amp)、射频(rf)放大器、比较器、电流镜、模拟乘法器、模拟分频器、模数转换器(adc)、数模转换器(dac)、压控振荡器(vco)、i/q调制器和模拟开关多路复用器等。另一方面,在一些非限制示例中,该电路是处理离散数字信号的数字电路。例如,数字电路可以包括以下中的至少一种:逻辑and门、逻辑or门、反相器、逻辑nand门、逻辑nor门、触发器、多路复用器(即,数据选择器)、同步时序逻辑电路、异步时序逻辑电路等。

38.然后,方法300进行至步骤304,在步骤304中,选择电路中的第一pmos finfet和第二pmos finfet。尽管理论上可以选择电路中的任何两个pmos finfet,但第一pmos finfet

和第二pmos finfet常常是基于与第一pmos finfet和第二pmos finfet的饱和电流(idsat)和漏电流(ioff)关联的考虑因素来选择的。例如,第一pmos finfet和第二pmos finfet可以是sram器件的头部单元中的pmos finfet(将在下面参考图7a描述其细节),因为头部单元中的该pmos finfet的漏电流对sram器件的总泄漏有显著贡献。应该注意,除了第一pmos finfet和第二pmos finfet之外,还可以选择电路中的除了第一pmos finfet和第二pmos finfet以外的pmos finfet。换句话说,在步骤304中,可以选择电路中的不止两个(例如,四个)pmos finfet。

39.然后,方法300进行至步骤306,在步骤306中,第一pmos finfet和第二pmos finfet被替换为第三pmos finfet。具体地,第一pmos finfet具有第一鳍数量,第二pmos finfet具有第二鳍数量并且第三pmos finfet具有第三鳍数量。鳍数量越大,整体鳍结构越宽。第三鳍数量等于第一鳍数量与第二鳍数量之和。如此,替换后整体鳍结构的宽度不变。然而,第三pmos finfet的漏电流小于第一pmos finfet和第二pmos finfet的总漏电流,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比。

40.图4a是图示了按照一些实施例的使用图3的方法300进行的pmos finfet的替换的示意图。图4b是图示了按照一些实施例的使用图3的方法300进行的pmos finfet的另一替换的示意图。如图4a中所示,在图3中示出的步骤304中,选择在电路490中的两个pmos finfet pm1和pm2。具体地,pmos finfet pm1具有1个鳍(即,栅极结构在一个鳍结构的上方并控制该鳍结构),而pmos finfet pm2具有2个鳍(即,栅极结构在两个鳍结构的上方并控制这2个鳍结构)。pmos finfet pm1具有栅极g2、源极s2和漏极d2;pmos finfet pm2具有栅极g2、源极s2和漏极d2。换句话说,pmos finfet pm1和pm2的栅极、源极和漏极被分别连接。在图3中示出的步骤306中,pmos finfet pm1和pm2被替换为pmos finfet pm3。具体地,pmos finfet pm3有3个鳍。pmos finfet pm3具有栅极g2、源极s2和漏极d2。如此,在图3中示出的步骤306中进行替换之后,对应于整体鳍尺寸的总鳍数量是不变的(即,二者都是3个)。然而,pmos finfet pm3的漏电流小于pmos finfet pm1与pmos finfet pm2的总漏电流,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比。如此,在图3中示出的步骤306中进行替换之后,总漏电流减小。

41.可选地,如图4b中所示,在图3中示出的步骤304中,选择在电路490中的三个pmos finfet pm4、pm5和pm6。具体地,pmos finfet pm4具有1个鳍,pmos finfet pm5具有1个鳍并且pmos finfet pm6具有1个鳍。pmos finfet pm4具有栅极g2、源极s2和漏极d2;pmos finfet pm5也具有栅极g2、源极s2和漏极d2;pmos finfet pm6也具有栅极g2、源极s2和漏极d2。换句话说,pmos finfet pm4、pm5和pm6的栅极、源极和漏极被分别连接。在图3中示出的步骤306中,pmos finfet pm4、pm5和pm6被替换为pmos finfet pm3。具体地,pmos finfet pm3有3个鳍。pmos finfet pm3具有栅极g2、源极s2和漏极d2。如此,在图3中示出的步骤306中进行替换之后,对应于整体鳍尺寸的总鳍数量是不变的(即,二者都是3个)。然而,pmos finfet pm3的漏电流小于pmos finfet pm4、pmos finfet pm5和pmos finfet pm6的总漏电流,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比。如此,在图3中示出的步骤306中进行替换之后,总漏电流减小。

42.应该注意,方法300可以应用于电路中的任何pmos finfet,并且图4a和图4b只是示例。在一个示例中,具有2个鳍的pmos finfet可以被用于替换两个pmos finfet,并且其

中每个都具有1个鳍。在一个示例中,具有4个鳍的pmos finfet可以被用于替换:(1)其中每个都具有1个鳍的四个pmos finfet;(2)具有2个鳍的pmos finfet和其中每个都具有1个鳍的两个pmos finfet;(3)具有3个鳍的pmos finfet和具有1个鳍的pmos finfet;以及(4)其中每个都具有2个鳍的两个pmos finfet。在一个示例中,具有5个鳍的pmos finfet可以被用于替换:(1)其中每个都具有1个鳍的五个pmos finfet;(2)具有2个鳍的pmos finfet和其中每个都具有1个鳍的三个pmos finfet;(3)具有3个鳍的pmos finfet和其中每个都具有1个鳍的两个pmos finfet;(4)具有4个鳍的pmos finfet和具有1个鳍的pmos finfet;(5)具有1个鳍的pmos finfet和其中每个都具有2个鳍的两个pmos finfet;以及(6)具有2个鳍的pmos finfet和具有3个鳍的pmos finfet。同样,图3中示出的该方法300可以应用于总鳍数量为n的多个pmos finfet,其中,n是大于1的整数。如模拟结果所示,通过实现如图1中所示的方法100,在以下条件下:使用典型工艺;在0.75v下操作;在85℃的温度下,对于标准电压(例如,200mv)、低压(例如,150mv)和超低压(例如,100mv),漏电流可以分别降低7

‑

20%、10

‑

25%和10

‑

25%。

43.图5是图示了按照一些实施例的示例方法500的流程图。通常,方法500可以被视为图1中示出的方法100与图3中示出的方法300的组合。在图5中示出的示例中,方法500从步骤502开始,在步骤502中,设置电路。该电路可以是包括nmos finfet和pmos finfet二者的任何电路。在一些非限制示例中,该电路是处理连续模拟信号的模拟电路。例如,模拟电路可以包括以下中的至少一种:差分放大器、运算放大器(op amp)、射频(rf)放大器、比较器、电流镜、模拟乘法器、模拟分频器、模数转换器(adc)、数模转换器(dac)、压控振荡器(vco)、i/q调制器和模拟开关多路复用器等。另一方面,在一些非限制示例中,该电路是处理离散数字信号的数字电路。例如,数字电路可以包括以下中的至少一种:逻辑and门、逻辑or门、反相器、逻辑nand门、逻辑nor门、触发器、多路复用器(即,数据选择器)、同步时序逻辑电路、异步时序逻辑电路等。

44.然后,方法500进行至步骤504,在步骤504中,选择第一nmos finfet。尽管理论上可以选择电路中的任何nmos finfet,但第一nmos finfet常常是基于与第一nmos finfet的饱和电流(idsat)和漏电流(ioff)关联的考虑因素来选择的。例如,第一nmos finfet可以是静态随机存取存储器(sram)器件的写驱动器中的nmos finfet(将在下面参考图7a描述其细节),因为写驱动器中的nmos finfet的漏电流对sram器件的总泄漏有显著贡献。应该注意,也可以选择电路中的除了第一nmos finfet以外的nmos finfet。换句话说,可以在步骤504中选择电路中的多个nmos finfet。

45.然后,方法500进行至步骤506,在步骤506中,第一nmos finfet被替换为第二nmos finfet和第三nmos finfet。具体地,第一nmos finfet具有第一鳍数量,第二nmos finfet具有第二鳍数量并且第三nmos finfet具有第三鳍数量。鳍数量越大,整体鳍结构越宽。第一鳍数量等于第二鳍数量与第三鳍数量之和。如此,替换后整体鳍结构的宽度不变。然而,第二nmos finfet与第三nmos finfet的总漏电流小于第一nmos finfet的漏电流,因为具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。

46.然后,方法500进行至步骤508,在步骤508中,选择电路中的第一pmos finfet和第二pmos finfet。尽管理论上可以选择电路中的任何两个pmos finfet,但第一pmos finfet和第二pmos finfet常常是基于与第一pmos finfet和第二pmos finfet的饱和电流

(idsat)和漏电流(ioff)关联的考虑因素来选择的。例如,第一pmos finfet和第二pmos finfet可以是sram器件的头部单元中的pmos finfet(将在下面参考图7a描述其细节),因为头部单元中的该pmos finfet的漏电流对sram器件的总泄漏有显著贡献。应该注意,除了第一pmos finfet和第二pmos finfet之外,还可以选择电路中的除了第一pmos finfet和第二pmos finfet以外的pmos finfet。换句话说,在步骤508中,可以选择电路中的不止两个(例如,四个)pmos finfet。

47.然后,方法500进行至步骤510,在步骤510中,第一pmos finfet和第二pmos finfet被替换为第三pmos finfet。具体地,第一pmos finfet具有第一鳍数量,第二pmos finfet具有第二鳍数量并且第三pmos finfet具有第三鳍数量。鳍数量越大,整体鳍结构越宽。第三鳍数量等于第一鳍数量与第二鳍数量之和。如此,替换后整体鳍结构的宽度不变。然而,第三pmos finfet的漏电流小于第一pmos finfet和第二pmos finfet的总漏电流,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比。

48.图6是图示了按照一些实施例的使用图5的方法进行的nmos finfet和多个pmos finfet的替换的示意图。由于方法500可以被视为图1中示出的方法100与图3中示出的方法300的组合,因此图6可以被视为图2a和图4a的组合。具体地,电路690包括nmos finfet nm1以及两个pmos finfet pm1和pm2,还有其它。在步骤504中,选择nmos finfet nm1。nmos finfet nm1具有栅极g1、源极s1和漏极d1。具体地,nmos finfet nm1具有3个鳍(即,栅极结构在三个平行鳍结构的上方并控制这3个鳍结构)。在图5中示出的步骤506中,nmos finfet nm1被替换为nmos finfet nm2和nmos finfet nm3。具体地,nmos finfet nm2具有1个鳍,而nmos finfet nm3具有2个鳍。nmos finfet nm2具有栅极g1、源极s1和漏极d1;nmos finfet nm3也具有栅极g1、源极s1和漏极d1。换句话说,nmos finfet nm2和nm3的栅极、源极和漏极被分别连接。

49.另一方面,在图5中示出的步骤508中,选择pmos finfet pm1和pm2。具体地,pmos finfet pm1具有1个鳍(即,栅极结构在一个鳍结构的上方并控制该鳍结构),而pmos finfet pm2具有2个鳍(即,栅极结构在两个鳍结构的上方并控制这2个鳍结构)。pmos finfet pm1具有栅极g2、源极s2和漏极d2;pmos finfet pm2具有栅极g2、源极s2和漏极d2。换句话说,pmos finfet pm1和pm2的栅极、源极和漏极被分别连接。在图5中示出的步骤510中,pmos finfet pm1和pm2被pmos finfet pm3替换。具体地,pmos finfet pm3有3个鳍。pmos finfet pm3具有栅极g2、源极s2和漏极d2。

50.如此,对于nmos finfet,在图5中示出的步骤506中进行替换之后,总鳍数量是不变的(即,二者都是3个)。然而,nmos finfet nm2和nm3的总漏电流小于nmos finfet nm1的漏电流,因为具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。另一方面,对于pmos finfet,在图5中示出的步骤510中进行替换之后,总鳍数量是不变的(即,二者都是3个)。然而,pmos finfet pm3的漏电流小于pmos finfet pm1与pmos finfet pm2的总漏电流,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比。因此,在图5中示出的步骤506和步骤508中进行替换之后,电路690的总漏电流减小。

51.图7a是按照一些实施例的可以应用图5的方法500的sram器件的示意图。图7b是图示了按照一些实施例的图5的方法500的应用的示意图而图7c是图示了按照一些实施例的

与图7b对应的布局的示意图。图7d是图示了按照一些实施例的图5的方法500的应用的示意图而图7e是按照一些实施例的与图7d对应的布局的示意图。如图7a中所示,sram电路(也称为“sram器件”,其将被可互换使用)790包括存储器阵列710、字线(wl)、位线(bl和blb)、用于写操作的写驱动器720以及头部电路730a和730b(统称为730),还有其它。应该注意,sram电路790可以包括诸如未示出的存储器控制器、未示出的读驱动器、未示出的行解码器、未示出的列解码器和未示出的i/o电路之类的其它部件。

52.存储器阵列710包括按列行布置的多个存储器单元位(mcb)。对于每个存储器单元位(mcb),mcb可以通过互补位线bl和blb耦合,并且可以经由互补位线bl和blb与mcb进行数据的读取和写入。在图7a中示出的示例中,mcb包括但不限于六晶体管(6t)sram结构。在一些实施例中,可以使用多于或少于六个晶体管来实现mcb。例如,在一些实施例中,mcb可以使用4t、8t或10t sram结构。图7a中示出的mcb包括由nmos/pmos finfet对t1和t2形成的第一反相器、由nmos/pmos finfet对t3和t4形成的第二反相器以及存取finfet t5和t6。finfet t1、t3、t5和t6是nmos finfet,而finfet t2和t4是pmos finfet。

53.在图示示例中,mcb在第一功率域(即,vddm)中操作,因此通过头部电路730a连接到vddm电源轨。如图示示例中所示的头部电路730a包括并联连接的两个pmos finfet p5和p6。pmos finfet p5和p6的源极耦合到vddm电源轨,而pmos finfet p5和p6的漏极耦合到端子vddai,vddai又耦合到pmos finfet t2和t4的源极。pmos finfet p5和p6响应于关断(sd)信号而导通或截止,以在sram电路790的休眠模式期间节省功耗。

54.另一方面,在图7a中示出的示例中,写驱动器720包括四个pmos finfet p1、p2、p3、p4和两个nmos finfet,还有其它。pmos finfet p1和p2串联连接在端子vddhd_dr与nmos finfet n1之间,而pmos finfet p3和p4串联连接在端子vddhd_dr与nmos finfet n2之间。向端子vddhd_dr提供第二功率域(即,vdd)中的电压,该电压低于第一功率域(即,vddm)。pmos finfet p1和nmos finfet n1的栅极连接到第一写信号wc,而pmos finfet p3和nmos finfet n2的栅极连接到第二写信号wt。pmos finfet p2和p4的栅极连接到互补位线blb和bl。

55.在图示示例中,写驱动器720在第二功率域(即,vdd)中操作,因此通过头部电路730b连接到vdd电源轨。如在图示示例中示出的,头部电路730b包括并联连接的两个pmos finfet p7和p8。pmos finfet p7和p8的源极耦合到vdd电源轨,而pmos finfet p7和p8的漏极耦合到端子vddhd_dr,端子vddhd_dr又耦合到pmos finfet p1和p3的源极。pmos finfet p7和p8响应于关断(sd)信号而导通或截止,以在sram电路790的休眠模式期间节省功耗。

56.参考图7b和图7c,图5的方法500可以应用于nmos finfet n1。应该注意,图5的方法500也可以应用于nmos finfet n2,为了简明起见,不对此进行详细描述。如以上提到的,nmos finfet n1是sram电路790的写驱动器720中的nmos finfet,如果图5的方法500应用于nmos finfet n1,则漏电流可以减小。在图示示例中,nmos finfet n1具有5个鳍782和3个栅极指784,如图7c中所示。在应用图5的方法500之后,nmos finfet n1被替换为两个nmos finfet n1a和n1b。nmos finfet n1a具有2个鳍782和3个栅极指784,而nmos finfet n1b具有3个鳍782和3个栅极指784。因此,nmos finfet n1的鳍数量等于nmos finfet n1a和n1b的鳍数量之和。也就是说,总鳍数量不变。然而,nmos finfet n1a和n1b的总漏电流小

于nmos finfet n1的漏电流,因为具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。

57.参考图7d和图7e,图5的方法500可以应用于pmos finfet p5和p6。应该注意,图5的方法500也可以应用于pmos finfet p7和p8,为了简明起见,不对此进行详细描述。如以上提到的,pmos finfet p5和p6中的每个都是sram电路790的头部电路730中的pmos finfet,如果将图5的方法500应用于pmos finfet p5和p6,则漏电流可以减小。在图示示例中,pmos finfet p5和p6中的每个都具有3个鳍782和100个栅极指784,如图7e中所示。换句话说,pmos finfet p5和p6共同具有3个鳍782和200个栅极指784。在应用图5的方法500之后,pmos finfet p5和p6被替换为pmos finfet p9。pmos finfet p9具有6个鳍782和100个栅极指784。因此,pmos finfet p9的鳍数量等于pmos finfet p5和p6的鳍数量之和。也就是说,总鳍数量不变。然而,pmos finfet p9的漏电流小于pmos finfet p5和pmos finfet p6的总漏电流,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比。

58.因此,在图7b中示出的替换和图7d中示出的替换之后,sram电路790的总漏电流减小。基于模拟结果,通过应用图7b中示出的替换,对于标准电压(例如,200mv)漏电流可以减小3

‑

10%,而对于低电压(例如,150mv)漏电流可以减小5

‑

10%。另一方面,基于模拟结果,通过应用图7d中示出的替换,漏电流可以减小5

‑

10%。

59.此外,图5的方法500可以应用于各种电路。在一个非限制示例中,该方法可以应用于反相器,如下面图8中所示。在一个非限制示例中,该方法可以应用于存储器件的字线(wl)驱动器,如下面图9中所示。在一个非限制示例中,该方法可以应用于存储器件的行解码器(ydec)驱动器或列解码器(xdec)驱动器,如下面图10中所示。应该注意,上述的方法100、300和500的其它应用也在本发明的范围内。

60.图8是图示了按照一些实施例的应用图5的方法500的包括反相器的电路890的示意图。如图8中所示,电路890可以包括反相器891,还有其它。在图示示例中,反相器891包括并联耦合的两个pmos finfet pm81和pm82。并联的pmos finfet pm81和pm82与两个端子vdd和vss之间的nmos finfet nm81串联连接。pmos finfet pm81和nmos finfet nm81的栅极连接到输入端子。pmos finfet pm81和pm82中的每个都具有3个鳍,而nmos finfet nm81具有5个鳍。在应用图5的方法500之后,pmos finfet pm81和pm82被替换为pmos finfet pm83,而nmos finfet nm81被替换为两个nmos finfet nm82和nm83。pmos finfet pm83具有6个鳍,nmos finfet nm82具有2个鳍,而nmos finfet nm83具有3个鳍。换句话说,pmos finfet pm83的鳍数量等于pmos finfet pm81的鳍数量与pmos finfet pm82的鳍数量之和;nmos finfet nm81的鳍数量等于nmos finfet nm82的鳍数量和nmos finfet nm82的鳍数量与nmos finfet nm83的鳍数量之和。也就是说,总鳍数量不变。然而,过漏电流减小,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比,而具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。

61.图9是图示了按照一些实施例的应用图5的方法500的包括字线驱动器的存储器件电路990的示意图。如图9中所示,存储器件电路990可以包括字线驱动器991,还有其它。存储器电路990可以是sram器件,尽管其它类型的存储器件也在本发明的范围内。在图示示例中,字线驱动器991包括串联连接在时钟信号端子clk与字线信号端子wl之间的两个反相器

992和993。反相器993是最后一级,因此对漏电流的贡献相对大。反相器993包括例如其中每个都具有3个鳍的八个pmos finfet。在应用图5的方法500之后,八个pmos finfet被替换为其中每个都具有6个鳍的四个pmos finfet。换句话说,pmos finfet的总鳍数量不变。然而,过漏电流减小,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比。应该注意,只要总鳍数量不变,也可以采用其它替换布置(例如,各自具有8个鳍的三个pmos finfet)。还应该注意,反相器993中的nmos finfet也可以通过应用图5的方法500而被类似地替换。

62.图10是图示了按照一些实施例的应用图5的方法500的包括行解码器驱动器或列解码器驱动器的存储器件电路1090的示意图。如图10中所示,存储器件电路1090可以包括行解码器驱动器或列解码器驱动器1091,还有其它。存储器电路1090可以是sram器件,尽管其它类型的存储器件也在本发明的范围内。在图示示例中,行解码器驱动器或列解码器驱动器1091包括串联连接在两个输入信号端子a0、a1与输出端子dec之间的nand门1092和反相器1093。反相器1093是最后一级,因此对漏电流的贡献相对大。反相器1093包括例如其中每个都具有3个鳍的八个pmos finfet。反相器1093还包括例如其中每个都具有6个鳍的四个nmos finfet。在应用图5的方法500之后,八个pmos finfet被替换为其中每个都具有6个鳍的四个pmos finfet;四个nmos finfet被替换为其中每个都具有3个鳍的八个nmos finfet。换句话说,pmos finfet的总鳍数量不变;nmos finfet的总鳍数量不变。然而,过漏电流减小,因为具有较大鳍尺寸的pmos finfet由于较高的空穴迁移率而具有较高的饱和

‑

漏比,而具有较小鳍尺寸的nmos finfet由于较高的电子迁移率而具有较高的饱和

‑

漏比。同样,应该注意,只要总nmos/pmos鳍数量不变,也可以采用其它替换布置。

63.按照一些公开的实施例,提供了一种设计电路的方法。该方法包括:设置电路;选择该电路中的第一nmos鳍式场效应晶体管(finfet);以及将具有第一鳍数量的第一nmos finfet替换为具有第二鳍数量的第二nmos finfet和具有第三鳍数量的第三nmos finfet,其中,第二鳍数量与第三鳍数量之和等于第一鳍数量。

64.在上述方法中,电路是逻辑电路。

65.在上述方法中,电路是模拟电路。

66.在上述方法中,设置电路包括设置反相电路,反相电路具有与第一nmos finfet串联连接在第一电力端子和第二电力端子之间的第一pmos finfet。

67.在上述方法中,设置电路包括设置存储器件的字线驱动器,并且字线驱动器包括串联连接在时钟信号端子和字线信号端子之间的第一反相器和第二反相器。

68.在上述方法中,第二反相器包括第一nmos finfet。

69.在上述方法中,设置电路包括设置存储器件的解码器驱动器,并且解码器驱动器包括串联连接在两个输入信号端子和一个输出端子之间的nand门和反相器。

70.在上述方法中,反相器包括第一nmos finfet。

71.在上述方法中,设置电路包括设置静态随机存取存储器(sram)电路,并且sram电路包括存储器单元和写驱动器,存储器单元和写驱动器二者耦合在第一位线和第二位线之间。

72.在上述方法中,写驱动器包括第一nmos finfet。

73.在上述方法中,写驱动器包括:第一pmos finfet,具有与第一电力端子耦合的第

一源极/漏极端子;第二pmos finfet,具有与第一pmos finfet的第二源极/漏极端子耦合的第一源极/漏极端子以及与第一位线耦合的栅极端子;第三pmos finfet,具有与第一电力端子耦合的第一源极/漏极端子;第四pmos finfet,具有与第三pmos finfet的第二源极/漏极端子耦合的第一源极/漏极端子以及与第二位线耦合的栅极端子;第一nmos finfet,连接在第二pmos finfet的第二源极/漏极端子和第二电力端子之间,其中,第一nmos finfet的栅极端子连接到第一写输入端子;以及第四nmos finfet,连接在第四pmos finfet的第二源极/漏极端子和第二电力端子之间,其中,第四nmos finfet的栅极端子连接到第二写输入端子。

74.在上述方法中,还包括:选择电路中的第一pmos finfet和第二pmos finfet;以及将具有第四鳍数量的第一pmos finfet和具有第五鳍数量的第二pmos finfet替换为具有第六鳍数量的第三pmos finfet,其中,第四鳍数量与第五鳍数量之和等于第六鳍数量。

75.按照一些公开的实施例,提供了另一种设计电路的方法。该方法包括:设置电路;选择该电路中的第一pmos finfet;以及将具有第一鳍数量的第一pmos finfet和具有第二鳍数量的第二pmos finfet替换为具有第三鳍数量的第三pmos finfet,其中,第一鳍数量与第二鳍数量之和等于第三鳍数量。

76.在上述方法中,第一pmos finfet与第二pmos finfet并联连接。

77.在上述方法中,设置电路包括设置sram电路,并且sram电路包括存储器单元和连接在存储器单元和第一电压端子之间的第一头部电路,其中,第一头部电路包括并联连接的第一pmos finfet和第二pmos finfet,并且第一pmos finfet和第二pmos finfet响应于关断信号而导通或截止。

78.在上述方法中,sram电路还包括写驱动器和连接在写驱动器和第二电压端子之间的第二头部电路,其中,第二头部电路包括并联连接的具有第四鳍数量的第四pmos finfet和具有第五鳍数量的第五pmos finfet,并且方法还包括:将第四pmos finfet和第五pmos finfet替换为具有第六鳍数量的第六pmos finfet,其中,第四鳍数量与第五鳍数量之和等于第六鳍数量。

79.在上述方法中,第一电压端子被提供在第一电压域中的第一电压,第二电压端子被提供在第二电压域中的第二电压,并且第一电压域高于第二电压域。

80.在上述方法中,设置电路包括设置反相电路,反相电路具有并联连接的第一pmos finfet和第二pmos finfet以及第一nmos finfet。

81.按照其它公开的实施例,提供一种sram器件。该sram器件包括:存储器单元和写驱动器。存储器单元包括:第一反相器;第二反相器,其与第一反相器交叉耦合;第一存取晶体管,其连接在第一反相器的第一数据节点与第一位线之间;第二存取晶体管,其连接在第二反相器的第二数据节点与第二位线之间。写入驱动器包括:第一pmos finfet,其具有与第一电力端子耦合的第一源极/漏极端子;第二pmos finfet,其具有与第一pmos finfet的第二源极/漏极端子耦合的第一源极/漏极端子以及与第一位线耦合的栅极端子;第三pmos finfet,其具有与第一电力端子耦合的第一源极/漏极端子;第四pmos finfet,其具有与第三pmos finfet的第二源极/漏极端子耦合的第一源极/漏极端子以及与第二位线耦合的栅极端子;第一和第二nmos finfet,其并联连接在第二pmos finfet的第二源极/漏极端子与第二电力端子之间,其中,第一pmos finfet的栅极端子以及第一和第二nmos finfet的栅

极端子被连接,以接收第一写信号;第三和第四nmos finfet,其并联连接在第四pmos finfet的第二源极/漏极端子与第二电力端子之间,其中,第三pmos finfet的栅极端子以及第三和第四nmos finfet的栅极端子被连接,以接收第二写信号。

82.在上述sram器件中,第一和第二nmos finfet总共具有第一数量的鳍,第一和第二nmos晶体管替换具有第一数量的鳍的第一单个nmos finfet,并且其中,第三和第四nmos finfet总共具有第一数量的鳍,第三和第四nmos晶体管替换具有第一数量的鳍的第二单个nmos finfet。

83.上面概述了若干实施例的特征,使得本领域技术人员可以更好地理解本发明的方面。本领域技术人员应该理解,它们可以容易地使用本发明作为基础来设计或修改用于实施与本文所介绍实施例相同的目的和/或实现相同优势的其它工艺和结构。本领域技术人员也应该意识到,这种等同构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,本文中它们可以做出多种变化、替换以及改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1