用于擦除非易失性存储器装置中的数据的设备和方法与流程

1.本文中所描述的一个或更多个实施方式涉及一种存储器装置,并且更具体地,涉及一种用于擦除存储于非易失性存储器装置中的数据的设备和方法。

背景技术:

2.最近,计算环境的范式已经转变为无处不在的计算,这使得能够几乎随时随地地接入计算机系统。因此,便携式电子装置(例如,移动电话、数码相机、笔记本计算机等)的使用快速增加。这些装置中的每一者可以使用或包括具有至少一个存储器装置的存储器系统。存储器系统可以是例如可以用作主存储装置或辅存储装置的数据存储装置。

3.这样的数据存储装置可以包括展现出提高的稳定性和耐久性、不具有机械驱动部件(例如,机械臂)并且因此提供高数据接入速度和相对低的功耗的一个或更多个非易失性半导体存储器。这些类型的数据存储装置的示例包括但不限于通用串行总线(usb)存储器装置、具有各种接口的存储卡以及固态驱动器(ssd)。

技术实现要素:

4.本公开的实施方式可以提供一种用于擦除存储在非易失性存储器装置中的数据的设备和方法。

5.根据本公开的实施方式,当在用于擦除存储在非易失性存储器装置中的存储块中的数据的擦除操作期间将高电平电压施加到多个非易失性存储器单元所在的块体时,施加到块体的高电平电压引起串中的沟道处的电荷积累。因为累积电荷可能引起不利影响,所以实施方式可以提供能够使通过位线和公共源极线进行的沟道中的电荷放电同步的设备和方法。

6.此外,根据本公开的实施方式,当非易失性存储器装置执行擦除操作时,电荷可以以相同的速度或在预设的时间差内通过位线和公共源极线从串的沟道被放电。当在一侧的放电速度比在另一侧的放电速度更快时,可能出现其中字线被向下耦合到负电压的负升压或欠耦合。另外,当一侧的放电速度比另一侧更慢时,可能出现在非易失性存储器单元中存储的数据未被正常擦除的现象。

7.此外,根据本公开的实施方式,当在非易失性存储器装置中执行的擦除操作期间通过位线和公共源极线以相同速度或在预设时间差内对串的沟道中的电荷进行放电时,存储器装置可以均匀地控制非易失性存储器单元的特性(其可能根据非易失性存储器单元的位置而变化(例如,更接近位线或更接近公共源极线)),使得可以提高非易失性存储器单元的操作可靠性。

8.在实施方式中,存储器装置可以包括:多个非易失性存储器单元,多个非易失性存储器单元能够存储数据并且被串联布置在位线和源极线之间;以及控制电路,控制电路被配置为在用于擦除存储在多个非易失性存储器单元中的数据的擦除操作期间使通过位线和源极线进行的对在由多个非易失性存储器单元形成的沟道中累积的电荷的放电同步。

9.控制电路可以被配置为控制施加到包括在沟道中的晶体管的电压电平或流经沟道的电流量以使通过位线和公共源极线进行的对沟道中的电荷的放电以相同速度或在预设时间差内同步。

10.控制电路可以被配置为响应于通过源极线对电荷进行放电的第一速度而调整通过位线对电荷进行放电的第二速度以使通过位线和源极线进行的对沟道中的电荷的放电同步。

11.控制电路可以被配置为改变施加到第二放电晶体管的栅极的电压电平以调整第二速度,第二放电晶体管被配置为将接地电压施加到位线。

12.控制电路可以被配置为改变施加到第二放电晶体管的栅极的电压电平以改变第二放电晶体管的电阻。

13.存储器装置还可以包括:多个第一放电晶体管,多个第一放电晶体管独立地被配置为向源极线施加接地电压。控制电路可以被配置为选择性地导通多个第一放电晶体管以控制通过源极线的对电荷进行的放电的第一速度,以使通过位线和源极线进行的对沟道中的电荷的放电同步。

14.存储器装置还可以包括:被配置为向位线施加接地电压的至少一个第二放电晶体管。控制电路可以被配置为响应于多个第一放电晶体管的导通而改变施加到第二放电晶体管的栅极的电压电平以使通过位线和源极线进行的对沟道中的电荷的放电同步。

15.存储器装置还可以包括:多个第一放电晶体管,多个第一放电晶体管独立地被配置为向源极线施加接地电压;以及多个第二放电晶体管,多个第二放电晶体管独立地被配置为向位线施加接地电压。控制电路可以被配置为选择性地导通多个第一放电晶体管和多个第二放电晶体管以使通过位线和源极线进行的对沟道中的电荷的放电同步。

16.控制电路可以被配置为在多个第一放电晶体管当中导通比多个第二放电晶体管当中的导通的第二放电晶体管的数量更大数量的第一放电晶体管。

17.存储器装置还可以包括:第一放电晶体管,第一放电晶体管被配置为向源极线施加接地电压;以及第二放电晶体管,第二放电晶体管被配置为向位线施加接地电压。控制电路可以被配置为调整施加到第一放电晶体管和第二放电晶体管的栅极的第一电压和第二电压的电平以控制通过源极线对电荷进行的放电的第一速度和通过位线对电荷进行的放电的第二速度,以使通过位线和源极线进行的对沟道中的电荷的放电同步。

18.可以同时施加第一电压和第二电压。第一电压可以具有比第二电压更高的电平。

19.在另一实施方式中,存储器系统可以包括:存储器装置,存储器装置被配置为存储数据;以及控制器,控制器联接到存储器装置并且被配置为发送关于数据的读取命令、写入命令或擦除命令。存储器装置可以包括:多个非易失性存储器单元,多个非易失性存储器单元被串联布置在位线和源极线之间;以及控制电路,控制电路被配置为响应于擦除命令使通过位线和源极线进行的对在由多个非易失性存储器单元形成的沟道中累积的电荷的放电同步。

20.控制电路可以被配置为控制施加到包括在沟道中的晶体管的电压电平或流经沟道的电流量以使通过位线和源极线进行的对沟道中的电荷的放电以相同速度或在预设时间差内同步。

21.控制电路可以被配置为响应于通过源极线对电荷进行放电的第一速度而调整通

过位线对电荷进行放电的第二速度以使通过位线和源极线进行的对沟道中的电荷的放电同步。

22.控制电路可以被配置为改变施加到第二放电晶体管的栅极的电压电平以调整第二速度,第二放电晶体管被配置为将接地电压施加到位线。

23.存储器装置还可以包括多个第一放电晶体管,多个第一放电晶体管独立地被配置为向源极线施加接地电压。控制电路可以被配置为选择性地导通多个第一放电晶体管以控制通过源极线对电荷进行放电的第一速度,以使通过位线和源极线进行的对沟道中的电荷的放电同步。

24.存储器装置还可以包括:被配置为向位线施加接地电压的至少一个第二放电晶体管。控制电路可以被配置为响应于多个第一放电晶体管的导通而改变施加到第二放电晶体管的栅极的电压电平以使通过位线和源极线进行的对沟道中的电荷的放电同步。

25.存储器装置还可以包括:多个第一放电晶体管,多个第一放电晶体管独立地被配置为向源极线施加接地电压;以及多个第二放电晶体管,多个第二放电晶体管独立地被配置为向位线施加接地电压。控制电路可以被配置为选择性地导通多个第一放电晶体管和多个第二放电晶体管以使通过位线和源极线进行的对沟道中的电荷的放电同步。控制电路被配置为在多个第一放电晶体管当中导通比多个第二放电晶体管当中的导通的第二放电晶体管的数量更大数量的第一放电晶体管。

26.存储器装置还可以包括:第一放电晶体管,第一放电晶体管被配置为向源极线施加接地电压;以及第二放电晶体管,第二放电晶体管被配置为向位线施加接地电压。控制电路可以被配置为调整施加到第一放电晶体管和第二放电晶体管的栅极的第一电压和第二电压的电平以控制通过源极线对电荷进行的放电的第一速度和通过位线对电荷进行的放电的第二速度,以使通过位线和源极线进行的对沟道中的电荷的放电同步。可以同时施加第一电压和第二电压。第一电压可以具有比第二电压更高的电平。

27.在实施方式中,一种用于操作存储器系统的方法可以包括以下步骤:响应于擦除命令,确定用于擦除存储在多个非易失性存储器单元中的数据的擦除电压和栅极电压的电平;向多个非易失性存储器单元所在的块体施加擦除电压并且向联接到多个非易失性存储器单元的字线施加负电压或0v的接地电压;控制通过位线和源极线对在由多个非易失性存储器单元形成的沟道中累积的电荷进行放电的路径,以使通过位线和源极线的放电速率或时间同步;以及验证数据是否被擦除。

28.在另一实施方式中,一种存储器装置可以包括:非易失性存储器单元的串,非易失性存储器单元串联布置在位线与源极线之间;第一放电电路,第一放电电路被配置为通过参考被配置为在其中存储关于第一时间点、第一放电量和第一放电时间长度的信息的寄存器在第一时间点将源极线以第一放电量放电达第一放电时间长度;第二放电电路,第二放电电路被配置为在第二时间点将位线以第二放电量放电达第二放电时间长度;以及控制电路,控制电路被配置为通过基于所述信息来确定第二时间点、第二放电量和第二放电时间长度从而控制第一放电电路和第二放电电路在对串的擦除操作期间进行操作。

附图说明

29.本文的描述参照附图,其中在所有附图中,相同的附图标记指代相同的部件。

30.图1例示根据本公开的实施方式的存储器装置。

31.图2例示根据本公开的实施方式的数据处理系统。

32.图3例示根据本公开的实施方式的在存储器装置中执行的擦除操作期间在沟道中生成电荷的现象。

33.图4例示根据本公开的实施方式的用于擦除存储在非易失性存储器单元中的数据的方法。

34.图5例示根据本公开的实施方式的用于控制存储器装置的位线的电路。

35.图6例示根据本公开的实施方式的用于控制存储器装置的公共源极线的电路。

36.图7例示根据本公开的实施方式的在存储器装置中执行的擦除操作期间的沟道放电。

37.图8例示根据本公开的实施方式的在存储器装置中执行的擦除操作期间通过位线和公共源极线对串的沟道中的电荷进行放电的操作。

38.图9例示根据本公开的实施方式的用于在存储器装置中使通过位线和公共源极线进行的放电同步的方法。

39.图10例示根据本公开的实施方式的用于使放电同步的第一示例。

40.图11例示根据本公开的实施方式的用于使放电同步的第二示例。

41.图12例示根据本公开的实施方式的用于使放电同步的第三示例。

具体实施方式

42.下面参照附图描述本公开的各个实施方式。然而,本公开的元件和特征可以被不同地配置或布置以形成其它实施方式,其可以是所公开的实施方式中的任何实施方式的变型。

43.在本公开中,对包括在“一个实施方式中”、“示例实施方式”、“实施方式”、“另一实施方式”、“一些实施方式”、“各个实施方式”、“其它实施方式”、“替代实施方式”等中的各个特征(例如,元件、结构、模块、组件、步骤、操作、特性等)的引用旨在表示任何这样的特征被包括在本公开的一个或更多个实施方式中,但是可以或可以不必在相同的实施方式中被组合。

44.在本公开中,术语“包括”、“包含”、“具有”和“含有”是开放式的。如在所附权利要求中所使用的,这些术语指定所陈述的元件的存在,并且不排除一个或更多个其它元件的存在或添加。权利要求中的这些术语不排除装置包括附加组件(例如,接口单元、电路等)。

45.在本公开中,各种单元、电路或其它组件可以被描述或要求保护为“被配置为”执行一个或多个任务。在这样的上下文中,“被配置为”用于通过指示块/单元/电路/组件包括在操作期间执行一个或更多个任务的结构(例如,电路)来隐含结构。这样,即使在所指定的块/单元/电路/组件当前未操作(例如,未被开启或被激活)时,块/单元/电路/组件也可以被称为被配置为执行任务。与“被配置为”语言一起使用的块/单元/电路/组件包括硬件(例如,电路、存储可执行以实现操作的程序指令的存储器等)。另外,“被配置为”可以包括由软件和/或固件(例如,执行软件的通用处理器或fpga)操纵从而以能够执行所讨论的任务的方式操作的通用结构(例如,通用电路)。“被配置为”还可以包括使制造工艺(例如,半导体制造设施)适用于制造适用于实现或执行一个或更多个任务的装置(例如,集成电路)。

46.如在本公开中所使用的,术语“电路”或“逻辑”是指以下全部:(a)仅硬件电路实现(诸如仅在模拟电路和/或数字电路中的实现)和(b)电路和软件(和/或固件)的组合,例如(如适用):(i)处理器的组合,或(ii)一起工作以使设备(例如,移动电话或服务器)执行各种功能的处理器/软件(包括数字信号处理器)、软件和存储器的部分,以及(c)需要软件或固件以进行操作的电路(例如,微处理器或微处理器的一部分),即使软件或固件在物理上不存在。“电路”或“逻辑”的该定义适用于本技术中的包括在任意权利要求中的该术语的所有用例。作为又一示例,如在本技术中使用的,术语“电路”或“逻辑”也涵盖仅处理器(或多个处理器)或处理器的部分及其随附软件和/或固件的实现。术语“电路”或“逻辑”还涵盖(例如,并且如果适用于特定权利要求要素)用于存储装置的集成电路。

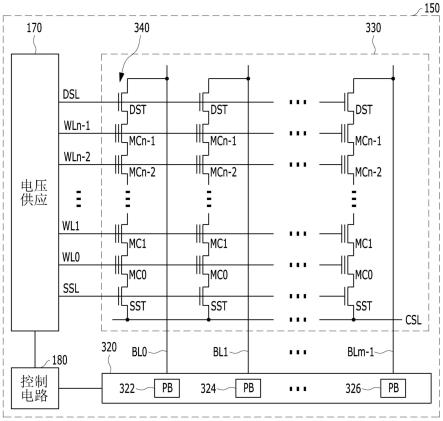

47.如本文所使用的,术语“第一”、“第二”、“第三”等被用作它们后面的名词的标签,并且不隐含任何类型的排序(例如,空间、时间、逻辑等)。术语“第一”和“第二”并不一定隐含第一值一定在第二值之前被写入。此外,尽管本文可能使用这些术语来标识各种元件,但这些元件不受这些术语的限制。这些术语用于将一个元件与否则将具有相同或相似名称的另一元件区分开来。例如,第一电路可以与第二电路区分开来。

48.此外,术语“基于”用于描述影响确定的一个或多更个因素。该术语不排除影响确定的附加因素。也就是说,确定可仅仅基于这些因素或至少部分地基于这些因素。考虑短语“基于b来确定a”。虽然在这种情况下,b是影响a的确定的因素,但是短语并不排除还基于c来确定a。在其它情况下,a可以仅基于b来确定。

49.在本文中,数据的项、数据项、数据条目或数据的条目可以是比特序列。例如,数据项可以包括文件的内容、文件的一部分、存储器中的页、面向对象的程序中的对象、数字消息、数字扫描的图像、视频或音频信号的一部分、元数据或可以由比特序列表示的任何其它实体。根据实施方式,数据项可以包括离散对象。根据另一实施方式,数据项可以包括在两个不同组件之间的传输分组内的信息单元。

50.本文描述的实施方式提供了数据处理系统和用于操作数据处理系统的方法。数据处理系统包括诸如存储器系统和主机的组件和资源,并且能够基于组件和资源的使用来动态地分配用于组件之间的数据通信的多个数据路径。

51.现在将参照附图描述实施方式,其中相似的附图标记表示相似的元件。

52.图1例示根据本公开的实施方式的包括形成在存储器管芯中的存储器单元阵列电路的存储器装置150。

53.参照图1,存储器装置150可以包括具有多个单元串340的至少一个存储器组330。每个单元串340可以包括连接到多条位线bl0至blm-1中的相应一者的多个非易失性存储器单元mc0至mcn-1。单元串340被设置在存储器组330的相应列中,并且每个单元串340可以包括至少一个漏极选择晶体管dst和至少一个源极选择晶体管sst。每个单元串340的非易失性存储器单元mc0至mcn-1可以串联连接在漏极选择晶体管dst和源极选择晶体管sst之间。非易失性存储器单元mc0至mcn-1中的每一个可以被配置为多级单元(mlc),其每单元存储具有多个比特的数据项。单元串340可以电连接到位线bl0至blm-1的对应位线。

54.在一个实施方式中,存储器组330可以包括nand型闪存存储器单元mc0至mcn-1。在另一实施方式中,存储器组330可以被实现为nor型闪存存储器、其中混合或组合至少两种不同类型的存储器单元的混合闪存存储器、或其中控制器被嵌入在单个存储器芯片中的单

芯片nand闪存存储器。在实施方式中,存储器组330可以包括闪存存储器单元,该闪存存储器单元包括具有导电浮置栅极或绝缘层的电荷捕获闪存(ctf)层。

55.图2例示根据本公开的实施方式的可以包括存储器装置150的存储器系统110。在该实施方式中,存储器装置150中的存储器组330可以包括一个或更多个存储块152、154、156。根据实施方式,存储器装置150可以具有二维(2d)结构或三维(3d)结构。例如,存储器装置150中的存储块152、154、156中的每一个可以被实现为3d结构(即,垂直结构)。存储块152、154、156中的每一个可以具有沿着第一方向至第三方向(例如,x轴方向、y轴方向和z轴方向)延伸的三维结构。

56.包括多个存储块152、154、156的存储器组330可以联接到多条位线bl、多条源极选择线或串选择线ssl和多条漏极选择线dsl、多条字线wl、多条虚设字线dwl和多条公共源极线csl。在实施方式中,存储器组330可以包括例如可以分别与单元串340相对应的多个nand串ns。每个nand串ns可以包括多个存储器单元mc并且可以连接到位线bl中的相应位线。另外,每个nand串ns的串选择晶体管sst可以连接到公共源极线csl,并且每个nand串ns的漏极选择晶体管dst可以连接到对应位线bl。在每个nand串ns中,存储器单元mc可以布置在串选择晶体管sst和漏极选择晶体管dst之间。

57.参照图1和图2,存储器装置150可以包括电压供应电路170,其可以根据操作模式供应针对相应字线的字线电压(例如,诸如编程电压、读取电压和通过电压的一个或更多个预定电压),或可以将电压提供给其中形成包括存储器单元mc的每个存储块的块体(bulk)(例如,阱区域)。在这种情况下,可以在控制电路180的控制下执行电压供应电路170的电压生成操作。此外,电压供应电路170可以生成多个可变读取电压以将多个数据项彼此区分开。

58.响应于控制电路的控制,可以选择存储器单元阵列的存储块中的一个或扇区中的一个,并且可以选择所选存储块的字线中的一条。可以独立地将字线电压供应给所选字线和未选字线。电压供应电路170可以包括用于生成具有各种电平的目标电压的电压发生电路(例如,参照图4至图8)。

59.在实施方式中,电压供应电路170可以联接到接收从外部(例如,外部装置)施加的第一电源电压vcc的第一引脚或焊盘,以及接收从外部装置施加的第二电源电压vpp的第二引脚或焊盘。第二电源电压vpp可以具有比第一电源电压vcc的电压电平更高(例如,是第一电源电压vcc的电压电平的两倍或更高)的电压电平。例如,第一电源电压vcc可以具有2.0v至5.5v的电压电平,而第二电源电压可以具有9v至13v的电压电平。

60.根据实施方式,电压供应电路170可以包括用于更快速地生成存储器组330中使用的各种电平的目标电压的电压发生电路。电压发生电路可以使用第二电源电压vpp来生成目标电压,该目标电压可以具有比第二电源电压vpp更高的电压电平。

61.存储器装置150还可以包括由控制电路180控制的读取/写入电路320。读取/写入电路320可以根据操作模式用作感测放大器或写入驱动器。例如,在验证操作和读取操作中,读取/写入电路320可以用作用于从存储器单元阵列读取数据项的感测放大器。在编程操作中,读取/写入电路320可以用作根据待存储于存储器单元阵列中的数据项来控制位线的电位的写入驱动器。读取/写入电路320可以在编程操作期间从页缓冲器接收待编程到单元阵列的数据项。读/写电路320可以基于输入数据项来驱动位线。为此,读取/写入电路320

可以包括多个页缓冲器(pb)322、324、326,其中每个页缓冲器与每一列或每一位线相对应,或与每一列对(column pair)或每一位线对相对应。根据实施方式,多个锁存器可以被包括在页缓冲器322、324、326中的每一个中。

62.页缓冲器322、324、326可以通过多条总线bus联接到数据输入/输出装置(例如,串行化电路(serialization circuit)或串行器)。当页缓冲器322、324、326中的每一个通过不同总线联接到数据输入/输出装置时,可以减少在来自页缓冲器322、324、326的数据传输中可能出现的延迟。例如,每个页面缓冲器322、324、326可以执行数据传输而没有等待时间。

63.根据实施方式,存储器装置150可以接收写入命令、写入数据以及关于写入数据将存储到的位置的信息(例如,物理地址)。控制电路180使电压供应电路170生成用于响应于写入命令而执行的编程操作的编程脉冲、通过电压等,并且生成用于在编程操作之后执行的验证操作的一个或更多个电压。

64.当多比特数据项被编程在包括在存储器组330中的非易失性存储器单元中时,错误率可能高于当单比特数据项被存储在非易失性存储器单元中时的错误率。例如,可能由于单元到单元干扰(cci)而诱发非易失性存储器单元中的错误。为了减少非易失性存储器单元中的错误,应当减小非易失性存储器单元之间的阈值电压分布(与所存储的数据项相对应)的宽度(偏差)。

65.为此,存储器装置150可以执行增量步进脉冲编程(ispp)操作以有效地获得非易失性存储器单元的窄阈值电压分布。在实施方式中,存储器装置150可以使用ispp操作以进行多步骤编程操作。例如,存储器装置150可以在非易失性存储器单元或页之间根据预定顺序将编程操作划分为最低有效位(lsb)编程操作和最高有效位(msb)操作。

66.根据实施方式,可以提供一种能够在通过向存储器装置中的存储器单元施加多个编程脉冲而实现的数据编程操作期间减少在编程脉冲施加之间用于对位线或沟道进行放电的时间的设备和方法。当放电时间可以减少时,可以增大存储器装置的编程操作的速度。例如,为了对存储器装置中的位线或沟道进行放电,存储器装置可以控制或调整位线选择线或漏极选择线(dsl)的电压电平,以便于在通过位线选择线或漏极选择线(dsl)控制时避免晶体管处于浮置状态。这是因为当晶体管处于浮置状态时,可能不能适当地对位线或沟道进行放电。

67.在实施方式中,存储器装置可以在将编程脉冲施加到存储器装置中的非易失性存储器单元的单位编程操作(unit program operation)期间调整和改变用于在施加编程脉冲之后调整位线的电位的设定时间。因此,可以提供能够增大编程操作的速度和/或提高编程操作效率的设备和方法。

68.例如,在将多个编程脉冲施加到存储器装置中的非易失性存储器单元以便于利用多比特数据来编程非易失性存储器单元的操作期间,存储器装置可以以各种模式中的一者执行其中在已施加第一编程脉冲之后施加第二编程脉冲的单位编程操作。

69.单位编程操作的模式可以包括第一编程模式、第二编程模式和第三编程模式。在第一编程模式下,响应于第二编程脉冲对数据进行编程的程度(例如,当施加了第二编程脉冲时在非易失性存储器单元中的阈值电压的改变或转变)可以类似于或大于响应于第一编程脉冲对数据进行编程的程度。在第二编程模式下,响应于第二编程脉冲对数据进行编程

的程度小于响应于第一编程脉冲对数据进行编程的程度。在第三编程模式下,响应于第二编程脉冲对数据进行编程的程度是不存在的(例如,即使在施加第二编程脉冲时在非易失性存储器单元中也不存在阈值电压的改变或转变)。模式可以基于在施加编程脉冲时联接到目标存储器单元的位线的电位来实现。如果放电时间可以减少,则存储器装置可以通过调整和改变用于对位线电位进行改变或放电的设定时间来提高数据编程操作的效率或速度。

70.根据实施方式,存储器装置可以响应于编程操作环境(例如,温度)和关于在数据编程操作期间施加到非易失性存储器单元的编程脉冲的电平(或大小)或施加数量而改变或调整通过位线选择线或漏极选择线(dsl)施加的控制电压。因此,存储器装置可以通过将多个编程脉冲施加到非易失性存储器单元而在数据编程操作期间减小与每个编程脉冲相对应的操作裕度。这可以减少执行数据编程操作所花费的时间。

71.再次参照图2,存储器装置150被示为包括在数据处理系统100中。根据实施方式,数据处理系统100可以包括与存储器系统(例如,存储器系统110)接合或联接的主机102。例如,主机102和存储器系统110可以经由数据总线、主机线缆等彼此联接以执行数据通信。

72.存储器系统110可以包括存储器装置150和控制器130。存储器系统110中的存储器装置150和控制器130可以被认为是彼此物理分离的组件或元件。存储器装置150和控制器130可经由至少一个数据路径连接。例如,数据路径可以包括信道(channel)和/或通路(way)。

73.根据实施方式,存储器装置150和控制器130可以是在功能上划分的组件或元件。此外,根据实施方式,存储器装置150和控制器130可以在单个芯片中或多个芯片中实现。控制器130可以响应于从外部装置输入的请求来执行数据输入/输出操作。例如,当控制器130响应于从外部装置输入的读取请求输入而执行读取操作时,存储在包括在存储器装置150中的多个非易失性存储器单元中的数据被传送到控制器130。

74.在图2中,存储器装置150可以包括一个或更多个存储块152、154、156。存储块152、154、156中的每一个可以被理解为通过单个擦除操作将数据一起去除的一组非易失性存储器单元。存储块152、154、156可以包括至少一个页(例如,在单个编程操作期间一起存储数据和/或在单个读取操作期间一起输出数据的一组非易失性存储器单元)。例如,一个存储块可以包括多个页。

75.在实施方式中,存储器装置150可以包括多个存储器平面或者一个或更多个存储器管芯。根据实施方式,存储器平面可以被认为是逻辑分区或物理分区,其包括至少一个存储块、能够控制多个非易失性存储器单元的阵列的驱动电路以及可以临时存储输入到非易失性存储器单元或从非易失性存储器单元输出的数据的缓冲器。

76.根据实施方式,每个存储器管芯可以包括至少一个存储器平面,并且可以被理解为在物理上可区分的基板上实现的组件的集合。每个存储器管芯可以通过数据路径连接到控制器130,并且可以包括用于与控制器130交换数据项和信号的接口。

77.根据实施方式,存储器装置150可以包括至少一个存储块152、154、156,至少一个存储器平面或至少一个存储器管芯。存储器装置150的内部配置(例如,图1所示)可以根据存储器系统110的性能而不同。本公开的实施方式不限于图2中所示的内部配置。

78.在图2中,存储器装置150包括能够将一个或更多个电压提供给存储块152、154、

156的电压供应电路170。电压供应电路170可以包括用于生成针对存储块152、154、156的目标电压(例如,如参照图4至图8所描述的)的电压发生电路。

79.在实施方式中,电压供应电路170可以将读取电压vrd、编程电压vprog、通过电压vpass或擦除电压vers提供给包括在存储块中的非易失性存储器单元。例如,在用于读取存储在存储块152、154、156中的非易失性存储器单元中的数据的读取操作期间,电压供应电路170可以将读取电压vrd提供给所选非易失性存储器单元。在用于将数据存储在存储块152、154、156中的非易失性存储器单元中的编程操作期间,电压供应电路170可以将编程电压vprog提供给所选非易失性存储器单元中。在对所选非易失性存储器单元执行的读取操作或编程操作期间,电压供应电路170可以将通过电压vpass提供给未选非易失性存储器单元。在用于擦除存储在存储块152、154、156中的非易失性存储器单元中的数据的擦除操作期间,电压供应电路170可以将擦除电压vers提供给存储块。

80.存储器装置150可以基于执行哪一操作而存储关于提供给存储块152、154、156的各种电压的信息。例如,当存储块152、154、156中的非易失性存储器单元可以存储多比特数据时,可以使用用于识别或读取多比特数据项的读取电压vrd的多个电平。存储器装置150可以包括具有指示与多比特数据项相对应的读取电压vrd的多个电平的信息的表。例如,该表可以包括存储在寄存器中的偏置值,其中每个偏置值与读取电压vrd的特定电平相对应。用于读取操作的读取电压vrd的偏置值的数量可以被限定于预设范围。此外,在一个实施方式中,偏置值可以被量化。

81.主机102可以包括便携式电子装置(例如,移动电话、mp3播放器、膝上型计算机等)或非便携式电子装置(例如,台式计算机、游戏机、电视机、投影仪等)。根据实施方式,主机102可以包括被包括在便携式电子装置和非便携式电子装置中的中央处理单元(cpu)。

82.主机102可以包括可以控制在主机102中执行的功能和操作的至少一个操作系统(os)。os可以提供在操作上与存储器系统110接合的主机102和打算将数据存储在存储器系统110中的用户之间的互操作性。os可以支持与用户请求相对应的功能和操作。作为示例而非限制,os可以根据主机102的移动性被分类为通用操作系统和移动操作系统中。可以根据系统要求或用户环境将通用操作系统划分为个人操作系统和企业操作系统。与个人操作系统相比,企业操作系统可以专门用于确保和支持高性能计算。

83.移动操作系统可以支持用于移动性的服务或功能(例如,省电功能)。主机102可以包括多个操作系统。主机102可以执行与用户请求相对应的与存储器系统110互锁的多个操作系统。主机102可以将与用户请求相对应的多个命令发送到存储器系统110,从而在存储器系统110内执行多个命令相对应的操作。

84.控制器130可以响应于来自主机102的请求或命令而控制存储器装置150。例如,控制器130可以执行读取操作以将从存储器装置150读取的数据提供到主机102并且可以执行写入操作(或编程操作)以将从主机102输入的数据存储在存储器装置150中。为了执行数据输入/输出(i/o)操作,控制器130可以控制和管理读取数据、编程数据、擦除数据等的内部操作。

85.根据实施方式,控制器130可以包括主机接口(i/f)132、处理器134、纠错电路(ecc)138、电源管理单元(pmu)140、存储器接口(i/f)142和存储器144。如图2所示的控制器130中的组件可以根据关于存储器系统110的结构、功能、操作性能等而变化。

86.例如,存储器系统110可以利用根据主机接口的协议与主机102电联接的各种类型的存储装置中的任意一种来实现。合适的存储装置的非限制性示例包括固态驱动器(ssd)、多媒体卡(mmc)、嵌入式mmc(emmc)、尺寸减小mmc(rs-mmc)、微型mmc、安全数字(sd)卡、迷你sd、微型sd、通用串行总线(usb)存储装置、通用闪存(ufs)装置、紧凑型闪存(cf)卡、智能媒体(sm)卡、记忆棒等。可以根据存储器系统110的实现方式将组件添加到控制器130或从控制器130省略。

87.主机102和存储器系统110中的每一个可以包括用于根据一个或更多个预定协议发送和接收信号、数据等的控制器或接口。例如,存储器系统110中的主机接口132可以包括能够向主机102发送信号、数据等或者从主机102接收信号、数据等的设备。

88.主机接口132可以接收从主机102输入的信号、命令(或请求)和/或数据。例如,主机102和存储器系统110可以使用预定协议在它们之间发送和接收数据。由主机102和存储器系统110支持的用于发送和接收数据的通信标准或接口的示例包括通用串行总线(usb)、多媒体卡(mmc)、并行高级技术附件(pata)、小型计算机系统接口(scsi)、增强型小型磁盘接口(esdi)、集成驱动电子设备(ide)、外围组件互连express(pcie或pci-e)、串行附接scsi(sas)、串行高级技术附件(sata)、移动行业处理器接口(mipi)等。根据实施方式,主机接口132是用于与主机102交换数据并且利用被称为主机接口层(hil)的固件来实现或驱动的层的类型。

89.集成驱动电子设备(ide)或高级技术附件(ata)可以用作用于发送和接收数据的接口之一,并且例如可以使用包括并联连接的40条导线的线缆,以支持主机102和存储器系统110之间的数据发送和数据接收。当多个存储器系统110连接到单个主机102时,可以使用多个存储器系统110所连接到的位置或指拨开关(dip switch)将多个存储器系统110划分为主装置和从装置。被设置为主装置的存储器系统110可以用作主存储器装置。ide(ata)可以包括例如快速ata、atapi或增强型ide(eide)。

90.串行高级技术附件(sata)接口是一种串行数据通信接口,其与由集成驱动电子设备(ide)使用的并行数据通信接口的各种ata标准兼容。ide接口中的40条导线可以减少为sata接口中的六条导线。例如,针对ide的40个并行信号可以被转换为针对sata接口的6个串行信号。由于其的更快的数据发送和接收速率及其更少的资源消耗,sata接口已经被广泛使用在用于数据发送和接收的主机102中。sata接口可以将多达30个外部装置连接到包括在主机102中的单个收发器。另外,sata接口可以支持热插拔,即使主机102与另一装置之间的数据通信正被执行,其也允许外部装置附接到主机102或从主机102拆卸。因此,即使当主机102通电时,与通用串行总线(usb)所支持的装置类似,存储器系统110也可以作为附加装置连接或断开。例如,在具有esata端口的主机102中,存储器系统110可以与外部硬盘类似地自由地附接到主机102或从主机102拆卸。

91.小型计算机系统接口(scsi)是一种串行数据通信接口,其用于将计算机或服务器与其它外围装置连接。与诸如ide和sata的其它接口相比,scsi可以提供高的发送速度。在scsi中,主机102和至少一个外围装置(例如,存储器系统110)串联连接,但是可以通过并行数据通信来执行主机102和每个外围装置之间的数据发送和接收。在scsi中,容易将诸如存储器系统110的装置连接到主机102或从主机102断开。scsi可以支持15个其它装置到包括在主机102中的单个收发器的连接。

92.串行附接scsi(sas)可以被理解为scsi的串行数据通信版本。在sas中,主机102和多个外围装置串联连接,并且主机102和每个外围装置之间的数据发送和接收可以以串行数据通信方案执行。此外,sas可以通过串行线缆而不是并行线缆来支持主机102和外围装置之间的连接,以容易地使用sas来管理设备并且增强或提高操作可靠性和通信性能。此外,sas可以支持八个外部装置到包括在主机102中的单个收发器的连接。

93.非易失性存储器express(nvme)是一种至少基于外围组件互连express(pcie)的接口,其被设计为增加装备有非易失性存储器系统110的主机102、服务器、计算装置等的性能和设计灵活性。pcie可以使用用于连接计算装置(例如,主机102)和外围装置(例如,存储器系统110)的插槽或特定线缆。例如,pcie可以使用多个引脚(例如,18个引脚、32个引脚、49个引脚或82个引脚)和至少一条导线(例如,x1、x4、x8或x16)来实现每秒几百mb(例如,250mb/s、500mb/s、984.6250mb/s或1969mb/s)的高速数据通信。根据实施方式,pcie方案可以实现每秒几十千兆比特到几百千兆比特的带宽。nvme可以支持比硬盘更快的非易失性存储器系统110(例如,ssd)的操作速度。

94.根据实施方式,主机102和存储器系统110可以通过通用串行总线(usb)连接。通用串行总线(usb)是一种可扩展的、可热插拔的即插即用串行接口,其可以在主机102和外围装置(例如,键盘、鼠标、操纵杆、打印机、扫描仪、存储装置、调制解调器、视频摄像机等)之间提供成本高效的标准连接。诸如存储器系统110的多个外围装置可以联接到包括在主机102中的单个收发器。

95.纠错电路138可以校正从存储器装置150读取的数据的错误比特,并且可以包括纠错码(ecc)编码器和ecc解码器。ecc编码器可以对将编程在存储器装置150中的数据执行纠错编码,以便于生成将添加了奇偶校验位的经编码数据。经编码数据可以被存储在存储器装置150中。当控制器130读取存储在存储器装置150中的数据时,ecc解码器可以检测和校正包含在从存储器装置150读取的数据中的错误比特。例如,在对从存储器装置150读取的数据执行纠错解码之后,纠错电路138基于纠错解码的结果来确定纠错解码是否已成功,并且输出指令信号(例如,校正成功信号或校正失败信号)。纠错电路138可以使用在ecc编码过程期间针对存储在存储器装置150中的数据生成的奇偶校验位,以便于校正读取数据的错误比特。当错误比特的数量大于或等于可校正错误比特的数量时,纠错电路138可以不校正错误比特,而是可以输出指示校正错误比特的失败的校正失败信号。

96.根据实施方式,纠错电路138可以基于编码调制来执行纠错操作。示例包括低密度奇偶校验(ldpc)码、博斯-chaudhuri-hocquenghem(bch)码、turbo码、里德-所罗门(rs)码、卷积码、递归系统码(rsc)、网格编码调制(tcm)、块编码调制(bcm)等。纠错电路138可以包括用于基于上述代码中的至少一个来执行纠错操作的所有电路、模块、系统和/或装置。在一个实施方式中,纠错电路138可以包括图1所示的控制器130中的组件中的至少一些。

97.ecc解码器可以对从存储器装置150发送的数据执行硬判决解码(hard decision decoding)或软判决解码。硬判决解码可以被理解为针对纠错被大致地分类的两种方法之一。硬判决解码可以包括例如通过从存储器装置150中的非易失性存储器单元读取

‘0’

或

‘1’

的数字数据来校正错误比特的操作。因为硬判决解码处理二进制逻辑信号,所以与软判决解码相比,电路/算法设计或配置可以更简单并且处理速度可以更快。

98.软判决解码可以通过两个或更多个量化值(例如,多比特数据、近似值、模拟值等)

来量化存储器装置150中的非易失性存储器单元的阈值电压,以便于基于两个或更多个量化值来校正错误比特。控制器130可以从存储器装置150中的多个非易失性存储器单元接收两个或更多个字母表(alphabet)或量化值,并且然后基于通过将量化值表征为诸如条件概率或可能性的信息的组合而生成的信息来执行解码。

99.根据实施方式,ecc解码器可以使用针对软判决解码而设计的方法中的低密度奇偶校验和生成器矩阵(ldpc-gm)码。低密度奇偶校验(ldpc)码使用以下算法,该算法可以根据可靠性以数个比特从存储器装置150读取数据的值(而不是如硬判决解码那样简单地读取1或0的数据),并通过消息交换迭代地对其重复以提高值的可靠性。然后,最终将这些值确定为1或0的数据。例如,使用ldpc码的解码算法可以被理解为概率解码。在硬判决解码中,从非易失性存储器单元输出的值可以被编码为0或1。

100.与硬判决解码相比,软判决解码可以基于随机信息确定存储在非易失性存储器单元中的值。关于可以被认为是在存储器装置150中可能出现的错误的比特翻转(bit-flipping),软判决解码可以提供提高的校正错误并恢复数据以及提供经校正数据的可靠性和稳定性的概率。ldpc-gm码可以具有其中内部低密度生成器矩阵(ldgm)码可以与高速ldpc码串联级联的方案。

101.根据实施方式,ecc解码器可以使用例如低密度奇偶校验卷积码(ldpc-cc)来进行软判决解码。ldpc-cc可以与使用基于可变块长度和移位寄存器的流水线解码和线性时间编码的方案相对应。

102.根据实施方式,ecc解码器可以使用例如对数似然比turbo码(llr-tc)进行软判决解码。对数似然比(llr)可以被计算为采样值与理想值之间的距离的非线性函数。另外,turbo码(tc)可以包括两个或三个维度上的简单代码(例如,汉明码),并且在行方向和列方向上重复解码以提高值的可靠性。

103.电源管理单元(pmu)140可以控制提供给控制器130的电力。pmu 140可以监测提供给存储器系统110的电力(例如,提供给控制器130的电压),并且将电力提供给包含在控制器130中的组件。pmu 140不仅可以检测通电或断电,而且还可以生成触发信号,以使得存储器系统110能够在提供给存储器系统110的电力不稳定时紧急地备份当前状态。根据实施方式,pmu 140可以包括能够累积可以在紧急情况下使用的电力的装置或组件。

104.存储器接口142可以用作用于处理在控制器130与存储器装置150之间传送的命令和数据的接口,以便于允许控制器130响应于从主机102输入的命令或请求来控制存储器装置150。当存储器装置150是闪存存储器时,存储器接口142可以在处理器134的控制下生成用于存储器装置150的控制信号,并且可以处理输入到存储器装置150或从存储器装置150输出的数据。

105.例如,当存储器装置150包括nand闪存存储器时,存储器接口142包括nand闪存控制器(nfc)。存储器接口142可提供用于处理在控制器130与存储器装置150之间传送的命令和数据的接口。根据实施方式,存储器接口142可以通过用于与存储器装置150交换数据的被称为闪存接口层(fil)的固件来实现或由其驱动。

106.根据实施方式,存储器接口142可以支持用于与存储器装置150的数据输入/输出的开放nand闪存接口(onfi)、切换模式等。例如,onfi可以使用包括能够以8比特或16比特数据为单位支持双向发送和接收的至少一个信号线的数据路径(例如,信道、通路等)。控制

器130和存储器装置150之间的数据通信可以通过关于异步单数据速度(sdr)、同步双倍数据速度(ddr)、切换双倍数据速度(toggle double data rate,ddr)等的至少一个接口来实现。

107.存储器144可以在临时存储在存储器系统110和控制器130中执行的操作的事务性数据的同时用作存储器系统110或控制器130的工作存储器。例如,存储器144可以在读取数据输出到主机102之前响应于来自主机102的读取请求而临时存储从存储器装置150输出的读取数据。

108.此外,控制器130可以在将写入数据编程到存储器装置150中之前将从主机102输入的写入数据临时存储在存储器144中。当控制器130控制存储器装置150的操作(例如,数据读取操作、数据写入或编程操作、数据擦除操作等)时,可以将在控制器130与存储器系统110的存储器装置150之间发送的数据临时存储在存储器144中。

109.除了读取数据或写入数据之外,存储器144还可以存储用于在主机102与存储器装置150之间输入或输出数据的信息(例如,映射数据、读取请求、编程请求等)。根据实施方式,存储器144可以包括命令队列、程序存储器、数据存储器、写入缓冲器/高速缓存、读取缓冲器/高速缓存、数据缓冲器/高速缓存、映射缓冲器/高速缓存等中的一个或更多个。控制器130可以针对被建立以执行数据输入/输出操作的组件分配存储器144中的一些存储空间。例如,在存储器144中建立的写入缓冲器可以用于临时存储进行编程操作的目标数据。

110.在一个实施方式中,可以利用易失性存储器来实现存储器144。例如,存储器144可以用静态随机存取存储器(sram)、动态随机存取存储器(dram)或两者来实现。尽管图2例示了设置在控制器130内的存储器144,但是实施方式不限于此。存储器144可以位于控制器130内或控制器130外部。例如,存储器144可以由具有用于在存储器144和控制器130之间传送数据和/或信号的存储器接口的外部易失性存储器来实现。

111.处理器134可以控制存储器系统110的整体操作。例如,处理器134可以响应于从主机102输入的写入请求或读取请求而控制存储器装置150的编程操作或读取操作。根据实施方式,处理器134可以执行固件以控制存储器系统110中的编程操作或读取操作。固件可以是例如闪存转换层(ftl)。根据实施方式,处理器134可以用微处理器、中央处理单元(cpu)或另一处理装置来实现。

112.根据实施方式,存储器系统110可以利用至少一个多核处理器来实现。多核处理器是一种其中集成了被认为是不同的处理区域的两个或更多个核的电路或芯片。例如,当多核处理器中的多个核独立地驱动或执行多个闪存转换层(ftl)时,可以提高存储器系统110的数据输入/输出速度(或性能)。根据实施方式,存储器系统110中的数据输入/输出(i/o)操作可以通过多核处理器中的不同核独立地执行。

113.控制器130中的处理器134可以执行与从主机102输入的请求或命令相对应的操作。此外,存储器系统110可以独立于从主机102输入的命令或请求来执行操作。在一种情况下,由控制器130响应于从主机102输入的请求或命令而执行的操作可以被视为前台操作,而由控制器130独立于从主机102输入的请求或命令而执行的操作可以被视为后台操作。控制器130可以执行前台操作或后台操作以用于读取、写入或擦除存储器装置150中的数据。另外,与作为从主机102发送的设置命令的设置特征命令或设置参数命令相对应的参数设置操作可以被视为前台操作。作为可以在没有从主机102发送的命令的情况下执行的后台

操作的示例,控制器130可以执行垃圾收集(gc)、损耗均衡(wl)、用于标识和处理坏块的坏块管理等。

114.根据实施方式,可以执行基本相似的操作作为前台操作和后台操作二者。例如,当存储器系统110响应于从主机102输入的请求或命令执行垃圾收集(例如,手动gc)时,垃圾收集可以被认为是前台操作。当存储器系统110独立于主机102执行垃圾收集(例如,自动gc)时,垃圾收集可以被认为是后台操作。

115.当存储器装置150包括各自包含多个非易失性存储器单元的多个管芯(或多个芯片)时,控制器130可以执行针对从主机102输入的多个请求或命令的并行处理以便于提高存储器系统110的性能。例如,所发送的请求或命令可以被划分为包括包含在存储器装置150中的多个平面、多个管芯或多个芯片中的至少一些的多个组,并且该多个组的请求或命令在每个平面、每个管芯或每个芯片中被独立地或并行地处理。

116.控制器130中的存储器接口142可以通过至少一个信道和至少一个通路连接到存储器装置150中的多个管芯或芯片。当控制器130响应于与包括非易失性存储器单元的多个页相关联的请求或命令而通过每个信道或每个通路将数据分配并存储在多个管芯中时,可以同时或并行地在多个管芯或平面中执行与请求或命令相对应的多个操作。这样的处理方法或方案可以被认为是交织方法。因为存储器系统110的数据输入/输出速度通过利用交织方法操作而增大,所以可以提高存储器系统110的数据i/o性能。

117.作为示例而非限制,控制器130可以识别与包括在存储器装置150中的多个管芯相关联的多个信道(或多个通路)的状态。控制器130可以将每个信道或每个通路的状态确定为忙碌状态、就绪状态、活动状态、空闲状态、正常状态和异常状态中的一个。由控制器130通过哪个信道或通路传递指令(和/或数据)的确定可以与物理块地址相关联。控制器130可以参考从存储器装置150传递的描述符。描述符可以包括描述关于存储器装置150的某些事项的参数的块或页。描述符可以具有预定的格式或结构。例如,描述符可以包括装置描述符、配置描述符、单位描述符等。控制器130可以参考或使用描述符来确定哪个(哪些)信道或通路用于交换指令或数据。

118.如上所述,存储器系统110中的存储器装置150可以包括一个或更多个存储块152、154、156。存储块152、154、156中的每一个包括多个非易失性存储器单元。根据实施方式,存储块152、154、156中的每一个可以是一起被擦除的一组非易失性存储器单元。存储块152、154、156可以包括作为一起读取或编程的一组非易失性存储器单元的多个页。

119.在实施方式中,存储块152、154、156中的每一个可以具有三维层叠结构以用于高集成度。此外,存储器装置150可以包括多个管芯,每个管芯包括多个平面,每个平面包括存储块152、154、156。存储器装置150的配置可以根据存储器系统110的性能而改变。

120.在图2中,存储器装置150包括存储块152、154和156,其基于可以存储在一个存储器单元中的比特的数量而可以是单级单元(slc)存储块、多级单元(mlc)存储块等中的任意一个。slc存储块包括由存储器单元实现的多个页,每个存储器单元存储一比特数据。slc存储块可以具有比mlc存储块更高的数据i/o操作性能和更高的耐久性。mlc存储块包括由存储器单元实现的多个页,其中每个存储器单元存储多比特数据(例如,两个或更多比特数据)。与slc存储块相比,mlc存储块针对相同空间可以具有更大的存储容量。mlc存储块在存储容量方面可以是高度集成的。

121.在实施方式中,存储器装置150可以利用mlc存储块(例如,双级单元(dlc)存储块、三级单元(tlc)存储块、四级单元(qlc)存储块及其组合)来实现。dlc存储块可包括由存储器单元实现的多个页,其中每个存储器单元能够存储2比特数据。tlc存储块可以包括由存储器单元实现的多个页,其中每个存储器单元能够存储3比特数据。qlc存储块可以包括由存储器单元实现的多个页,其中每个存储器单元能够存储4比特数据。在另一实施方式中,存储器装置150可以利用包括由存储器单元实现的多个页的块来实现,其中每个存储器单元能够存储五个或更多比特数据。

122.根据实施方式,控制器130可以将包括在存储器装置150中的mlc存储块用作在一个存储器单元中存储一比特数据的slc存储块。多级单元(mlc)存储块的数据输入/输出速度可以比slc存储块的数据输入/输出速度更慢。例如,当mlc存储块用作slc存储块时,可以减少读取操作或编程操作的裕度。例如,当mlc存储块用作slc存储块时,控制器130可以以更高速度执行数据输入/输出操作。因此,控制器130可以将mlc存储块用作slc缓冲器来临时存储数据,因为缓冲器可能需要高数据输入/输出速度来提高存储器系统110的性能。

123.根据实施方式,控制器130可以多次将数据编程在mlc中,而不对包括在存储器装置150中的特定mlc存储块执行擦除操作。通常,非易失性存储器单元不支持数据重写。然而,控制器130可以使用mlc能够存储多比特数据的特征多次在mlc中编程1比特数据。针对mlc重写操作,当在mlc中编程1比特数据时,控制器130可以将编程次数存储为单独的操作信息。根据实施方式,可以在在同一mlc中编程另一1比特数据之前执行mlc(每个mlc具有存储的一比特数据)的均匀地均衡阈值电压的操作。

124.在实施方式中,存储器装置150被实现为诸如闪存存储器的非易失性存储器,例如,nand闪存存储器、nor闪存存储器等。在另一实施方式中,存储器装置150可以由相变随机存取存储器(pcram)、铁电随机存取存储器(fram)、自旋转移力矩随机存取存储器(stt-ram)和自旋转移力矩磁性随机存取存储器(stt-mram)等中的至少一个来实现。

125.图3例示根据本公开的实施方式的在存储器装置中执行的擦除操作期间在沟道中生成电荷的现象。具体地,图3作为示例描述了的图1中描述的串340的截面。串340的截面中的层的形状或厚度可以根据存储器装置150的制造工艺和串340的(2d或3d)结构的特性而变化。

126.参照图3,半导体基板(p-sub)可以是p型硅半导体。可以在距半导体基板(p-sub)的表面的预设深度处形成袋状p型阱区域(pp阱)。袋状p型阱区域(pp阱)可以被n型阱区域围绕。在袋状p型阱区域(pp阱)中,掺杂有n型杂质的n+掺杂区域可以利用插置于其间的沟道区域而彼此隔离。非易失性存储器单元的控制栅极可以形成在n+掺杂区域之间。

127.在擦除操作期间,可以将具有比电源电压的电平显著更高的电平的擦除电压vers施加到设置有多个非易失性存储器单元的块体(pp阱)。当将高电平电压施加到块体时,也可以通过pn结正向偏置将高电压施加到位线bl或公共源极线csl。此外,施加到块体的高电平电压可以影响布置在非易失性存储器单元的控制栅极之间的n+掺杂区域。例如,擦除电压vers可以具有比15v更高的电平,而电源电压具有比3v至5v更小的电平。联接在多个非易失性存储器单元和位线bl或公共源极线csl之间的晶体管可以是在施加高电平电压的情况下可耐久和可操作的一种高压晶体管。另外,高电平电压不应直接施加到低电压电路(例如,在使用低电平电源电压的情况下操作的页缓冲器或位线驱动器)。

128.参照图1和图3,由于存储器装置150的结构,当在擦除操作期间将具有高电平的擦除电压vers施加到块体(pp阱)时,可以在串340的沟道中累积电荷。因为在串340的沟道中累积的电荷可能干扰擦除操作,所以存储器装置150可以将接地电压施加到位线bl和公共源极线csl,以通过位线bl和公共源极线csl对在沟道中累积的电荷进行放电。

129.在图3中,已经作为示例描述了擦除电压vers被施加到块体(pp阱)。然而,根据实施方式,可以将擦除电压vers施加到位线bl和公共源极线csl,以擦除存储在多个非易失性存储器单元中的数据。

130.图4例示根据本公开的实施方式的用于擦除存储在非易失性存储器单元中的数据的方法。

131.参照图4,当图2所描述的控制器130将擦除命令发送到存储器装置150时,存储器装置150可以开始擦除操作(操作220)。根据实施方式,控制器130可以将指示至少一个存储块的地址与擦除命令一起发送到存储器装置150。存储器装置150可以基于从控制器130发送的地址确定将执行擦除操作的范围。

132.存储器装置150可以设置针对擦除操作待施加到与存储块相对应的阱区域的擦除电压vers的电平(操作222)。根据实施方式,可以基于非易失性存储器单元的操作特性来确定擦除电压vers的电平。此外,可以根据存储器装置150的操作状态(例如,磨损水平)或操作条件(例如,温度等)来调整擦除电压vers的电平。

133.存储器装置150可以建立针对擦除操作施加到存储块中的每一串的栅极电压(操作224)。在这种情况下,栅极电压可以包括施加到连接到非易失性存储器单元的字线的电压和通过漏极选择线dsl和源极选择线ssl施加的电压。此外,栅极电压可以包括用于确定接地电压是否被施加到公共源极线csl和位线bl的控制信号。

134.当确定了针对擦除操作的擦除电压vers和栅极电压的电平时,可以将所确定的电压电平施加到存储块(操作226)。当擦除电压vers被施加到存储块所在的阱区域并且栅极电压通过联接到存储块的字线施加时,存储在存储块中的非易失性存储器单元中的数据可以被擦除。

135.参照图1和图3至图4,当存储器装置150将擦除电压vers施加到存储块所在的阱区域时,电荷在串340的沟道中累积。存储器装置150可以对串340的沟道中的电荷进行放电(操作228)。根据实施方式,为了控制用于对串340的沟道中的电荷进行放电的速度或时间,存储器装置150可以控制被配置为将接地电压施加到位线bl或公共源极线csl的晶体管。例如,存储器装置150可以调整施加到将接地电压施加到位线bl或公共源极线csl的晶体管的栅极的栅极电压的电平,或调整将接地电压施加到位线bl或公共源极线csl的导通晶体管的数量。存储器装置150可以控制或改变电荷通过其从串340的沟道被放电的路径,以使对通过位线bl和公共源极线csl放电的在沟道中累积的电荷放电的速度或时间同步。

136.存储器装置150可以验证存储于存储块中的数据是否被擦除(操作230)。当从存储块擦除了数据时(操作230的通过),存储器装置150可以终止擦除操作(操作234)。另一方面,当未擦除存储块中的所有数据时(操作230的失败),存储器装置150可以调整或改变针对擦除操作建立的电压电平(操作232)。例如,当数据未被擦除时,可以针对擦除操作增大擦除电压vers的电平。此外,根据实施方式,存储器装置150可以确定栅极电压不被施加到联接到其中数据未被擦除的非易失性存储器单元的字线。当调整或改变针对擦除操作施加

的电压时(操作232),存储器装置150可以将具有经调整的电平的电压施加到存储块(操作226)。

137.图5例示根据本公开的实施方式的用于控制存储器装置的位线的电路。

138.参照图5,串340可以联接到源极线sl和位线bl。在本文中,源极线sl可以与参照图1描述的公共源极线csl相对应。

139.位线bl可以通过页缓冲器控制信号pbsense联接到页缓冲器322、324、326(参照图1)。在读取操作或验证操作期间,可以通过位线bl输出所感测数据so。

140.位线bl可以由位线选择信号sel_bl控制。例如,位线选择信号sel_bl可以在读取操作期间输出通过位线bl发送的数据,或者在擦除操作期间向位线bl施加接地电压vssi。

141.在一个实施方式中,可以基于擦除电压施加信号verasetobl将擦除电压vers施加到位线bl。因为擦除电压vers具有高电压电平,所以擦除电压施加信号verasetobl可以被施加到被设计为即使在施加了高电平电压时也能避免出现操作问题的晶体管。

142.例如,当擦除电压施加信号verasetobl在擦除操作期间变为逻辑高电平(h)时,可以将擦除电压vers施加到位线bl,并且位线选择信号sel_bl可以是逻辑低电平(l)。当经过用于从非易失性存储器单元擦除数据的时间或操作间隔时,擦除电压施加信号verasetobl可以变为逻辑低电平(l)。另外,为了对累积在串340的沟道中的电荷进行放电,位线选择信号sel_bl和位线放电信号bldis可以是逻辑高电平(h)。通过这些方法,可以对累积在串340的沟道中的电荷进行放电,使得沟道的电位变为0v。

143.在擦除操作期间,可以将接地电压vssi施加到位线bl以对累积在串340的沟道中的电荷进行放电。当位线放电信号bldis被激活时,接地电压vssi可以被施加到位线bl。通过调整位线放电信号bldis的电压电平,可以调整或改变通过位线bl对串340的沟道中累积的电荷进行放电的速度或时间。

144.图6例示根据本公开的实施方式的用于控制存储器装置的公共源极线的电路。

145.参照图6,多个晶体管并联联接到源极线sl。源极线sl可以与参照图1描述的公共源极线csl相对应。在擦除操作期间,响应于擦除电压施加信号verasetosl,可以将擦除电压vers施加到源极线sl。可以施加到不同位置的图6所描述的擦除电压施加信号verasetosl和图5所描述的擦除电压施加信号verasetobl可以被同时激活或去激活。因为擦除电压vers具有高电平,所以擦除电压施加信号verasetosl可以被施加到被设计为即使在施加高电平电压时也避免出现操作问题的晶体管。

146.例如,当擦除电压施加信号verasetosl在擦除操作期间变为逻辑高电平(h)时,可以将擦除电压vers施加到源极线sl。当经过用于从非易失性存储单元擦除数据的时间或操作间隔时,擦除电压施加信号verasetosl可以变为逻辑低电平(l)。另外,为了对累积在串340的沟道中的电荷进行放电,源极线放电信号sltognd、sltognd_slow《0:2》可以具有逻辑高电平(h)。通过该方法,可以对累积在串340的沟道中的电荷进行放电,使得沟道的电位变为0v。

147.根据实施方式,可以激活所有源极线放电信号sltognd、sltognd_slow《0:2》以便快速地对在串340的沟道中累积的电荷进行放电。此外,可以激活源极线放电信号sltognd、sltognd_slow《0:2》的一部分以对在串340的沟道中累积的电荷缓慢地放电。导通以将接地电压vssi施加到沟道的晶体管的数量可以基于有多少个源极线放电信号sltognd、

sltognd_slow《0:2》被激活而变化。通过该方法,可以调整或改变通过源极线sl对串340的沟道中累积的电荷进行放电的速度或时间。

148.参照图5和图6,因为联接到位线bl的组件(例如,页缓冲器等)被包括在存储器装置150中,可能难以增加联接到位线bl的晶体管的数量以通过位线bl对串340的沟道中累积的电荷进行放电。然而,增加将接地电压施加到源极线sl的晶体管的数量的配置可以比增加将接地电压施加到位线bl的晶体管的数量的配置更简单地实现。

149.参照图1,多个非易失性存储器单元通过单个位线bl联接到页缓冲器。另一方面,与公共源极线csl类似,源极线sl可以联接到多个串340。由于该结构差异,存在于位线bl和公共源极线csl中的寄生电容可以是不同的。例如,公共源极线csl的寄生电容可以大于位线bl的寄生电容。因此,通过公共源极线csl和位线bl对在串340的沟道中累积的电荷进行放电的速率或时间可以是不同的。

150.图7例示根据本公开的实施方式的在存储器装置中执行的擦除操作期间的沟道放电。

151.参照图7,存储器装置150可以在擦除操作期间使用用于将擦除电压vers施加到联接到串340的位线bl和源极线sl的擦除电压施加信号verasetobl、verasetosl。当擦除电压施加信号verasetobl、verasetosl被施加时,位线bl和源极线sl的电位可以持续上升。

152.在经过用于从多个非易失性存储器单元擦除数据的时间或操作间隔之后,擦除电压施加信号verasetobl、verasetosl被去激活,并且在串340的沟道中累积的电荷可以通过位线bl和源极线sl被放电。

153.参照图7,在串340中的沟道中累积的电荷通过位线bl和源极线sl以不同速率放电,使得位线bl和源极线sl的电位下降至0v的斜率不同。如上所述,当位线放电信号bldis被激活时,电荷通过位线bl快速放电。但是,基于源极线放电信号sltognd、sltognd_slow《0:2》是否被激活,可以不同地控制通过源极线sl对电荷进行放电的速率。

154.根据实施方式,为了使通过位线bl和源极线sl对在串340中的沟道中累积的电荷进行放电的速率或时间同步,存储器装置150可以使用源极线放电信号sltognd、sltognd_slow《0:2》来增加通过源极线sl对电荷进行放电的速率,或者使用位线放电信号bldis来减小通过位线bl对电荷进行放电的速率。

155.图8例示根据本公开的实施方式的在存储器装置中执行的擦除操作期间通过位线和公共源极线对串的沟道中的电荷进行放电的操作。

156.参照图8,累积在串340的沟道中的电荷可以通过位线bl和源极线sl被放电。当在擦除电压vers或擦除脉冲被施加到串340之后在沟道中累积的电荷被放电时,可以在沟道和字线之间形成耦合电容。形成在沟道和字线之间的耦合电容可能引起字线wl被负向下耦合(negatively down-coupled)的负升压或欠耦合(under coupling)。在这种情况下,可能出现非易失性存储器单元的特性根据串340中的非易失性存储器单元的位置而改变的现象。当非易失性存储器单元的特性不同时,存储器装置150的操作可靠性可能劣化。为了避免该问题,存储器装置150可以减慢通过位线bl和源极线sl进行放电的速度。然而,当速度减慢时,擦除操作的性能可能劣化。

157.在本公开的实施方式中,当串的沟道中的电荷通过位线和公共源极线放电时,可以响应于电荷通过源极线的第二放电速率来改变或调整电荷通过位线的第一放电速率,使

得可以使第一放电速率和第二放电速率(或两个放电时间)同步。

158.图9例示根据本公开的实施方式的用于使在存储器装置中通过位线和公共源极线进行的放电同步的方法。

159.参照图9,可以增加(sl快放电)或降低(sl慢放电)通过源极线sl对电荷进行放电的速度。例如,如图6所描述的,基于源极线放电信号sltognd、sltognd_slow《0:2》中的激活信号的数量,可以调整或改变通过源极线sl对串340的沟道中的电荷进行放电的速度。响应于通过源极线sl对电荷进行放电的速度,存储器装置150在不同时段期间施加具有各种电平vref1、vref2、vref3、vref4中的一者的位线放电信号bldis。通过该方法,可以调整或改变通过位线bl对串340的沟道中的电荷进行放电的速度。

160.为了使通过位线bl和源极线sl对串340中的沟道中累积的电荷进行放电的速度或时间同步,存储器装置150可以将控制信息存储在寄存器中。用于控制通过源极线sl对电荷进行放电的速度的控制信息可以包括多少源极线放电信号sltognd、sltognd_slow《0:2》被激活多长时间。基于控制信息,存储器装置150可以调整或改变位线放电信号bldis的电平以控制通过位线bl对电荷进行放电的速度。参照图9,当可能估计通过源极线sl对电荷进行放电的速度为快(sl快放电)时,存储器装置150可以施加第一电平vref1和第二电平vref2以快速增加位线放电信号bldis的电平。当可能估计通过源极线sl对电荷进行放电的速度为慢(sl慢放电)时,存储器装置150可以施加第三电平vref3和第四电平vref4以缓慢增加位线放电信号bldis的电平。根据施加到位线放电信号bldis的电压电平vref1、vref2、vref3、vref4,通过位线bl对电荷进行放电的速度(或时间)可以增加或减少(短或长)。

161.参照图10至图12,下文将描述用于使通过位线bl和源极线sl对串340的沟道中累积的电荷进行放电的速率或时间同步的实施方式。

162.图10例示根据本公开的实施方式的用于使放电同步的第一示例。

163.参照图10,为了使通过位线bl和源极线sl对串340的沟道中累积的电荷进行放电的速度或时间同步,随着为了通过源极线sl对电荷进行放电而激活的晶体管的数量增加,存储器装置150可以增大位线放电信号bldis的电压电平。这里,激活的晶体管的数量可以与源极线放电信号sltognd、sltognd_slow《0:2》当中的激活信号的数量相对应。

164.如参照图9所描述的,存储器装置150可以通过存储在寄存器中的值来识别源极线放电信号sltognd、sltognd_slow《0:2》当中的激活信号的数量,并且然后基于识别出的数量来控制或调整位线放电信号bldis的电平。

165.图11例示了根据本公开的实施方式的用于使放电同步的第二示例。

166.参照图11,为了使通过位线bl和源极线sl对串340的沟道中累积的电荷进行放电的速度或时间同步,随着为了通过源极线sl对电荷进行放电而激活的晶体管的数量增加,存储器装置150可以减少通过位线bl对电荷进行放电的时间。例如,存储器装置150可以增大位线放电信号bldis的电压电平(vref电平)以减少通过位线bl对电荷进行放电的时间。

167.图12例示了根据本公开的实施方式的用于使放电同步的第三示例。

168.参照图12,存储器装置150可以基于在源极线sl和位线bl中生成的放电电流使通过位线bl和源极线sl对串340的沟道中累积的电荷进行放电的速度或时间同步。与参照图10描述的其中调整和改变位线放电信号bldis的电压电平的实施方式不同,根据参照图12描述的实施方式的存储器装置150可以生成控制电流或参考电流(电流ref)并且将控制电

流或参考电流(电流ref)施加到用于通过源极线sl对电荷进行放电的晶体管和用于通过位线bl对电荷进行放电的晶体管。当由存储器装置150施加的控制电流或参考电流(电流ref)的量增大时,放电速度可以增大。当控制电流或参考电流(电流ref)的量减小时,放电速度可以减小。在存储器装置150中,施加到用于通过源极线sl对电荷进行放电的晶体管的控制电流或参考电流(电流ref)可以与施加到用于通过位线bl对电荷进行放电的晶体管的控制电流或参考电流(电流ref)不同。即使这些电流不相同,这些电流也可能具有相似的趋势(例如,两个电流可以一起增大或减小)。也就是说,存储器装置150可以确定控制电流或参考电流(电流ref)在递减或递增的相同方向上的改变。

169.参照图10至图12,根据实施方式,为了使通过位线bl和源极线sl对串340的沟道中累积的电荷进行放电的速度或时间同步,存储器装置150可以调整或改变电压电平、电流量和/或放电时间。

170.如上所述,当存储器装置执行擦除操作时,根据本公开的实施方式的存储器装置可以通过位线和公共源极线以相同的速率对已经出现在串的沟道中的电荷进行放电,使得可以与非易失性存储器单元的位置无关地在擦除操作期间更有效地擦除数据。

171.另外,根据本公开的实施方式的存储器装置可以减少在用于擦除存储在非易失性存储器单元中的数据的擦除操作期间可以根据非易失性存储器单元位置而出现的特性差异,从而提高非易失性存储器单元的操作可靠性。

172.本文描述的方法、过程和/或操作可以通过将由计算机、处理器、控制器或其它信号处理装置执行的代码或指令来执行。计算机、处理器、控制器或其它信号处理装置可以是本文描述的那些或除了本文描述的元件之外的元件。因为形成方法(或计算机、处理器、控制器或其它信号处理装置的操作)的基础的算法被详细描述,用于实现方法实施方式的操作的代码或指令可以将计算机、处理器、控制器或其它信号处理装置变换成用于执行本文中的方法的专用处理器。

173.此外,另一实施方式可以包括用于存储上述代码或指令的计算机可读介质(例如,非暂时性计算机可读介质)。计算机可读介质可以是易失性存储器或非易失性存储器或其它存储装置,其可以可移除地或固定地联接到要执行用于执行本文中的设备实施方式的操作或方法实施方式的代码或指令的计算机、处理器、控制器或其它信号处理装置。

174.本文中所公开的实施方式的控制器、处理器、控制电路、装置、模块、单元、复用器、逻辑、接口、解码器、驱动器、生成器和其它信号发生和信号处理特征可以例如在可以包括硬件、软件或两者的非暂时性逻辑中实现。当至少部分地以硬件实现时,控制器、处理器、控制电路、装置、模块、单元、复用器、逻辑、接口、解码器、驱动器、生成器和其它信号发生和信号处理特征可以是例如各种集成电路中的任意一个,各种集成电路包括但不限于专用集成电路、现场可编程门阵列、逻辑门的组合、片上系统、微处理器或另一类型的处理或控制电路。

175.当至少部分地以软件实现时,控制器、处理器、控制电路、装置、模块、单元、复用器、逻辑、接口、解码器、驱动器、生成器和其它信号发生和信号处理特征可以包括例如用于存储要由例如计算机、处理器、微处理器、控制器或其它信号处理装置执行的代码或指令的存储器或其它存储装置。计算机、处理器、微处理器、控制器或其它信号处理装置可以是本文描述的那些或除了本文描述的元件之外的元件。

176.虽然已经关于特定实施方式例示和描述了本教导,但是本领域技术人员根据本公开将显而易见的是,可以在不脱离如所附权利要求所限定的本公开的精神和范围的情况下进行各种改变和修改。此外,实施方式可以被组合以形成另外的实施方式。

177.相关申请的交叉引用

178.本专利申请要求于2021年7月16日提交的韩国专利申请no.10-2021-0093236的权益,其全部公开内容通过引用并入本文。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1