一种存储装置的制作方法

1.本实用新型涉及存储装置领域,更具体地说,涉及一种存储装置。

背景技术:

2.存储装置作为数据存储以及转移设备,其广泛的运用在现时生活及工作中。现有的存储装置都是通过sip技术进行封装的,该技术整合了pcb基板组装及半导体封装制作流程,运用该技术将小型存储产品所需要的零部件直接封装而形成的存储卡成品。可以使数码存储产品达到完全的防水、耐高温、耐高压、读写速度快的效果,在各种恶劣的环境下依然能够正常使用,使数据得到更安全可靠的保存。该技术主要应用在数码存储卡上,如:udp模块、sd 卡、mmc卡等。

3.但是,基于sip技术进行封装的存储装置,其在存储装置实际运行时会出现存储装置不被电脑或手机(主机端)识别的问题,这个时候需要对存储装置进行除错操作,以求实现存储装置的正常工作,相关技术中是通过把存储装置上的封装胶体给磨掉,来进行除错。但是此举对于除错操作非常不方便。

技术实现要素:

4.本实用新型的主要目的在于提供一种存储装置,旨在解决存储装置的除错操作极为不便的技术问题。

5.为实现上述目的,本实用新型提供一种存储装置,所述存储装置包括:基板、控制芯片、存储芯片、封装胶体以及连接器;所述控制芯片和存储芯片分别与所述基板电性连接,且所述控制芯片、存储芯片及基板封装在所述封装胶体内,所述连接器焊接在所述封装胶体的第一表面上;所述控制芯片包括存储器接口和连接接口,且所述存储器接口经由所述基板与所述存储芯片电性连接;

6.所述封装胶体的第一表面上还包括除错接点触片,所述除错接点触片经由所述基板与所述连接接口的使能信号引脚电性连接。

7.进一步,所述连接接口的使能信号引脚为xfaleo引脚,所述除错接点触片经由所述基板与所述xfaleo引脚电性连接。

8.进一步,所述连接接口还包括vcc5a引脚、xrxp引脚、xrxn引脚、dm 引脚、gnd1引脚、dp引脚、xtxp引脚、xtxn引脚和gnd2引脚;所述封装胶体的第一表面还包括导电触片组,所述导电触片组包括第一数据触片、第二数据触片、第三数据触片、第四数据触片、第五数据触片、第六数据触片、电源信号触片、第一地信号触片和第二地信号触片,且所述电源信号触片经由所述基板与所述vcc5a引脚电性连接,第一数据触片经由所述基板与所述dm引脚电性连接,第二数据触片经由所述基板与所述dp引脚电性连接,第二地信号触片经由所述基板与所述gnd2引脚电性连接,第三数据触片经由所述基板与所述xrxn引脚电性连接,第四数据触片经由所述基板与所述xrxp引脚电性连接,第五数据触片经由所述基板与所述xtxn引脚电性连接,第六数据触片经由所述基板与所述xtxp引脚电性连接,第一地信号触

片经由所述基板与所述gnd1引脚电性连接。

9.进一步,所述导电触片组和所述除错接点触片沿着所述封装胶体的长度方向排列设置,且所述导电触片组和所述除错接点触片设置在所述封装胶体的长度方向的端部。

10.进一步,所述封装胶体的第一表面还包括焊接触片组,所述焊接触片组包括第一焊接触片和第二焊接触片。

11.进一步,所述连接器包括第一端子组和第二端子组,所述第一端子组电性连接至所述导电触片组,所述第二端子组和所述焊接触片组焊接。

12.进一步,所述连接器为usb3.0连接器。

13.进一步,所述封装胶体的长度为24.8mm,所述封装胶体的宽度为11.3mm,所述封装胶体的厚度为1.4mm。

14.进一步,所述封装胶体的长度为15mm,所述封装胶体的宽度为11.3mm,所述封装胶体的厚度为1.4mm。

15.本实用新型具有以下有益效果:在存储装置的第一表面上设置除错接点,将除错接点连接于控制芯片的使能信号引脚上,将除错接点裸露在外,存储装置正常使用时,通过连接器将所述除错接点触片遮盖住,防止其氧化短路;在需要对存储装置进行除错操作时,只需要将连接器从存储装置中拆下,连接到裸露在外的除错接点,从而可以接入到存储装置的控制芯片中,强制存储装置必须识别控制芯片,这个时候不和存储芯片通讯,进而实现对存储装置的除错操作,此举使得对存储装置的除错操作非常简单方便。

附图说明

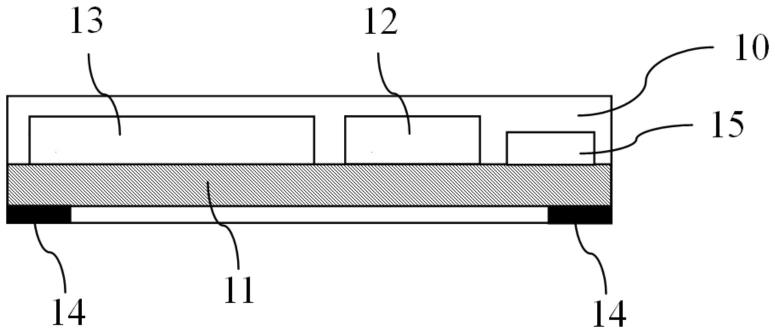

16.图1是本实用新型实施例提供的存储装置的剖面结构示意图;

17.图2是本实用新型实施例提供的存储装置的电连接示意图;

18.图3为本实用新型实施例提供的存储装置的立体示意图;

19.图4为本实用新型实施例提供的存储装置的平面示意图;

20.图5是本实用新型实施例提供的存储装置的连接接口和导电触片组电连接示意图;

21.图6为本实用新型实施例提供的连接器的示意图;

22.图7为本实用新型实施例提供的焊接有连接器的存储装置的示意图。

具体实施方式

23.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

24.如图1-图2所示,是本实用新型实施例提供的存储装置的结构示意图,该存储装置可应用于手机、数码相机、便携式电脑、mp3等电子设备上,并实现相应数据的存储。本实施例的存储装置包括基板11、控制芯片12、存储芯片13 以及封装胶体10,其中控制芯片12和存储芯片13分别与基板11电性连接,且控制芯片12、存储芯片13及基板11封装在封装胶体10内。此外,上述封装胶体10 内还可封装有多个被动元件15,例如电阻、电容等,这些被动元件15分别与基板11电性连接,并与控制芯片12、存储芯片13共同组成电路,让存储装置可

以实现数据存取的功能。

25.存储芯片13具体可以为nand flash等存储介质131构成,控制芯片12是存储装置的控制器,其用于提供标准接口并管理存储芯片13中的存储单元。在本实用新型的一个实施例中,其可由裸晶(die)构成,其表面分别具有多个接合焊盘。在实际应用中,控制芯片12和存储芯片13也可先封装在一起。基板11即为导线架(substrate),用于承载控制芯片12、存储芯片13及被动元件15,其主要由基板(具体可以为硬质基板、柔性薄膜基板和共烧陶瓷基板等)和位于基板上的铜箔(其厚度可以在1.5μm-18μm之间)构成,且该基板11上具有多个基板焊盘,基板焊盘之间通过铜箔电性连接。基板11不仅可实现控制芯片12、存储芯片13及被动元件15等的固定和热传导,而且可实现控制芯片12、存储芯片13及被动元件15之间的电性连接。具体地,控制芯片12、存储芯片13粘结在基板11的表面,并通过引线键合(wire bonding)工艺将接合焊盘与基板焊盘电性连接。通过控制芯片12、存储芯片13及被动元件15,可实现存储装置的相关功能。基板11、控制芯片12、存储芯片13各自的结构及其电性连接结构属于本领域的习知技术,在此不再赘述。

26.上述控制芯片12具体包括控制电路121、存储器接口122和连接接口123,其中控制电路121用于控制所述控制芯片12的整体运作。具体来说,控制电路 121具有多个控制指令,并且在存储装置运作时,这些控制指令会被执行以进行数据的写入、读取与擦除等运作。

27.具体地,存储器接口122经由基板11与存储芯片13电性连接,并用于存取存储介质131。也就是说,欲写入至存储介质131的数据会经由存储器接口122 转换为存储介质131所能接受的格式。具体来说,若控制电路121要存取存储介质131,存储器接口122会传送对应的指令序列。例如,这些指令序列可包括指示写入数据的写入指令序列、指示读取数据的读写指令序列、指示擦除数据的擦除指令序列、以及用于指示各种存储器操作(例如,改变读取电压电平或执行垃圾回收操作等等)的相对应的指令序列。这些指令序列例如是由控制电路121产生并且通过存储器接口122传送至存储介质131。这些指令序列可包括一或多个信号,或是在总线上的数据。这些信号或数据可包括指令码或程序码。例如,在读写指令序列中,会包括读取的识别码、存储器地址等信息。

28.具体地,连接接口123是电性连接至控制电路121并且用于接收与识别主机端所传送的指令与数据。也就是说,主机端所传送的指令与数据会通过连接接口123来传送至控制电路121。

29.进一步,连接接口123是电性连接至导电触片组14来接收与识别主机端所传送的指令与数据。也就是说,主机端所传送的指令与数据会通过导电触片组 14来传送至控制电路121。

30.具体地,如图3-图4所示,上述存储装置通过设置于封装胶体10第一表面上的导电触片组14,将封装胶体10内的控制芯片12的各个引脚引出,导电触片组14可以通过相对应的连接器来连接主机端,从而使得主机端的数据可以写入到存储装置中或者将存储装置中数据存入主机端中。

31.具体地,如图5所示,本技术实施例中,连接接口123包括vcc5a引脚、 xrxp引脚、xrxn引脚、dm引脚、gnd1引脚、dp引脚、xtxp引脚、xtxn 引脚、gnd2引脚和xfaleo引脚。

32.具体地,封装胶体10的第一表面上还包括导电触片组14和除错接点触片 210,导

电触片组14包括第一数据触片202、第二数据触片203、第三数据触片205、第四数据触片206、第五数据触片208、第六数据触片209、电源信号触片 201、第一地信号触片207和第二地信号触片204。

33.如图5所示,电源信号触片201经由基板11与所述vcc5a引脚电性连接,第一数据触片202经由基板11与所述dm引脚电性连接,第二数据触片203经由基板 11与所述dp引脚电性连接,第二地信号触片204经由基板11与所述gnd2引脚电性连接,第三数据触片205经由基板11与所述xrxn引脚电性连接,第四数据触片206经由基板11与所述xrxp引脚电性连接,第五数据触片208经由基板11与所述xtxn引脚电性连接,第六数据触片209经由基板11与所述xtxp引脚电性连接,第一地信号触片207经由基板11与所述gnd1引脚电性连接,所述除错接点触片 210经由基板11与所述xfaleo引脚电性连接。

34.进一步,第一数据触片202和第二数据触片203传输的是半双工的差分信号。第一数据触片202、第二数据触片203和第一地信号触片207用于实现usb2.0 协议的数据传输。

35.进一步,第三数据触片205、第四数据触片206、第五数据触片208和第六数据触片209传输的是全双工的差分信号。第三数据触片205、第四数据触片 206、第五数据触片208、第六数据触片209和第二地信号触片204用于实现 usb3.0协议的数据传输。

36.进一步,请返回参阅图3和图4,导电触片组14和除错接点触片210沿着所述封装胶体10的长度方向排列设置,且导电触片组14和除错接点触片210设置在封装胶体10的长度方向的端部。

37.进一步,请返回参阅图3和图4,封装胶体10的第一表面还包括焊接触片组 30,所述焊接触片组包括第一焊接触片302和第二焊接触片304,其用于实现所述存储装置和连接器的连接。

38.进一步,如图6所示,所述连接器包括第一端子组61和第二端子组62,第一端子组61电性连接至导电触片组14,第二端子组62和焊接触片组30焊接。

39.具体地,所述连接器为usb3.0连接器。图6为usb3.0连接器的示意图。图 6中,所述usb3.0连接器中的第一端子组61,其包括数量为9个的端子;用于和导电触片组14中的第一数据触片202、第二数据触片203、第三数据触片205、第四数据触片206、第五数据触片208、第六数据触片209、电源信号触片201、第一地信号触片207和第二地信号触片204焊接,实现焊接有usb3.0连接器的存储装置和相对应的usb接口的主机端进行数据传输。第二端子组62,其用以和焊接触片组30焊接,实现所述存储装置和连接器的连接。

40.进一步,封装胶体10的长度为24.8mm,宽度为11.3mm,厚度为1.4mm。

41.进一步,封装胶体10的长度为15mm,宽度为11.3mm,厚度为1.4mm。

42.具体地,上述封装胶体10的尺寸可被理解为存储装置的尺寸。封装胶体10 的尺寸为24.8mm

×

11.3mm

×

1.4mm(长

×

宽

×

厚)为长胶体的udp,封装胶体10的尺寸为15mm

×

11.3mm

×

1.4mm(长

×

宽

×

厚)为短胶体的udp。

43.进一步,所述连接器通过焊接触片组30和存储装置焊接后,得到一个焊接有usb3.0连接器的存储装置。如7所示,图7为焊接着usb3.0连接器的存储装置示意图,所述存储装置具体地为长胶体的udp。

44.本技术实施例中,除错接点触片210和控制芯片12的使能信号引脚电连接,示例性的,如xfale0引脚,xfaleo引脚和除错接点触片210电性连接。所述 xfale0引脚在控制芯片

12的引脚定义中具体地为flash address latchenable,其高电平有效,控制地址数据写入地址寄存器中;在需要对存储装置进行除错操作时,通过利用除错接点触片210短路到接地使其电压拉低,进入 boot code状态,然后通过debug软件在底层底下进行强制读取存储芯片13;如果没有出现存储芯片13颗粒损坏或者其他硬件问题,是可以正确读到存储芯片13的,通过读到存储芯片13,进而可以进行除错操作。

45.本技术实施例中,在存储装置的第一表面上设置除错接点,将除错接点连接于控制芯片的使能信号引脚上,将除错接点裸露在外,存储装置正常使用时,通过连接器将所述除错接点触片遮盖住,防止其氧化短路;在需要对存储装置进行除错操作时,只需要将连接器从存储装置中拆下,连接到裸露在外的除错接点,从而可以接入到存储装置的控制芯片中,强制存储装置必须识别控制芯片,这个时候不和存储芯片通讯,进而实现对存储装置的除错操作,此举使得对存储装置的除错操作非常简单方便。

46.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应该以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1