存储器装置及其假信号预防方法与流程

1.本公开涉及一种存储器装置及其假信号预防方法。

背景技术:

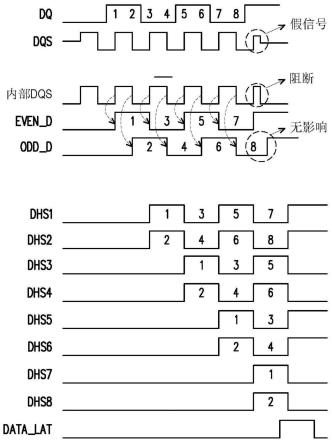

2.目前双倍数据速率(double data rate;ddr)同步动态随机存取存储器(synchronous dynamic random access memory;sdram)装置使用数据选通信号(data strobe signal;dqs)进行数据选通。dqs通过特定突发长度(burst length;bl)和特定预/后输入时序锁存到dram。通过使用dqs选通数据,可减少由于系统时钟与存储器装置之间的位置差异而在数据与系统时钟之间发生的偏差。然而,随着系统的时钟频率增加,时序预算变得越来越紧张,偶尔会在实际应用中发生写入后同步(postamble)故障的情况。

3.图1为常规的ddr sdram的时序图。参考图1,在常规的ddr sdram中,当输入写入命令时,ddr sdram接收数据信号dq连同通常称为dqs的数据选通信号。dqs用作时钟信号以自数据信号dq捕获对应输入数据。将dqs放大以产生内部dqs,且产生具有与内部dqs上升沿同步的脉冲的数据写入信号even_d,而产生具有与内部dqs下降沿同步的脉冲的数据写入信号odd_d。数据写入信号even_d和数据写入信号odd_d分别用于自数据信号dq捕获输入数据。如图1所示出,当dqs的上一脉冲中出现假信号时,内部dqs的下降沿被错误地识别,且因此根据内部dqs的上一下降沿所产生的数据写入信号odd_d的宽度变小。因此,根据数据写入信号odd_d捕获较小有效数据。参考下部部分中示出的数据dhs1到数据dhs8,对准数据dhs1和对准数据dhs2与数据写入信号even_d和数据写入信号odd_d的上升沿同步。由于假信号,对准数据dhs2的值提早改变,且因此捕获到不正确的数据。

4.因此,需要提供一种能够防止写入后发生同步故障的装置。

技术实现要素:

5.鉴于以上内容,本公开提供一种存储器装置及其假信号预防方法,其能够防止后同步时序上出现不需要的假信号。

6.本公开提供一种存储器装置,其包含数据选通信号输入电路、传输信号产生电路、数据对准电路和阻断电路。数据选通信号输入电路配置成输入数据选通信号。传输信号产生电路配置成回应于传输命令而产生具有与数据选通信号的上升沿或下降沿同步的脉冲的传输信号。数据对准电路配置成回应于所产生的传输信号而对准待传输的数据信号。阻断电路配置成根据在每次数据传输中计数的突发数目在数据选通信号的后同步时序上阻断数据选通信号的输入。

7.阻断电路包括突发计数器电路,其配置成对数据传输开始时对突发数目进行计数,且回应所计数的突发数目超过存储器装置的突发长度而输出阻断信号用于阻断数据选通信号的输入。

8.突发计数器电路包括第一反相器、异步计数器、第一逻辑电路和第二逻辑电路。第一反相器配置成使数据选通信号反相且输出反相数据选通信号。异步计数器包含第一触发

器和第二触发器。第一触发器具有第一数据端、第一时钟端和第一异步输出端,其中第一数据端配置成接收参考信号,且第一时钟端配置成接收反相数据选通信号。第二触发器具有第二数据端、第二时钟端和第二异步输出端,其中第二数据端连接到第二异步输出端,且第二时钟端配置成接收第一异步输出端的输出信号和参考信号。第一逻辑电路配置成回应参考信号和第二异步输出端被启用的输出信号而输出启用信号。第二逻辑电路配置成回应第一逻辑电路的输出信号和被启用的反相数据选通信号而输出阻断信号。

9.突发计数器电路进一步包括开关,其配置成回应于重置信号而提供参考信号到第一输入端,其中输入重置信号到第一触发器和第二触发器的重置端以重置锁存在第一触发器和第二触发器中的数据。

10.第一逻辑电路和第二逻辑电路中的每一个包括串联连接的与非门(nand gate)和反相器。

11.突发长度包括四、八和十六中的一个。

12.传输信号产生电路包括产生具有与数据选通信号的上升沿同步的脉冲的第一传输信号和产生具有与数据选通信号的下降沿同步的脉冲的第二传输信号。

13.数据对准电路包括回应于第一传输信号和第二传输信号而同步对准待传输的数据信号。

14.存储器装置进一步包括放大器,其配置成放大数据选通信号。

15.本公开提供一种存储器装置的假信号预防方法。在假信号预防方法中,数据选通信号为第一输入。回应于传输命令而产生具有与数据选通信号的上升沿或下降沿同步的脉冲的传输信号。回应于所产生的传输信号而对准待传输的数据信号。根据在每次数据传输中计数的突发数目在数据选通信号的后同步时序上阻断数据选通信号的输入。

16.后同步时序为从对应于数据传输的数据选通信号的上一下降沿到数据选通信号的下一上升沿的时序。

17.根据在每次数据传输中计数的突发数目在数据选通信号的后同步时序上阻断数据选通信号的输入的步骤包括对从数据传输的开始计数的突发数目进行计数,且回应所计数的突发数目超过存储器装置的突发长度而输出阻断信号以阻断数据选通信号的输入。

18.回应于传输命令而产生具有与数据选通信号的上升沿或下降沿同步的脉冲的传输信号的步骤包括产生具有与数据选通信号的上升沿同步的脉冲的第一传输信号,且产生具有与数据选通信号的下降沿同步的脉冲的第二传输信号。

19.回应于所产生的传输信号而对准待传输的数据信号的步骤包括回应于第一传输信号和第二传输信号而同步对准待传输的数据信号。

附图说明

20.图1为常规的ddr sdram的时序图;

21.图2为根据本公开的实施例的存储器装置的框图;

22.图3为示出根据本公开的实施例的存储器装置的假信号预防方法的流程图;

23.图4为根据本公开的实施例的存储器装置的电路图;

24.图5为根据本公开的实施例的突发计数器电路的电路图;

25.图6到图7为根据本公开的实施例的存储器装置的时序图。

26.附图标号说明

27.20、40:存储器装置;

28.22:数据选通信号输入电路;

29.24:传输信号产生电路;

30.26:数据对准电路;

31.28:阻断电路;

32.50:突发计数器电路;

33.52:异步计数器;

34.54:逻辑电路;

35.56:逻辑电路;

36.a:放大器;

37.blk:阻断信号;

38.d、d':数据端;

39.data_lat:阻断信号;

40.dhs3、dhs4、dhs5、dhs6、dhs7、dhs8:数据;

41.dhs1、dhs2:对准数据;

42.dq:数据信号;

43.dqs:数据选通信号;

44.反相数据选通信号;

45.dqsb:反数据选通信号;

46.even_d、odd_d:数据写入信号;

47.ff、ff1、ff2:触发器;

48.inv1、inv2、inv3:反相器;

49.m1:开关;

50.nd2、nd3:与非门;

51.q、时钟端和异步输出端;

52.q0、q1、q2、q3:模式信号;

53.reset:重置信号;

54.s302、s304、s306、s308:步骤;

55.vdd:参考信号。

具体实施方式

56.参考图2,本实施例的存储器装置20为例如使用数据选通信号(dqs)进行数据选通的双倍数据速率(ddr)同步动态随机存取存储器(sdram)或低功率ddr(low power ddr;lpddr)sdram。存储器装置20包含数据选通信号输入电路22、传输信号产生电路24、数据对准电路26和阻断电路28。

57.在一些实施例中,存储器装置20可进一步包含用于接收由处理器或控制器提供的各种信号的命令接口,以促进待写入或从存储器装置20读取的数据的传输和接收。所接收

到的信号包含来自外部装置的一个或多个时钟信号。在ddr存储器中,使用包含正时钟信号和反时钟信号的时钟信号差分对,且时钟输入电路可以根据所接收到的正时钟信号和反时钟信号产生内部时钟信号,且将内部时钟信号供应到内部时钟产生器(例如,延迟锁定回路(delay locked loop;dll)电路)以用于产生相控内部时钟信号。将相控内部时钟信号供应到i/o接口且作用于确定数据的输出时序的时序信号。

58.为促进存储器装置内的数据速率,在例如ddr存储器的存储器装置中使用通常称为dqs的数据选通信号。dqs由发送待写入的数据的外部处理器或控制器,或由读取数据的存储器装置20驱动,且用作时钟信号以捕获对应的输入数据。如同正时钟信号和反时钟信号,可提供dqs作为数据选通信号的差分对,从而在读取操作和写入操作期间提供差分对命令。

59.参考图3,假信号预防方法适用于存储器装置20,且下文将参考存储器装置20的各种组件描述本实施例的假信号预防方法的详细步骤。

60.首先,在步骤s302中,数据选通信号输入电路22配置成输入数据选通信号。

61.参考图4,在存储器装置40中,从外部装置(例如,处理器)接收的数据选通信号dqs可伴有与数据选通信号dqs互补的反数据选通信号dqsb。这些信号可传输到放大器a以产生内部dqs和互补内部dqsf(假数据选通信号)。放大器a将数据选通信号dqs的功率从外部电平改变为适合于在存储器装置40中使用的电平。

62.内部dqs用于在正确周期上使用触发器ff捕获数据信号dq以成功地开始写入突发且使用所捕获的在dqs域中的写入数据dhs来捕获传入的写入数据。数据选通信号dqs和产生数据信号dq的外部时钟信号之间可具有未知的相位关系。数据选通信号dqs的相位关系将相对于外部时钟进行校准以将数据选通信号dqs置于正确地捕获数据信号dq的位置。在一些实施例中,触发器ff可在内部dqs的下降沿处捕获数据信号dq。替代地,在一些实施例中,触发器ff可在内部dqs的上升沿处捕获数据信号dq。

63.在步骤s304中,传输信号产生电路24配置成回应于传输命令而产生具有与数据选通信号的上升沿或下降沿同步的脉冲的传输信号。传输信号产生电路24可产生具有与数据选通信号的上升沿同步的脉冲的第一传输信号,且产生具有与数据选通信号的下降沿同步的脉冲的第二传输信号。

64.在步骤s306中,数据对准电路26配置成回应于所产生的传输信号而对准待传输的数据信号。数据对准电路26可回应于第一传输信号和第二传输信号而同步对准待传输的数据信号。

65.在步骤s308中,阻断电路28配置成根据在每次数据传输中计数的突发数目在数据选通信号的后同步时序上阻断数据选通信号的输入。后同步时序为例如从对应于数据传输的数据选通信号的上一下降沿到数据选通信号的下一上升沿的时序。

66.在一些实施例中,阻断电路28由突发计数器电路实施,其配置成对从数据传输的开始的突发数目进行计数,且回应于突发数目超过存储器装置的突发长度而输出阻断信号用于阻断数据选通信号的输入。突发长度可为根据存储器装置20的类型确定的四、八或十六。

67.参考图5,本实施例的突发计数器电路50包含反相器inv1、异步计数器52、逻辑电路54和逻辑电路56。反相器inv1配置成使数据选通信号dqs反相且输出反相数据选通信号

异步计数器52包含触发器ff1和触发器ff2。在一些实施例中,触发器ff1和触发器ff2为d触发器,其在本文中不受限制。触发器ff1具有数据端d、时钟端和异步输出端q,其中数据端d配置成接收参考信号vdd,且时钟端配置成接收反相数据选通信号触发器ff2具有数据端d'、时钟端和异步输出端其中数据端d'连接到异步输出端且时钟端配置成接收异步输出端q的输出信号和参考信号vdd。逻辑电路54包含与非门nd2和反相器inv2,且配置成回应于参考信号vdd和异步输出端的输出信号被启用而输出启用信号。逻辑电路56包含与非门nd3和反相器inv3,且配置成回应于逻辑电路54的输出信号和反相数据选通信号被启用而输出阻断信号blk。另外,开关m1配置成回应于重置信号reset而将参考信号vdd提供到输入端d,其中重置信号reset被输入到触发器ff1和触发器ff2的重置端以用于重置锁存在触发器ff1和触发器ff2中的数据。

68.参考图6,本实施例示出图5中的突发计数器电路50的数据选通信号dqs与模式信号q0到模式信号q3之间的关系。突发计数器电路50的模式信号q0到模式信号q3对应于对数据选通信号dqs的上升沿(表示为数目“1”)计数的不同突发数目。当所计数的突发数目达到预定值(表示为数目“8”)时,输出模式信号q3且用于在数据选通信号dqs的后同步时序(即,dqs的上一下降沿之后的时序)上阻断数据选通信号dqs的输入。通过使用突发计数器电路50的模式信号q3作为阻断信号,可防止可能出现在数据选通信号dqs的后同步时序上的假信号。与内部延迟阻断方法相比,pvt(过程、电压、温度)变化影响可被最小化,且可达成具有高频率的数据选通信号dqs的快速反应。应注意,对于不同类型的存储器装置,采用的计数器可不同。举例来说,对于ddr3 sdram或ddr4 sdram,采用8位计数器,而对于lpddr4 sdram,替代地采用16位计数器。

69.参考图7,在本实施例中,当输入写入命令时,存储器装置接收数据信号dq连同通常称为dqs的数据选通信号。dqs用作时钟信号以自数据信号dq捕获对应输入数据。将dqs放大以产生内部dqs,且产生具有与内部dqs的上升沿同步的脉冲的数据写入信号even_d,同时产生具有与内部dqs的下降沿同步的脉冲的数据写入信号odd_d。数据写入信号even_d和数据写入信号odd_d分别用于自数据信号dq捕获输入数据。

70.如图7中所示出,当在数据选通信号dqs的上一脉冲中出现假信号时,数据选通信号dqs的下降沿可能会被错误地识别。然而,根据以上实施例产生的阻断信号data_lat,可阻挡由内部dqs中的假信号引起的脉冲,因此,根据内部dqs的上升沿和下降沿产生的数据写入信号even_d和数据写入信号odd_d被校正且用于从数据信号dq捕获输入数据。参考下部中示出的数据dhs1到数据dhs8,对准数据dhs1和对准数据dhs2与数据写入信号even_d和数据写入信号odd_d的上升沿正确地同步。

71.总而言之,根据本公开的实施例,提出一种存储器装置及其假信号预防方法,以借助计数器进行编程突发计数。基于突发数目的计数,可防止后同步时序上数据选通信号中扩展假信号的输入,且可实现高频率数据选通信号的快速反应。

72.尽管已通过以上实施例公开本公开,但是所述实施例并不意图限制本公开。对于本领域的技术人员将显而易见的是,在不脱离本公开的范围或精神的情况下,可以对本公开的结构进行各种修改和变化。因此,本公开的保护范围属于所附权利要求。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1