一种基于铁电晶体管阵列的编程和擦除方法与流程

1.本发明属于芯片存储器存储技术领域,是一种基于铁电晶体管阵列的编程和擦除方法。

背景技术:

2.基于冯

·

诺依曼体系,当前计算系统发展出一套多级存储架构体系来平衡读写速度和存储容量间的矛盾。随着集成电路工艺制造水平的提升,器件尺寸减小,可存储的电荷量也随之减少。以电荷存储为存储机制的传统存储技术面临严重的可靠性问题。同时,大数据,人工智能,万物互联等新兴领域的兴起和发展,需要高密度大容量兼顾读写速度的存储技术支撑。

3.铁电存储器是通过铁电材料的极化翻转实现0/1存储的存储技术,氧化铪基(hfo2)的铁电存储晶体管(ferroelectric field effect transistor,fefet)是铁电存储技术主要实现形式之一。相比传统的存储技术,fefet的读写速度快,操作电压低,微缩性好,能与主流硅工艺良好兼容,实现高密度存储。

4.铁电晶体管是构成铁电晶体管阵列的基础单元。铁电晶体管由一个栅极、一个源端、一个漏端和一个衬底构成。铁电晶体管的栅极由金属层、铁电层ferroelectric和绝缘层dielectric组成。在栅极上施加正电压或负电压,会导致铁电层极化正向翻转或负向翻转。撤去电压,极化状态保持不变。极化会在沟道吸引电性相反的电荷,改变晶体管的阈值电压。当施加在铁电材料上的电压超过矫顽场(ec)时,铁电材料才能实现极化翻转。

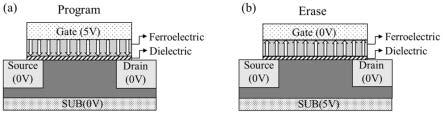

5.对于n沟道的fefet来说,当对铁电晶体管阵列存储信息0时,传统编程模式下,栅极施加足够大的正电压,源端和漏端电位为0。此时铁电极化正向翻转,铁电晶体管的阈值电压变小。相反地存储信息1时,栅极、源端和漏端电位均接零电位,底电极施加足够大的正电压,铁电极化负向翻转,铁电晶体管的阈值电压变大。

6.相反地对于p沟道的fefet来说,当对铁电晶体管阵列存储信息0时,栅极施加足够大的正电压,源端和漏端电压设为0v。此时铁电极化正向翻转,铁电晶体管的阈值电压变小。相反地存储信息1时,栅极施加足够大的负电压,源端和漏端电位为0,铁电极化负向翻转,铁电晶体管的阈值电压变大。

7.如图1是衬底floating情况下,编程program和擦除erase时铁电薄膜极化翻转的程度。当对fefet进行数据擦除时,由于衬底处于悬浮(floating)状态,在擦除过程中沟道的有效电场远小于极化翻转所需的矫顽场,只有源端(source)、漏端(drain)与栅极(gate)的交叠部分的铁电层,能实现有效地极化翻转,剩余沟道对应部分的铁电材料均不能实现有效翻转,限制了铁电晶体fefet的有效存储窗口(memory window,mw)。

8.改善该问题的有效方法之一是,在源漏端旁引出衬底的电极sub,如图2所示。该方法能有效改善铁电晶体管因衬底floating造成的窗口有限的问题,同时也引入了其他的问题。在源漏旁增加衬底电极,不仅增加了晶体管的有效面积,也增加了制造过程中的工艺复杂程度。

技术实现要素:

9.本发明目的在于针对现有技术的不足,提供一种基于铁电晶体管阵列的编程和擦除方法。

10.本发明的目的是通过以下技术方案来实现的:一种基于铁电晶体管阵列的编程和擦除方法,在晶体管的衬底底部引出电极sub,通过控制底电极电位,对铁电晶体管进行信息的存储和擦除;

11.编程时,bl、sl和衬底电压设置为0v,wl施加大的正电压,此时栅极和沟道间的电压差可使极化正向翻转;晶体管的阈值电压负向偏移,实现数据0的存储;

12.擦除时,wl、bl和sl电压均为0v,衬底电极施加正的高电压,铁电极化反方向翻转;由于共用底电极,所有晶体管的阈值电压正向漂移,实现数据1的存储。

13.进一步地,当对铁电晶体管存储信息0时,栅极施加足够大的正电压,源端、漏端和底电极电压设为0v;此时铁电极化正向翻转,铁电晶体管的阈值电压变小;相反地存储信息1时,栅极、源端和漏端电位接0电位;底电极施加足够大的正电压,铁电极化负向翻转,铁电晶体管的阈值电压变大;由于铁电晶体管阵列共用底电极,可实现阵列整体信息地擦除。

14.进一步地,编程时对于选中器件的外加电压方式,包括:位线bl、源线sl和衬底电压v

bulk

设置为0v,字线wl施加大于矫顽场ec的正电压v

p

,此时栅极和沟道间的电压差可使极化正向翻转;晶体管的阈值电压负向偏移,实现数据0的存储。

15.进一步地,编程时对于未选中器件的外加电压方式,包括:与选中器件共用字线wl的器件,wl施加电压为v

p

,bl和sl施加电压为1/2v

p

;与选中器件共用位线bl和源线sl的器件,bl、sl和wl电位均为0;剩余未选中器件的bl和sl的电位为1/2v

p

,wl电位为0。

16.进一步地,由于未选中器件bl、sl和wl两两之间的电位差均小于等于1/2v

p

,铁电极化难以翻转,防止误写。

17.进一步地,擦除时对选中器件和未选中器件的外加电压模式相同,包括:wl、bl和sl电压均为0v,衬底电极v

bulk

施加大于矫顽场ec的正电压ve,使铁电极化反方向翻转;由于共用底电极,所有晶体管的阈值电压正向漂移,实现数据1的存储。

18.本发明的有益效果是:本发明方法可使铁电极化有效翻转,增大晶体管的存储窗口。相比单个器件依次擦除,片擦除能够在不增加晶体管面积的前提下高效地实现大面积擦除。本发明不仅对体衬底的铁电晶体管阵列有效,也可应用于绝缘体上硅的铁电晶体管阵列。

附图说明

19.图1是衬底floating情况下铁电层的极化翻转示意图;其中,(a)为体硅上fefet编程极化翻转;(b)为体硅上fefet擦除极化翻转;

20.图2是衬底顶电极控制的铁电层的极化翻转示意图;其中,(a)为体硅上fefet编程极化翻转;(b)为体硅上fefet擦除极化翻转;

21.图3是衬底底电极控制的铁电层的极化翻转示意图;其中,(a)为体硅上fefet编程极化翻转;(b)为体硅上fefet擦除极化翻转;

22.图4是绝缘体上硅铁电晶体管阵列在底电极控制下极化翻转情况示意图;其中,(a)为编程时铁电层的极化翻转情况,(b)为擦除时铁电层的极化翻转情况;

23.图5是n沟道fefet阵列编程方式示意图;其中,(a)为衬底floating;(b)为衬底顶部引出衬底电位;(c)为fefet器件底部共用衬底电极;

24.图6是n沟道fefet阵列擦除方式示意图;其中,(a)为衬底floating;(b)为衬底顶部引出衬底电位;(c)为fefet器件底部共用衬底电极。

具体实施方式

25.下面结合附图对本发明作进一步描述。

26.本发明一种基于铁电晶体管阵列的编程和擦除方法,在晶体管的衬底底部引出电极sub,通过控制底电极电位,对铁电晶体管进行信息的存储和擦除。

27.以n型铁电晶体管为例,当对铁电晶体管存储信息0时,栅极施加足够大的正电压,源端、漏端和底电极电压设为0v。此时铁电极化正向翻转,铁电晶体管的阈值电压变小。相反地存储信息1时,栅极、源端和漏端电位接0电位。底电极施加足够大的正电压,铁电极化负向翻转,铁电晶体管的阈值电压变大。由于铁电晶体管阵列共用底电极,可实现阵列整体信息地擦除。

28.图3是从衬底底部引出底电极,体衬底铁电晶体管的编程和擦除方式下的铁电极化翻转程度。图4是绝缘体上硅铁电晶体管在本发明的编程和擦除方式下的铁电极化翻转程度。本发明的编程和擦除方法,对体结构的fefet晶体管阵列和绝缘体上硅的fefet晶体管阵列均适用。

29.相比从衬底顶部将衬底电位通过电极引出,本发明方法可减小晶体管的面积,同时增大存储窗口。此外,通过底电极擦除信息时,可对共用底电极的所有铁电晶体管进行信息擦除,称为片擦除。相比从顶部引出电极只能对整列器件进行擦除,本发明方法擦除效率高。

30.如图5是fefet阵列编程时,以上三种编程program方式的外加电压方式,如下:

31.图5(a)是衬底v

bulk

=floating情况下对fefet阵列进行编程时,各端的加压方式。对于选中器件(selected device),位线bl和源线sl电压设置为0,对字线wl施加大于矫玩场ec的正电压v

p

,此时只有源端/漏端和栅极交叠区域的铁电材料实现极化反转。

32.图5(b)是在选中器件表面增加新的连接端,通过偏置连接端的电位为0,使衬底电位v

bulk

也固定为0。此时对位线bl和源线sl施加0电位,字线wl同样施加大于矫玩场ec的正电压v

p

,可使栅极长度上的铁电材料的极化翻转。该种编程方法能实现铁电材料的有效翻转。劣势在于当前存储阵列的密度较高,新增加的连接端会导致器件面积的增大,降低器件密度。

33.图5(c)是本发明的编程方法,在晶体管的衬底底部引出电极sub。本发明方法在对铁电晶体管阵列编程时,选中器件的位线bl、源线sl和衬底电压v

bulk

设置为0v,字线wl施加大于矫顽场ec的正电压v

p

,此时栅极和沟道间的电压差可使极化正向翻转。晶体管的阈值电压负向偏移,实现数据0的存储,同时没有多余面积的增加。

34.对于未选中器件,除衬底电位v

bulk

不同,三种编程方式的bl、sl和wl的加压方式都一致,包括:与选中器件共用字线wl的器件,wl施加电压也为v

p

,但bl和sl施加电压为1/2v

p

,以防止铁电极化翻转。与选中器件共用位线bl和源线sl的器件,bl、sl和wl电位均为0。剩余未选中器件的bl和sl的电位为1/2v

p

,wl电位为0。由于未选中器件bl、sl和wl两两之间的电

位差均小于等于1/2v

p

,铁电极化难以翻转,可防止器件的误写。

35.与编程时所加电压的方法类似,图6是fefet阵列擦除时,以上三种擦除erase方式的三端外加电压模式,如下:

36.对于选中器件:图6(a)在对fefet阵列进行擦除时,bl和sl施加电压为0,wl施加数值大于ec的负电压ve,此时衬底floating。图6(b)在选中器件表面增加新的连接端,bl和sl同样施加电压为0,新增加的连接端电位也为0,wl施加数值大于ec的负电压ve。与编程时不同,片擦除方式对整个阵列的器件进行擦除。如图6(c)所示,此时wl、bl和sl电压均为0v,衬底电极v

bulk

施加大于矫顽场ec的正电压ve,使铁电极化反方向翻转。由于共用底电极,所有晶体管的阈值电压正向漂移,实现数据1的存储。

37.对于未选中器件,除衬底端为floating或接0电位,图6(a)、图6(b)两种擦除方式对源端、漏端和栅极的加压一致,包括:与选中器件共用wl的未选中器件,wl电位为ve,bl和sl的电位为1/2ve。与选中器件共用bl和sl的器件,bl、sl和wl电位均为0。其余未选中器件的sl和bl的电位为1/2ve,wl为0。上述两种擦除方法中,各端两两电位差保持小于等于1/2ve,铁电极化不翻转,未选中器件在擦除操作中保持初始状态。而本发明的擦除方法对选中器件和未选中器件均作相同处理,bl、sl和wl的电位为0,衬底电位v

bulk

为ve。本发明方法的擦除效率更高,且对体衬底和soi衬底均有用。

38.本发明并不限于上述实施方式,采用与本发明上述实施方式相同或近似的方式,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,均在本发明专利的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1