非易失性存储器及其擦除操作方法、非易失性存储系统与流程

1.本技术涉及半导体技术领域,更具体地,涉及一种非易失性存储器、非易失性存储器的擦除操作方法、非易失性存储系统、适用于神经网络算法的非易失性存储器以及适用于神经网络算法的非易失性存储系统。

背景技术:

2.非易失性存储器能够在断电后仍保留存储于其中的数据,并且广泛应用于计算机、蜂窝电话、智能手机、个人数字助理及其它电子设备系统。一种类型的非易失性存储器可包括由例如多个存储单元串联构成的nand串,多个nand串的一端与共同的源极线连接以构成存储块(block),从而使得这些nand串所包括的多个存储单元以存储块为单位在一次擦除操作过程中被擦除,而在一次擦除操作过程中选择性地使部分存储单元被擦除较为困难。

3.另一方面,人工神经网络(简称为神经网络)的快速发展使得人工智能方面的研究引发了新的浪潮。当利用非易失性存储器执行神经网络算法时,随着神经网络的参数规模和运算量急速提升,神经网络的硬件平台面临着存储利用率与计算参数参与量不匹配所带来的问题。

技术实现要素:

4.本技术一方面提供了一种非易失性存储器的擦除操作方法,其中,该非易失性存储器包括存储块,存储块包括多个存储串,多个存储串中的至少一个第一存储串连接于第一位线和源极线之间,并包括靠近第一位线的漏极选择晶体管以及漏极选择晶体管与源极线之间的多个存储单元,漏极选择晶体管和存储单元分别与漏极选择线和字线连接,该方法包括:在预擦除阶段内的t0时刻之后,使第一位线上的电压以预设斜率上升,并在擦除阶段保持所达到的目标擦除电压;在预擦除阶段内的t2时刻之前,向第一漏极选择线施加接地电压,并在t2时刻之后保持第一漏极选择线为浮置状态;以及在擦除阶段,向待擦除的存储单元连接的至少一个第一字线施加偏置电压,其中,目标擦除电压与偏置电压的差值大于擦除阈值。

5.在一些实施方式中,第一存储串还包括位于多个存储单元与源极线之间的源极选择晶体管,源极选择晶体管与源极选择线连接,该方法还包括:在预擦除阶段内的t0时刻之后,使源极选择线上的电压以预设斜率上升,并在擦除阶段保持所达到的目标擦除电压;或者在预擦除阶段和擦除阶段,保持源极选择线为浮置状态。

6.在一些实施方式中,该方法还包括:在预擦除阶段内的t3时刻之前,向第一字线以外的第二字线施加接地电压,并在t3时刻之后保持第二字线为浮置状态。

7.在一些实施方式中,存储块还包括第一漏极选择线以外的第二漏极选择线,该方法还包括:在预擦除阶段内的t1时刻之前,向第二漏极选择线施加接地电压,并在t1时刻之后保持第二漏极选择线为浮置状态,其中,t1时刻早于t2时刻。

8.在一些实施方式中,存储块还包括第一位线以外的第二位线,该方法还包括:在预擦除阶段内的t2时刻之后,使第二位线上的电压以预设斜率上升,并在擦除阶段保持所达到的目标非擦除电压。

9.在一些实施方式中,目标非擦除电压小于目标擦除电压。

10.在一些实施方式中,第一存储串还包括位于漏极选择晶体管与多个存储单元之间的漏极虚设存储单元,漏极虚设存储单元与漏极虚设字线连接,该方法还包括:在预擦除阶段内的t3时刻之前,向漏极虚设字线施加接地电压,并在t3时刻之后保持漏极虚设字线为浮置状态。

11.在一些实施方式中,第一存储串还包括位于源极选择晶体管与多个存储单元之间的源极虚设存储单元,源极虚设存储单元与源极虚设字线连接,该方法还包括:在预擦除阶段内的t1时刻之前,向源极虚设字线施加接地电压,并在t1时刻之后保持源极虚设字线为浮置状态,其中,t1时刻早于t2时刻。

12.在一些实施方式中,偏置电压为接地电压。

13.本技术另一方面提供了一种非易失性存储器,该非易失性存储器包括:存储块,存储块包括多个存储串,多个存储串中的至少一个第一存储串连接于第一位线和源极线之间,并包括靠近第一位线的漏极选择晶体管以及漏极选择晶体管与源极线之间的多个存储单元,漏极选择晶体管和存储单元分别与漏极选择线和字线连接;以及外围电路被配置为:在预擦除阶段内的t0时刻之后,使第一位线上的电压以预设斜率上升,并在擦除阶段保持所达到的目标擦除电压;在预擦除阶段内的t2时刻之前,向第一漏极选择线施加接地电压,并在t2时刻之后保持第一漏极选择线为浮置状态;以及在擦除阶段,向待擦除的存储单元连接的至少一个第一字线施加偏置电压,其中,目标擦除电压与偏置电压的差值大于擦除阈值。

14.在一些实施方式中,第一存储串还包括位于多个存储单元与源极线之间的源极选择晶体管,源极选择晶体管与源极选择线连接,外围电路还被配置为:在预擦除阶段内的t0时刻之后,使源极选择线上的电压以预设斜率上升,并在擦除阶段保持所达到的目标擦除电压;或者在预擦除阶段和擦除阶段,保持源极选择线为浮置状态。

15.在一些实施方式中,外围电路还被配置为:在预擦除阶段内的t3时刻之前,向第一字线以外的第二字线施加接地电压,并在t3时刻之后保持第二字线为浮置状态。

16.在一些实施方式中,存储块还包括第一漏极选择线以外的第二漏极选择线外围电路还被配置为:在预擦除阶段内的t1时刻之前,向第二漏极选择线施加接地电压,并在t1时刻之后保持第二漏极选择线为浮置状态,其中,t1时刻早于t2时刻。

17.在一些实施方式中,存储块还包括第一位线以外的第二位线,外围电路还配配置为:在预擦除阶段内的t2时刻之后,使第二位线上的电压以预设斜率上升,并在擦除阶段保持所达到的目标非擦除电压。

18.在一些实施方式中,目标非擦除电压小于目标擦除电压。

19.在一些实施方式中,第一存储串还包括位于漏极选择晶体管与多个存储单元之间的漏极虚设存储单元,漏极虚设存储单元与漏极虚设字线连接,外围电路还被配置为:在预擦除阶段内的t3时刻之前,向漏极虚设字线施加接地电压,并在t3时刻之后保持漏极虚设字线为浮置状态。

20.在一些实施方式中,第一存储串还包括位于源极选择晶体管与多个存储单元之间的源极虚设存储单元,源极虚设存储单元与源极虚设字线连接,外围电路还被配置为:在预擦除阶段内的t1时刻之前,向源极虚设字线施加接地电压,并在t1时刻之后保持源极虚设字线为浮置状态,其中,t1时刻早于t2时刻。

21.在一些实施方式中,偏置电压为接地电压。

22.本技术另一方面还提供了一种非易失性存储系统,该非易失性存储系统包括:如前文中任意实施方式所描述的至少一个非易失性存储器;以及控制器,连接至少一个非易失性存储器,被配置为控制非易失性存储器中的外围电路。

23.本技术另一方面又提供了一种适用于神经网络算法的非易失性存储器,其中,非易失性存储器包括位于不同存储串中的多个存储单元,多个存储单元与同一字线连接,并对应于神经网络中的一个神经元,多个存储单元所在多个存储串分别连接至多条位线;以及外围电路,被配置为:向多条位线施加多个位线电压,位线电压作为神经网络中的神经元的一个输入;向与多个存储单元连接的字线施加读取电压;基于多个存储单元中的多个电导值,确定神经元的输出,电导值作为神经元的输入对应的权重;以及对多个存储单元中的至少一个存储单元执行编程操作,或者根据前文中任意实施方式所描述的擦除操作方法执行擦除操作,以调整电导值,其中,第一存储串和第一字线的数量为一个。

24.本技术另一方面再提供了一种适用于神经网络算法的非易失性存储系统,该非易失性存储系统包括:如前文中任意实施方式所描述的至少一个非易失性存储器;以及控制器,连接至少一个非易失性存储器,被配置为控制非易失性存储器中的外围电路。

25.根据本技术的至少一个实施方式,一方面,本技术提供的一种非易失性存储器、非易失性存储器的擦除操作方法以及非易失性存储系统,利用gidl电流产生进入存储块中的一些选择的存储串中的空穴,从而使得这些选择的存储串的沟道层的电势升高,同时利用一些选择的字线与选择的存储串的沟道层的电势差,使得选择的存储串中的至少一个选择的存储单元被擦除,有利于提高非易性存储器的擦除操作灵活性。同时,还可通过选择性地擦除部分存储单元,增加选择性地增加这部分存储单元的读取窗口,以提高存储单元的读取准确性。

26.另一方面,本技术提供的一种适用于神经网络算法的非易失性存储器以及适用于神经网络算法的非易失性存储系统,利用非易失性存储器中的单个存储单元的电导值作为神经网络中神经元的一个输入所对应的权重,能够提高利用非易性存储器来存储神经网络的参数的存储利用率,有利于发挥非易性存储器高存储密度的优势。同时,无需增设例如减法器来计算电导差值,有利于与现有的外围电路兼容,并且也可避免消耗一部分存储容量来存储这些电导差值,进一步地提高非易性存储器的存储利用率。此外,通过对调整单个存储单元的电导值来调整权重,能够应对当两个存储单元的各自电导值达到上限后,无法继续对权重进行调整的问题,有利于实现更加复杂的深度神经网络。

附图说明

27.通过阅读参照以下附图所作的对非限制性实施例的详细描述,本技术的其它特征、目的和优点将会变得更明显。其中:

28.图1是根据本技术实施方式的连接到主机的非易失性存储系统的功能框图;

29.图2是根据本技术实施方式的非易失性存器的功能框图;

30.图3是根据本技术实施方式的存储单元阵列的等效电路图;

31.图4是根据本技术实施方式的存储串与各个控制线连接的物理结构剖面示意图;

32.图5是根据本技术实施方式的非易失性存器的擦除操作方法的流程图;

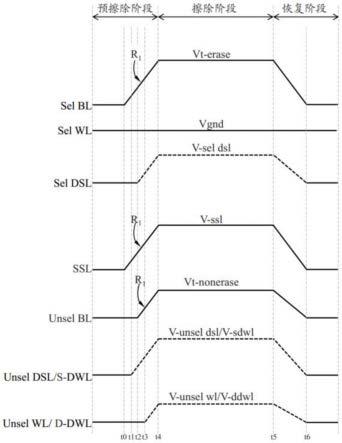

33.图6是根据图5示出的擦除操作方法的各个控制线的电压波形示意图;

34.图7是根据本技术实施方式的三层神经网络结构示意图;

35.图8是根据本技术实施方式的神经网络的训练过程的流程图;

36.图9是根据本技术实施方式的用于执行神经网络的非易失性存储器的操作方法的流程图;

37.图10是根据图3示出的存储单元阵列中的二维存储单元阵列的等效电路图;

38.图11是根据本技术实施方式的为确定神经元的输出向n条字线所施加的电压的波形图;

39.图12是根据本技术另一实施方式的用于执行神经网络的非易失性存储器的操作方法的示意图;以及

40.图13是根据本技术实施方式的存储单元的电导值与执行编程操作和擦除操作的时间的曲线图。

具体实施方式

41.为了更好地理解本技术,将参考附图对本技术的各个方面做出更详细的说明。应理解,这些详细说明只是对本技术的示例性实施方式的描述,而非以任何方式限制本技术的范围。在说明书全文中,相同的附图标号指代相同的元件。表述“和/或”包括相关联的所列项目中的一个或多个的任何和全部组合。

42.应注意,在本说明书中,第一、第二、第三等的表述仅用于将一个特征与另一个特征区域分开来,而不表示对特征的任何限制,尤其不表示任何的先后顺序。因此,在不背离本技术的教导的情况下,本技术中讨论的第一部分也可被称作第二部分,第一沟道结构也可称为第二结构,反之亦然。

43.在附图中,为了便于说明,已稍微调整了部件的厚度、尺寸和形状。附图仅为示例而并非严格按比例绘制。如在本文中使用的,用语“大致”、“大约”以及类似的用语用作表近似的用语,而不用作表程度的用语,并且旨在说明将由本领域普通技术人员认识到的、测量值或计算值中的固有偏差。

44.还应理解的是,诸如“包括”、“包括有”、“具有”、“包含”和/或“包含有”等表述在本说明书中是开放性而非封闭性的表述,其表示存在所陈述的特征、元件和/或部件,但不排除一个或多个其它特征、元件、部件和/或它们的组合的存在。此外,当诸如“...中的至少一个”的表述出现在所列特征的列表之后时,其修饰整列特征,而非仅仅修饰列表中的单独元件。此外,当描述本技术的实施方式时,使用“可”表示“本技术的一个或多个实施方式”。并且,用语“示例性的”旨在指代示例或举例说明。

45.除非另外限定,否则本文中使用的所有措辞(包括工程术语和科技术语)均具有与本技术所属领域普通技术人员的通常理解相同的含义。还应理解的是,除非本技术中有明确的说明,否则在常用词典中定义的词语应被解释为具有与它们在相关技术的上下文中的

含义一致的含义,而不应以理想化或过于形式化的意义解释。

46.需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。另外,除非明确限定或与上下文相矛盾,否则本技术所记载的方法中包含的具体步骤不必限于所记载的顺序,而可以任意顺序执行或并行地执行。下面将参考附图并结合实施例来详细说明本技术。

47.此外,在本技术中当使用“连接”或“联接”时可表示相应部件之间为直接的接触或间接的接触,除非有明确的其它限定或者能够从上下文推导出的除外。

48.图1是根据本技术实施方式的连接到主机20的非易失性存储系统10的功能框图。如图1所示,主机20和存储系统10组成的电子设备可为移动电话、台式计算机、膝上型电脑、平板电脑、车载计算机、游戏控制台、打印机、定位器件、可穿戴电子设备、智能传感器、虚拟现实(virtual reality,vr)设备、增强现实(argument reality,ar)设备或者任何其他适当的电子设备。

49.主机20可包括电子设备的处理器,并被配置为控制存储系统10的整体操作,以及往来于存储系统10发送或接收数据。主机20可为中央处理单元(central processing unit,cpu),或者可为片上系统(system-on-chip,soc),例如,应用处理器(application processor,ap)。

50.存储系统10可存储有主机20访问的数据。根据存储系统10与主机20连接的接口协议,存储系统10可被配置为诸如通用闪存存储(ufs)系统,固态硬盘(ssd),mmc、emmc、rs-mmc和微型mmc形式的多媒体卡,sd、迷你sd和微型sd形式的安全数字卡,个人计算机存储卡国际协会(pcmcia)卡类型的存储系统,外围组件互连(pci)类型的存储系统,高速pci(pci-e)类型的存储系统,紧凑型闪存(cf)卡,智能媒体卡或者记忆棒或者任何其他适当的存储系统。

51.如图1所示,存储系统10可包括用于存储数据的一个或多个非易失性存储器110和用于控制非易失性存储器110的控制器120。

52.控制器120耦合至非易失性存储器110和主机20,并且被配置为控制非易性存储器110的操作、管理存储在非易性存储器110中的数据以及与主机20通信。控制器120可例如包括主机接口121、处理器122、闪存接口123。

53.控制器120中的主机接口121可根据特定通信协议与主机20通信。主机接口210的接口协议可包括通用闪存(ufs)协议、串行高级技术附件(sata)协议、外围组件互连(pci)协议和高速pci(pci-e)协议、通用串行总线(usb)协议、多媒体卡(mmc)协议、并行高级技术附件(pata)协议、小型计算机系统接口(scsi)协议、串列scsi(sas)协议等中的任意一种。

54.控制器120中的处理器122可例如包括一个或多个arm核。处理器122可通过驱动被称为闪存转换层(ftl)的固件,以控制非易失性存储器110的固有操作并且对主机20提供兼容性。此外,处理器220还可通过诸如驱动其它固件实现例如磨损均衡(wear leveling)、垃圾收集(garbage collection)、坏块管理(bad block management)等功能。

55.控制器120中的闪存接口123可例如根据符合onfi或toggle标准的闪存命令,负责管理数据以从非易失性存储器110读取和写入。例如,对于每个非易失性存储器110而言,可通过闪存接口123向其传输命令、地址以及数据。对于多个非易失性存储器110而言,可在传输命令、地址以及数据之前,通过例如选通信号选择特定的非易失性存储器110。

56.每个非易失性存储器110可被称为管芯(die),也可被称为存储颗粒。每个管芯可为闪存通信的最小基本管理单元。示例性地,非易失性存储器110可为nand型存储器。一个非易失性存储器110或者多个非易失性存储器110可集成为一个封装件。例如,4~8个非易失性存储器110可封装在一起。需要说明的是,多个非易失性存储器110封装的数量可根据容量需求进行设计,本技术对具体的数量不做限定。

57.图2是根据本技术实施方式的非易失性存器210的功能框图。其中,非易失性存器210可为图1示出的多个非易失性存器110中的一个示例。如图2所示,非易失存储器210可包括存储单元阵列220和诸如页缓冲器231、行解码器232、列解码器233、电压发生器234、逻辑控制模块235、i/o模块236以及数据总线237等组成的外围电路。应理解的是,本技术中所描述的上述电路模块所执行的操作可由处理电路执行。可选地,处理电路可包括但不限于逻辑电路的硬件或者执行软件的处理器的硬件/软件组合。

58.存储单元阵列220可包括以三维阵列形成布置的多个储存单元。多个存储单元可按照预定的连接方式与多条位线(bl)和多条字线(wl)连接。示例性地,每个存储单元可为能够存储一位数据的单层存储单元(slc)、能够存储两位数据的两层存储单元(mlc)、能够存储三位数据的三层存储单元(tlc)以及能够存储四位数据的四层存储单元(qlc)中的任意一种。例如,同一字线连接的多个slc存储单元对应一个页(page)。

59.页缓冲器(或者称为“感测放大器”)231可被配置为根据来自逻辑控制模块235的控制信号从存储单元阵列220读取数据或者向存储单元阵列220编程(写入)数据。在一些示例中,页缓冲器231可存储将要被编程到存储单元阵列220中一个页的数据。在另一些示例中,页缓冲器231可在读取操作中感测存储在存储单元阵列220的存储单元中的数据的低功率信号,并且将小电压摆幅放大到可识别逻辑电平。

60.行解码器232可被配置为由逻辑控制模块235控制,并选择存储单元阵列220中一个页。例如,行解码器232可被配置为使用由电压发生器234生成的电压通过驱动字线而选择对应的页。

61.列解码器233可被配置为由逻辑控制模块235控制,并通过施加由电压发生器234生成的位线电压而选择对应的位线。

62.电压发生器234可被配置为由逻辑控制模块235控制,并且生成将被提供至存储单元阵列220中的字线电压(例如,充电电压、接地电压、读取电压、编程电压、通过电压、验证电压等)、位线电压(例如,擦除电压、非擦除电压等)和源极线电压等。

63.逻辑控制模块235可耦合至前文描述的每个外围电路模块,并且被配置为控制各个外围电路模块的操作,逻辑控制模块235可控制执行将要在下文中描述的擦除操作方法500(参考图5)和/或神经网络的操作方法900(参考图9)。

64.i/o模块236可耦合至逻辑控制模块235,以将从主机20(参考图1)或者控制器120(参考图1)接收到的控制命令转发至逻辑控制模块235,并且将从逻辑控制模块235接收到的状态信息转发至控制器120(参考图1)。i/o模块236还可经由数据总线237耦合至列解码器233,对往返于存储单元阵列220的数据进行缓冲和转发。

65.图3是根据本技术实施方式的存储单元阵列320的等效电路图。

66.其中,存储单元阵列320可为图2示出的存储单元阵列220中的一部分的示例。例如,图3示出的存储单元阵列320可被称为存储块。

67.如图3所示,存储块可包括多个存储串(例如,str11、strm1、str1p、strmp等)。例如,多个存储串str11~strmp可相对于xy平面以二维阵列形式布置。每个存储串(例如,str11)可沿z方向延伸,并连接于源极线acs与位线(例如,bl1)之间。示例性地,存储串str11可依次包括彼此串联连接的漏极选择晶体管dst

11

、漏极虚设存储单元d-dmc

11

、存储单元mc1

11

~mcn

11

、源极虚设存储单元s-dmc

11

以及源极选择晶体管sst

11

。示例性地,对于每个存储串(例如,str11)来说,漏极虚设存储单元d-dmc

11

和/或源极虚设存储单元s-dmc

11

可省略,或者漏极虚设存储单元d-dmc

11

和/或源极虚设存储单元s-dmc

11

的数量不限于图3示出的一个,二者均可具有其它数量,例如2~5个。此外,需要说明的是,每个存储串(例如,str11)所包括的漏极选择晶体管dst

11

、源极选择晶体管sst

11

以及存储单元mc1

11

~mcn

11

的数量本技术对此也不做具体的限定。

68.各个存储串str11~strmp中位于距离源极线asc(大致地)相同高度多个存储单元(例如,mck

11

、mck

m1

、mck

1p

以及mck

mp

等)的栅极端可连接至相同的字线(例如,wlk),从而使得例如存储块包括多条字线wl1~wln。如前文所述,连接至相同的字线(例如,wlk)的多个存储单元(例如,mck

11

、mck

m1

、mck

1p

以及mck

mp

等)可由该字线(例如,wlk)控制,该字线(例如,wlk)连接的多个存储单元(例如,mck

11

、mck

m1

、mck

1p

以及mck

mp

等)可构成一个页,从而使得例如存储块包括与多条字线wl1~wln对应的多个页。

69.沿x方向排列的多个存储串(例如,str11~strm1)中位于距离源极线acs(大致地)相同高度的多个漏极选择晶体管(例如,dst

11

~dst

m1

)的栅极端可连接至相同的漏极选择线(例如,dsl1),从而使得例如存储块包括沿y方向设置的多个漏极选择线dsl1~dslp。

70.沿y方向排列的多个存储串(例如,str11~str1p)的另一端可连接至相同的位线(例如,bl1)。示例性地,各个存储串(例如,str11~str1p)中位于端部的各个漏极选择晶体管(例如,dst

11

~dst

1p

)的漏极端可连接至位线bl1,从而使得例如存储块包括沿x方向设置的多条位线bl1~blm。

71.在一些示例中,存储块中的各个存储串str11~strmp中位于距离源极线acs(大致地)相同高度的多个源极选择晶体管(例如,sst

11

~sst

mp

)的栅极端可彼此连接,并连接至同一源极选择线ssl,从而使得例如存储块包括一个源极选择线ssl。

72.在一些示例中,存储块中的多个存储串str11~strmp的一端可共同连接至源极线acs。示例性地,各个存储串str11~strmp中位于端部的各个源极选择晶体管(例如,sst

11

~sst

mp

)的源极端可连接至源极线acs。

73.在一些示例中,存储块中的各个存储串str11~strmp中位于距离源极线acs(大致地)相同高度的多个漏极虚设存储单元(例如,d-dmc

11

~d-dmc

mp

)的栅极端可连接至相同的漏极虚设字线(例如,d-dwl)。存储块中的各个存储串str11~strmp中位于距离源极线acs(大致地)相同高度的多个源极虚设存储单元(例如,s-dmc

11

~s-dmc

mp

)的栅极端可连接至相同的源极虚设字线(例如,s-dwl)。

74.下面示例性地说明存储单元阵列中的存储串的物理结构。图4是根据本技术实施方式的存储串400与各个控制线连接的物理结构剖面示意图。其中,存储串400可例如为图3示出的存储串str11。

75.如图4所示,存储串400可包括由外向内依次设置的电荷阻挡层401、电荷捕获层402、隧穿层403以及沟道层404。其中,电荷阻挡层401、电荷捕获层402、隧穿层403可被称为

功能层405。示例性地,电荷阻挡层401、电荷捕获层402、隧穿层403的材料可依次为氧化硅、氮化硅、氧化硅。沟道层404的材料可为半导体材料,例如p型掺杂多晶硅。

76.在一些示例中,漏极选择线dsl1、漏极虚设字线d-dwl、字线wl1~wln、源极虚设字线s-dwl、源极选择线ssl可沿着存储串400的延伸方向(例如,z方向)依次间隔地设置。上述各个控制线(例如,wlk)可围绕电荷阻挡层401设置并与电荷阻挡层401接触。示例性地,上述各个控制线(例如,wlk)的材料可包括钨、掺杂的多晶硅或者任何合适的导电材料。

77.在一些示例中,每条字线(例如,wlk)和与该字线wlk对应的部分功能层405、沟道层404共同构成存储单元(例如,mck

11

)。例如,对字线wlk施加电压,可使沟道层404中的电荷(例如,电子)注入至电荷捕获层402,或者通过字线wlk及其它控制线的配合,使得沟道层404中的电荷(例如,空穴)注入至电荷捕获层402中。如图4所示,在z方向排列的多个存储单元(例如,mc1

11

~mcn

11

)共享沟道层404,换言之,多个存储单元(例如,mc1

11

~mcn

11

)可在z方向上串联排列(类似于nand门)。

78.需要说明的是,如前文所述,对于一个存储单元(例如,mck

11

)而言,由电介质材料(例如,氮化硅)制备的电荷捕获层402可类似于陷阱,使得电荷注入其中后难以逃脱,故这种存储单元可被称为电荷捕获型存储单元。在另一些示例中,功能层可依次包括电荷阻挡层、浮栅层以及隧穿层,浮栅层可例如由导电材料制备,当电荷注入至浮栅层后,由电介质材料制备的、且位于浮栅层两侧的电荷阻挡层和隧穿层可使电荷保存在浮栅层中,而不发生电荷逃脱,故这种存储单元可被称为浮置浮栅型存储单元。

79.在一些示例中,沟道插塞406可位于存储串400的一端,并与位线(例如,bl1)连接。例如,沟道插塞406可位于隧穿层403内侧并与沟道层404接触。示例性地,沟道插塞406的材料可为半导体材料,例如n型掺杂的多晶硅。在存储串400的远离沟道插塞406的另一端,沟道层404可与源极线acs连接。例如,沟道层404凸出于功能层405的端面,并延伸至源极线acs中。示例性地,源极线acs的材料可为半导体材料,例如n型掺杂的多晶硅。值得注意的是,各个存储串(例如,图3示出的存储串str11~strmp)可具有相同的物理结构,并且多个存储串(例如,图3示出的存储串str11~strmp)可连接至相同的源极线acs。

80.图5是根据本技术实施方式的非易失性存器的擦除操作方法500的流程图。图6是根据图5示出的擦除操作方法500的各个控制线的电压波形示意图。下面进一步地结合图3示出的存储单元阵列320所包括的多个存储串str11~strmp和图4示出的存储串400的物理结构说明擦除操作方法500和各个控制线的电压变化情况。其中,图6示出各个控制线的电压变化曲线中实线表示由控制电压所实现,虚线表示由其它控制电压的耦合作用所实现。在本技术中,接地电压vgnd为接近0v的电压,例如,接地电压vgnd在相对于0v的-10%~10%范围区间内浮动。

81.如图3所示,当存储串str11中的存储单元mck

11

为待擦除的存储单元时,该存储单元mck

11

可被称为选择的存储单元。该存储单元mck

11

所在的存储串str11可被称选择的存储串(即,第一存储串)。进一步地,与该选择的存储单元mck

11

连接的字线可被称为选择的字线sel wl(即,第一字线wlk),而除了选择的字线wlk以外字线可被称为未选择的字线unsel wl(即,第二字线wl1~wl3、wln-2~wln等);与该选择的存储串str11连接的位线可被称为选择的位线sel bl(即,第一位线bl1),而除了选择的位线bl1以外位线可被称为未选择的位线unsel bl(即,第二位线blm等);与该选择的存储串str11中的漏极选择晶体管dst

11

连

接的漏极选择线可被称为选择的漏极选择线sel dsl(即,第一漏极选择线dsl1),而除了选择的漏极选择线dsl1以外漏极选择线可被称为未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp等)。

82.如图3和图6所示,擦除操作过程可依次包括预擦除阶段、擦除阶段以及恢复阶段。其中,预擦除阶段为该擦除周期内t4时刻之前的时间段,擦除阶段为该擦除周期内t4至t5时刻之间的时间段,恢复阶段为该擦除周期内的t5时刻之后的时间段。在一些示例中,在t0时刻之前,与选择的存储单元mck

11

相关的各个控制线,例如选择的位线sel bl(即,第一位线bl1)、选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)、选择的字线sel wl(即,第一字线wlk)、未选择的字线unsel wl(即,第二字线wl1~wl3、wln-2~wln等)、源极选择线ssl、漏极虚设字线d-dwl以及源极虚设字线s-dwl可均保持接地电压vgnd。

83.在预擦除阶段内的t0时刻之后,使选择的位线sel bl(即,第一位线bl1)上的电压以预设斜率r1上升,并在预擦除阶段结束(即,擦除阶段开始)的t4时刻达到目标擦除电压vt-erase。在t4时刻至t5时刻的擦除阶段,使选择的位线sel bl(即,第一位线bl1)上的电压保持目标擦除电压vt-erase不变。例如,目标擦除电压大于10v。需要说明的是,在一些示例中,可通过对选择的位线sel bl(即,第一位线bl1)施加与例如预设斜率r1相同的电压,使得选择的位线sel bl(即,第一位线bl1)上的电压按照例如在t0时刻至t4时刻之间以预设斜率r1上升,并在t4时刻至t5时刻之间保持目标擦除电压vt-erase的趋势变化。在另一些示例中,可例如在t0时刻施加目标擦除电压vt-erase,由于控制线(例如,第一位线bl1)可等效为串联的电容和电阻,在电容耦合效应的影响下,使得选择的位线sel bl(即,第一位线bl1)上的电压按照例如在t0时刻至t4时刻之间以预设斜率r1上升,并在t4时刻至t5时刻之间保持目标擦除电压vt-erase的趋势变化。

84.在预擦除阶段的t2时刻之前,向选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)施加接地电压vgnd,并在t2时刻之后使选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)保持浮置状态。在预擦除阶段的t2时刻之后,由于例如沟道层404(参考图4)电压的耦合作用,选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)按照例如在t2时刻至t4时刻之间以预设斜率r1上升,并在擦除阶段的t4时刻至t5时刻之间保持其目标电压v-sel dsl的趋势变化。换言之,通过在t0时刻至t2时刻之间向选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)施加接地电压vgnd,使得选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)不受到耦合作用的影响。

85.需要说明的是,在预擦除阶段的t2时刻,选择的位线sel bl(即,第一位线bl1)上的电压(或者说传递到由例如n型掺杂的多晶硅材料制备的沟道插塞406(参考图4)上的电压)与选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)上的电压的差值能够产生gidl电流,从而使得空穴(图4示出的方向

①

)进入选择的存储串(例如,第一存储串str11)中的漏极选择晶体管dst

11

所对应沟道层404(参考图4)处,进而使得沟道层404的电势升高。示例性地,在预擦除阶段的t2时刻之后,由于沟道层404(参考图4)电压的耦合作用,选择的位线sel bl(即,第一位线bl1)上的电压与选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)上的电压可保持恒定的差值以产生gidl电流。示例性地,t2时刻与t0时刻的时间间隔还可满足:使得在t2时刻之后,选择的漏极选择线sel dsl(即,dsl1)在保持浮置状态的情况下所能达到的目标电压v-sel dsl与目标擦除电压vt-erase的差值小于擦除阈值(例如,

大于10v),以避免选择的存储串(例如,第一存储串str11)中的漏极选择晶体管dst

11

被擦除。需要说明的是,擦除阈值为能够使沟道层404内的空穴注入至电荷捕获层402时,沟道层404与字线或选择线之间的电压差值的最小值。

86.在擦除阶段t4至t5时刻之间,向与待擦除的存储单元mck

11

连接的选择的字线sel wl(即,第一字线wlk)施加偏置电压,例如该偏置电压为接地电压vgnd,这样由于选择的位线sel bl(即,第一位线bl1)上的电压t0时刻至t4时刻不断地上升,并且通过产生gidl电流,使沟道层404内的电压也在t0时刻至t4时刻不断地上升,直到预擦除阶段结束(即,擦除阶段开始)的t4时刻沟道层404内的电压达到了目标擦除电压vt-erase,当向选择的字线sel wl(即,第一字线wlk)施加偏置电压(例如,接地电压vgnd)时,由于目标擦除电压vt-erase与偏置电压(例如,接地电压vgnd)的差值大于擦除阈值,则选择的存储单元mck

11

根据fn隧穿效应被擦除。可选地,可从预擦除阶段至擦除阶段始终向与待擦除的存储单元mck

11

连接的选择的字线sel wl(即,第一字线wlk)施加上述偏置电压。

87.需要说明的是,虽然本技术以选择的位线sel bl(即,第一位线bl1)和选择的字线sel wl(即,第一字线wlk)的数量为一个进行了示例性地描述,但是选择的位线sel bl(即,第一位线bl1)和选择的字线sel wl(即,第一字线wlk)的数量并不限于一个,可根据存储单元的实际擦除需求,选择性地确定出选择的位线sel bl(即,第一位线bl1)和选择的字线sel wl(即,第一字线wlk)的数量,本技术对此不做具体地限定。

88.根据本技术一些实施方式提供的非易性存储器的擦除操作方法500,利用gidl电流产生进入存储块中的一些选择的存储串中的空穴,从而使得这些选择的存储串的沟道层的电势升高,同时利用一些选择的字线与选择的存储串的沟道层的电势差,使得选择的存储串中的至少一个选择的存储单元被擦除。在一些示例性地实施方式中,非易性存储器以存储块所包括的多个存储单元为单位进行整体擦除,与该示例性实施方式相比,本技术一些实施方式提供的非易性存储器的擦除操作方法500能够实现对选择性地存储块内对存储单元擦除,使得非易性存储器的擦除操作更加灵活。同时,还可通过选择性地擦除部分存储单元,增加选择性地增加这部分存储单元的读取窗口,以提高存储单元的读取准确性。

89.在一些示例中,在预擦除阶段的t3时刻之前,向选择的字线sel wl(即,第一字线wlk)以外的未选择的字线unsel wl(例如,第二字线wl1~wl3、wln-2~wln等)施加接地电压vgnd,并在t3时刻之后的预擦除阶段和擦除阶段保持上述未选择的字线(例如,第二字线wl1~wl3、wln-2~wln等)为浮置状态。相似地,在t3时刻之后,由于沟道层404(参考图4)电压的耦合作用,上述未选择的字线(例如,第二字线wl1~wl3、wln-2~wln等)按照例如在预擦除阶段的t3时刻至t4时刻之间以预设斜率r1上升,并在擦除阶段的t4时刻至t5时刻之间保持其目标电压v-unsel wl的趋势变化。示例性地,t3时刻与t0时刻的时间间隔还可满足:在t3时刻之后,上述未选择的字线(例如,第二字线wl1~wl3、wln-2~wln等)在保持浮置状态的情况下所能达到的目标电压v-unsel wl与目标擦除电压vt-erase的差值小于擦除阈值,以避免选择的存储串(例如,第一存储str11)中的未选择的存储单元(例如,mc1

11

~mc3

11

、mcn-2

11

~mcn

11

等)被擦除。

90.可以理解的是,上述未选择的字线(例如,第二字线wl1~wl3、wln-2~wln等)在保持浮置状态的情况下所能达到的目标电压v-unsel wl与目标擦除电压vt-erase的差值大于这些未选择的字线(例如,第二字线wl1~wl3、wln-2~wln等)对应的未选择的存储单元

(例如,mc1

11

~mc3

11

、mcn-2

11

~mcn

11

等)的开启电压,使得漏极选择晶体管dst

11

所对应沟道层404(参考图4)的相对较高电势能够传递至未选择的存储单元(例如,mc1

11

~mc3

11

、mcn-2

11

~mcn

11

等)所对应的各处沟道层404,从而使得沟道层404(参考图4)在各处的电势比较均匀,进而改善选择的存储单元mck

11

的擦除效果。

91.需要说明的是虽然本技术示例了t3时刻晚于t2时刻,但是可根据上述未选择的字线(例如,第二字线wl1~wl3、wln-2~wln等)实际需求的电压情况(例如,避免未选择的存储单元(例如,mc1

11

~mc3

11

、mcn-2

11

~mcn

11

等)使得被擦除和/或使未选择的存储单元(例如,mc1

11

~mc3

11

、mcn-2

11

~mcn

11

等)开启)而确定。换言之,t3时刻可与t2时刻重叠,或者t3时刻可早于t2时刻。

92.在一些示例中,在预擦除阶段内的t0时刻之后,使源极选择线ssl上的电压以预设斜率r1上升,并在擦除阶段保持所达到的目标擦除电压vt-erase。换言之,可向源极选择线ssl施加与选择的位线sel bl(即,第一位线bl1)相同变化趋势的电压,使得源极选择晶体管关断,以避免沟道层404(参考图4)内的高电势进一步地传递至源极线acs,从而影响擦除效果。在另一些示例中,可在预擦除阶段和擦除阶段,始终保持源极选择线ssl为浮置状态,同样地能够避免沟道层404(参考图4)内的高电势进一步地传递至源极线acs,从而影响擦除效果。

93.在一些示例中,如图3所示,对于选择的位线sel bl(即,第一位线bl1)与未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp)所定位到的未选择的存储串(例如,str1p等),如图6所示,在预擦除阶段内的t1时刻之前,向未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp等)施加接地电压vgnd,并在预擦除阶段内t1时刻之后以及擦除阶段t4时刻至t5时刻之间保持未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp等)为浮置状态,其中,t1时刻早于t2时刻。与在预擦除阶段的t2时刻之前向选择的漏极选择线sel dsl(即,第一漏极选择鹅涎dsl1)施加接地电压vgnd相似,通过在预擦除阶段的t1时刻之后向未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp等)施加接地电压vgnd,使得未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp等)不受到耦合作用的影响。

94.需要说明的是,由于t1时刻早于t2时刻,选择的位线sel bl(即,第一位线bl1)上的电压(或者说传递到由例如n型掺杂的多晶硅材料制备的沟道插塞406(参考图4)上的电压)与未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp等)上的电压的差值不能够产生gidl电流,从而不会使得空穴进入未选择的存储串(例如,str1p等)中的漏极选择晶体管(例如,dst

1p

等)所对应沟道层处,进而使得未选择的存储串(例如,str1p等)不具备沟道层的电势升高的条件,故未选择的存储串(例如,str1p等)上的各个未选择的存储单元不会被擦除。

95.在一些示例中,如图3所示,对于未选择的位线unsel bl(即,第二位线blm等)与选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)所定位到的未选择的存储串(例如,strm1等),如图6所示,在预擦除阶段的t2时刻之后,使未选择的位线unsel bl(即,第二位线blm等)上的电压以预设斜率r1上升,并在预擦除阶段结束(即,擦除阶段开始)的t4时刻达到的目标非擦除电压vt-nonerase。在t4时刻至t5时刻的擦除阶段,使未选择的位线unsel bl(即,第二位线blm等)上的电压保持目标非擦除电压vt-nonerase不变。需要说明的是,在一些示例中,可通过对未选择的位线unsel bl(即,第二位线blm等)施加与例如预

unsel dsl与该漏极虚设存储单元d-dmc

1p

在浮置状态下所达到的目标电压v-ddwl的差值不会使得该漏极虚设存储单元d-dmc

1p

所对应的沟道层处的电荷不会发生hci(热载流子注入),从而避免该漏极虚设存储单元d-dmc

1p

被干扰。

101.在一些示例中,如图3所示,在每个存储串(例如,str11)包括设置于源极选择晶体管(例如,sst

11

)和多个存储单元(例如,mc1

11

~mcn

11

)之间的源极虚设存储单元(例如,s-dmc

11

)的情况下,如图6所示,在预擦除阶段的t1时刻之前,向源极虚设字线s-dwl施加接地电压vgnd,并在t1时刻之后保持源极虚设字线s-dwl为浮置状态。例如,向源极虚设字线s-dwl和未选择的漏极选择线unsel dsl(即,第二漏极选择线dslp等)在相同的时刻施加相同变化趋势的电压(即,接地电压vgnd)。

102.需要说明的是,对于选择的存储串str11而言,由于沟道层404(参考图4)内的高电势是在靠近漏极选择晶体管dst

11

处所产生的,在沟道层404(参考图4)内的高电势向靠近源极漏极选择晶体管sst

11

传递的过程中,沟道层404(参考图4)内的电势可能会呈现出沿着从漏极端向源极端降低的趋势,在该示例中,通过在t0时刻向源极虚设字线s-dwl施加上述电压可使得沟道层404(参考图4)与源极虚设存储单元s-dmc

11

所对应处的电势升高,从而在沟道层404(参考图4)各处的高电势比较均匀,进而改善选择的存储单元mck

11

的擦除效果。

103.在一些示例中,在擦除阶段之后的恢复阶段,诸如选择的位线sel bl(即,第一位线bl1)、选择的漏极选择线sel dsl(即,第一漏极选择线dsl1)、选择的字线sel wl(即,第一字线wlk)、未选择的字线unsel wl(即,第二字线wl1~wl3、wln-2~wln等)、源极选择线ssl、漏极虚设字线d-dwl以及源极虚设字线s-dwl可恢复至预擦除阶段的初始默认状态例如接地电压vgnd,以为下一周期执行擦除操作做准备。

104.在以非易失性存储器作为硬件平台实现神经网络的训练过程中,若非易性存储器以存储块所包括的多个存储单元为单位进行整体擦除,则不利于实现大规模的深度神经网络运算。下文中将对神经网络以及上述擦除操作方法应用于神经网络进一步地说明。

105.神经网络可由输入层、输出层以及输入层与输出层之间的一个或多个隐藏层构成,每一层包括一个或多个神经元。根据神经网络中各个神经元的连接关系,使输入以一种数学变换的方式遍历各个层,并转换为每个输出的概率。

106.图7是根据本技术实施方式的三层神经网络结构700示意图。如图7所示,神经网络700中的圆圈表示神经元,连接线表示前一层的各个神经元与当前层的一个神经元之间的可变权重。图7示出了具有三个输入神经元(i1、i2、i3)的输入层、具有两个输出神经元(o1、o2)的输出层,以及具有四个隐藏神经元(h1、h2、h3、h4)的隐藏层。神经元(例如,隐藏神经元h1)可被实现为一种数学函数,该数学函数接收多个输入(i1、i2、i3)并将它们加权后进行累加以产生输出(o

h1

=i1ω1+i2ω2+i3ω3)。进一步地,隐藏神经元(例如,h1)产生的输出o

h1

可作为输出各个输出神经元(例如,o1)的一个输入。输出神经元产生的输出可作为神经网络700的输出。

107.在一些实施方式中,权重(例如,ω1、ω2、ω3)可利用训练过程而实现调整。此外,神经元(例如,隐藏神经元或输出神经元)可具有阈值,使得当加权后的输入累加值超过该阈值时,而产生输出(即,后一层的输入或神经网络的输出)。可选地,神经元的输出可通过一些非线性函数(例如,sigmoid函数)来计算。虽然图7示出了一个隐藏层,但是复杂的深度神经网络(dnn)可具有许多此类的隐藏层。

108.基于训练后的神经网络能够解决例如模式识别等问题。例如,经过训练后的神经网络能够用于推断出图像中的水果类别。图8是根据本技术实施方式的神经网络的训练过程的流程图800。例如,该训练过程可基于有监督的学习规则。下面结合图7示出的神经网络700详细说明训练过程800。

109.在步骤801中,输入神经元i1、i2、i3(参考图7)接收训练输入。示例性地,训练输入为一组图像,每张图像中均包括待识别的一种水果类别。

110.在步骤802中,可使用当前权重,将输入神经元i1、i2、i3连接到下一层的隐藏神经元h1、h2、h3、h4。进一步地,将隐藏神经元h1、h2、h3、h4连接到下一层的输出神经o1、o2,并将隐藏神经元h1、h2、h3、h4的输出作为下一层输出神经元o1、o2的输入。进一步地,输出神经元o1、o2的输出作为神经网络500的输出。换言之,来自输入层的训练输入以这种方式遍历所有隐藏层直至输出层进行传播。示例性地,如前文所述,在利用神经网络识别水果类别的示例中,隐藏层和输出层使用当前权重来计算图像中的水果为特定类别的概率,并将目标水果类别的标签在步骤803处返回。

111.在步骤804中,确定使用当前权重,神经网络输出的特定水果类别的概率是否满足足够准确的标签,并且如果是,则训练完成(步骤805)。如果结果不够准确,则神经网络在步骤806处调整权重,然后循环返回到步骤804,以使用经调整的权重再次运行输入数据。

112.当步骤805确定了神经网络的权重,基于该权重可用于推断前文所述的图像中的水果类别,并且所确定的权重,可存储在非易失性存储器320(参见图3)中。

113.图9是根据本技术实施方式的用于执行神经网络的非易失性存储器的操作方法900的流程图。图10是根据图3示出的存储单元阵列320中的二维存储单元阵列1020-1的等效电路图。下面结合图9和图10对操作方法900的进一步地说明。操作方法900可利用例如图10示例的存储单元阵列320的一部分(即,二维存储单元阵列1020-1)来执行神经网络的训练过程中的前向传播和反向传播,以及推断过程。

114.如图10所示,二维存储单元阵列1020-1可等效为神经网络(例如,图7示例的神经网络700)的一个隐藏层或输出层(以下简称当前层)中的多个神经元。对于二维存储单元阵列1020-1中的各个存储串(例如,str11~strm1),其可由相同的漏极选择线dsl1控制,以使得图10示出的多个存储串str11~strm1能够在同一漏极选择线dsl1的控制下与多条位线(例如,bl1~blm)接通。

115.在步骤901中,如图9所示,相同字线(例如,wl1)连接的、且位于不同的存储串(例如,str11~strm1)上的多个存储单元(例如,mc1

11

~mc1

m1

)可对应于当前层中的一个神经元。例如,二维存储单元阵列1020-1可对应于当前层中的n个神经元。进一步地,可向多条位线(例如,bl1~blm)分别施加多个位线电压(例如,v

bl1

~v

blm

),每条位线(例如,bl1~blm)上的位线电压(例如,v

bl1

~v

blm

)可对应于当前层中一个神经元的一个输入。换言之,多条位线上的多个位线电压(例如,v

bl1

~v

blm

)可对应于当前层中一个神经元的多个输入。例如,对于当前层中一个神经元来说,其可接收m个输入(即,m条位线上的m个位线电压v

bl1

~v

blm

)。

116.在步骤902中,一个存储单元(例如,mc1

11

)的电导值g1

11

可作为对应于神经元的一个输入(例如,施加到位线bl1上的位线电压v

bl1

)的权重。需要说明的是,如前文所述,对于浮置浮栅型或电荷捕获型存储单元而言,各个存储单元根据注入至电荷捕获层或浮栅层的电荷数量的不同,各个存储单元所呈现出的电导值(即,电阻值的倒数)不同。在该步骤中,

可根据存储单元的上述特性以及存储单元阵列的电连接特性,通过对存储单元所连接的字线施加读取电压,从而感测流经该存储单元的电流,为后续步骤903确定神经元的输出提供执行条件。

117.图11是根据本技术实施方式的为确定神经元的输出向n条字线所施加的电压的波形图。如图11所示,读取脉冲电压vread(灰色)依次施加至字线wl1至wln,以依次确定出与字线wl1连接的各个存储单元(例如,mc1

11

~mc1

m1

)的电流值直至字线wln连接的各个存储单元的电流值。在一些示例中,由于在步骤901中已对各个存储串str11~strm1连接的位线bl1~blm施加的位线电压v

bl1

~v

blm

,在t1时间对字线wl1施加读取脉冲电压vread时,与各个存储串str11~strm1的一端(例如,未连接位线的一端)连接的例如感测电路(未示出)能够感测出流经与字线wl1连接的各个存储单元mc1

11

~mc1

m1

所在的多个存储串str11~strm1的电流值。

118.在步骤903中,在一个存储单元(例如,mc1

11

)的电导值(例如,g1

11

)作为神经网络的一个神经元的一个输入(例如,v

bl1

)对应的权重的情况下,则该一个输入(例如,v

bl1

)与对应的权重(例如,g1

11

)的乘积(即,g1

11

×vbl1

)可为该神经元的输出一部分。进一步地,由于字线wl1连接多个存储单元mc1

11

~mc1

m1

,多个输入(例如,v

bl1

~v

blm

)与分别对应的多个权重(例如,g1

11

~g1

m1

)的乘积(即,(g1

11

×vbl1

)~(g1

m1

×vblm

))能够确定出。进一步地,可通过感测公共源极线acs中的总电流实现将上述各个乘积相加,从而确定出字线wl1对应的一个神经元的输出(即,),进而可确定神经网络中当前层的n个神经元的n个输出。

119.在一些示例中,如图11所示,在t1时间对字线wl1施加读取脉冲电压vread期间,可对字线wl2~wlm施加偏置脉冲电压vbias-p。例如,偏置脉冲电压vbias-p大于读取脉冲电压vread。换言之,对于存储串str11来说,存储单元mc1

11

可被称为待读取的存储单元,存储串str11中的除了存储单元mc1

11

以外的其它存储单元可被称为未待读取的存储单元,当对未待读取的存储单元所施加的偏置脉冲电压vbias-p大于待读取的存储单元mc1

11

所施加的读取脉冲电压vread的情况下,能够在感测流经待读取的存储单元mc1

11

的电流时有效地避免未待读取的存储单元的影响,从而提高获取神经元输出的准确性。

120.需要说明的是,图11示出的字线wl1~wln的电压波形图仅为示例性地,在其它示例中,从时域上来说,读取脉冲电压vread可并非逐一地施加至字线wl1~wln,换言之,读取脉冲电压vread可省略任意一个或多条字线不对其施加读取脉冲电压vread,从而使得该一条或多条字线所连接的存储单元并不对应于神经网络中当前层的一个神经元。

121.图12是根据本技术另一实施方式的用于执行神经网络的非易失性存储器的操作方法的示意图。如图12所示,漏极选择线dsl1连接的多个存储串中的多个存储单元可组成一个二维存储单元阵列(例如,第一存储单元阵列1220-1)。相似地,第二存储单元阵列1220-2中的多个存储串可连接至另一个漏极选择线(未示出),第p存储单元阵列中的多个存储串可连接至又一个漏极选择线(例如,dslp(参考图3))。换言之,第一存储单元阵列1220-1、第二存储单元阵列1220-2至第p存储单元阵列1220-p可分别由p个漏极选择线控制。其中,第一存储单元阵列1220-1可与图10示例的二维存储单元阵列1020相同。

122.在一些示例中,对于第一存储单元阵列1220-1而言,可通过向漏极选择线dsl1施加导通电压(即,使连接至漏极选择线dsl1的多个漏极选择晶体管导通的电压),使得第一

存储单元阵列1220-1中的多个存储串str11~strm1的一端能够接收位线电压(例如,v

bl1

~v

blm

)。即,如前文所详细说明的,第一存储单元阵列1220-1中对应的各个神经元可作为神经网络当前层中的多个神经元的一部分,并能够在预定的时间内产生对应的输出。

123.进一步地,可通过向第二存储单元阵列1220-2至第p存储单元阵列中的一个或多个所对应的漏极选择线施加导通电压,使得第二存储单元阵列1220-2至第p存储单元阵列1220-p中的至少部分二维存储单元阵列能够作为神经网络当前层中的多个神经元的一部分,并行地在预定的时间内产生对应的输出,从而有效地提高利用非易失性存储器执行神经网络算法中前向传播或推断过程的操作效率。

124.在步骤904中,如前文所述,在神经网络的训练过程中,若神经网络输出的概率未满足足够准确的标签,那么需要调整神经网络中的各个权重。进一步地,由于存储单元的电导值作为每个神经元中的输入对应的权重,那么可通过调整存储单元的电导值,来实现每个神经元中的输入对应的权重调整。需要说明的是,通过神经网络输出的概率是否满足足够准确的标签,来调整神经网络中的各个权重可被称为神经网络的反向传播(backward propagation,bp)。

125.图13是根据本技术实施方式的存储单元的电导值与执行编程操作和擦除操作的时间的曲线图。如图13所示,在一些示例中,随着对存储单元执行编程操作执行时间的增加,存储单元的电导随之降低。具体地,例如随着对存储单元执行编程操作的时间的增加,存储单元的沟道层中的更多的电荷被注入至电荷捕获层402(参见图4),从而使得存储单元的电导值降低,即调整了存储单元的电导值。在另一些示例中,还可通过增加对存储单元执行编程操作的脉冲强度,使得存储单元的沟道层404(参见图4)中的更多的电荷被注入至电荷捕获层402(参见图4),以调整存储单元的电导值。

126.下面参照图10示出的二维存储单元阵列1020-1,对其中的一个存储单元mc1

11

执行编程操作进行示例性说明。示例性地,存储单元mc1

11

可被称为待编程的存储单元。对该待编程的存储单元执行编程操作时,可对与其连接的字线wl1施加编程电压(例如,15~20v),并打开存储单元mc1

11

所在的存储串str11上的漏极选择晶体管dst1

11

,对与存储单元mc1

11

所在的存储串str11连接的位线bl1施加例如接地电压。在字线wl1的高电压的作用下,电荷(例如,电子)隧穿后注入电荷捕获层402(参考图4)充电,以达到调整存储单元mc1

11

的电导值的作用。可选地,可对其它位线(例如,blm等)施加禁止编程电压(例如,2v),以阻碍电荷发生隧穿效应,以抑制存储串(例如,strm1等)中的与字线wl1连接的其他存储单元被编程。

127.示例性地,再次参考图12,可并行地调整第二存储单元阵列1220-2至第p存储单元阵列中的一个或多个存储单元阵列中的存储单元的电导值,从而有效地提高利用非易失性存储器执行神经网络算法中反向传播的操作效率。

128.在另一些示例中,随着对存储单元执行擦除操作执行时间的增加,存储单元的电导值随之增加。具体地,例如随着对存储单元执行擦除操作的时间的增加,存储单元的电荷捕获层402(参考图2)中更多的空穴注入至电荷捕获层402(参见图4),从而使得存储单元的电导值增加,即调整了存储单元的电导值。示例性地,可参考图5示出的擦除操作方法500,当第一位线和第一字线的数量为一个时,可实现对一个存储单元(例如,mc1

11

)执行擦除操作,从而使得该存储单元的电导值增加,即调整了该存储单元的电导值。其中,擦除操作方法500已在前文中详细地说明,本技术在此不再赘述。

129.在一些示例性实施方式中,在非易性存储器以存储块所包括的多个存储单元为单位进行整体擦除的情况下,通常采用存储单元对的电导差值作为神经网络中神经元的一个输入所对应的权重(即,w=g

+-g-),换言之,在相同存储容量(即,存储单元数量)前提下,通过非易失性存储器中的多个存储单元存储神经网络的参数的利用率将减半。同时,采用电导差值表征一个输入所对应的权重,需要在非易失性存储器中增设例如减法器等硬件,还会消耗一部分存储容量来存储这些电导差值。另一方面,在调整权重过程中,需要通过对两个存储单元编程配合来实现每个权重独立地调整,然而对于复杂且训练次数较多的神经网络,当两个存储单元的电导值达到上限后,则无法继续对权重进行调整。若需要继续对权重进行调整,可通过对存储块所包括的多个存储单元为单位进行整体擦除,这样会摧毁之前的训练成果。

130.根据本技术一些实施方式提供的适用于神经网络的非易性存储器,与上述示例性实施方式相比,利用非易失性存储器中的单个存储单元的电导值作为神经网络中神经元的一个输入所对应的权重,能够提高利用非易性存储器来存储神经网络的参数的存储利用率,有利于发挥非易性存储器高存储密度的优势。同时,无需增设例如减法器来计算电导差值,有利于与现有的外围电路兼容,并且也可避免消耗一部分存储容量来存储这些电导差值,进一步地提高非易性存储器的存储利用率。另一方面,通过对调整单个存储单元的电导值来调整权重,能够应对当两个存储单元的各自电导值达到上限后,无法继续对权重进行调整的问题,有利于实现更加复杂的深度神经网络。

131.以上描述仅为本技术的实施方式以及对所运用技术原理的说明。本领域技术人员应当理解,本技术中所涉及的保护范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离技术构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本技术中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1