一种基于忆阻器阵列的矩阵乘法运算电路及其使用方法

1.本发明属于矩阵乘法运算电路技术领域。具体涉及一种基于忆阻器阵列的矩阵乘法运算电路。

背景技术:

2.矩阵乘法运算在物理研究、图像处理、线性规划、信号处理等多个领域被广泛应用。矩阵乘法运算速度的提高能使上述多种应用中数据处理的速度得到提升。目前的大规模矩阵乘法运算都是在计算机中通过矩阵乘法运算程序来实现的,但其运算速度受以下两种因素的制约而无法得到有效的提高:一是计算机在执行矩阵乘法运算时,运算器和存储器之间需频繁地进行数据传输,使得大量的时间被消耗在运算器和存储器之间的通信中,运算速度难以得到明显提高。二是计算机程序在同一时刻只能执行两个数据间的运算,这也使得矩阵乘法运算的时间大幅增加。因此,如何解决以上两个问题以提高矩阵乘法运算的速度为本领域技术人员所关注。

3.忆阻器阵列是忆阻器的一种组合电路,它能够以电阻的形式存储多个模拟量,且仅需在忆阻器阵列的各行施加电压就能并行完成乘积累加的运算,因此可以避免运算器和存储器之间因进行数据传输而造成的时间消耗。此外,使用忆阻器阵列可以同时实现多组数据的运算,能够解决计算机因依次执行单组数据间的运算而导致的低速问题。在矩阵乘法运算电路中,矩阵元素与忆阻器阵列中的忆阻器具有相同的排列方式,且忆阻器阵列能够在一个计算周期内完成向量与矩阵间的乘法运算,因此,基于忆阻器阵列的电路在矩阵乘法运算电路的研究中具有很大价值。

4.nourazar m等人(nourazar m,rashtchi v,azarpeyvand a,et al.memristor-based approximate matrix multiplier[j].analog integrated circuits and signal processing,2017,93(3):363-373)将数字电路和忆阻器阵列相结合,设计了一种矩阵乘法运算电路。该电路用忆阻器阵列中每个忆阻器的电导值表征矩阵中的一个元素,用施加到忆阻器阵列各行的电压表示与矩阵相乘的向量。进行运算时控制器将表征向量元素的电压施加到忆阻器阵列的对应行,同时读取忆阻器阵列的输出电压作为向量矩阵乘法运算的结果,然后通过多次向量矩阵乘法完成矩阵与矩阵间的乘法运算。虽然该矩阵乘法运算电路可以通过模拟运算大幅提高矩阵乘法的运算效率,但实现过程中的每一次向量矩阵乘法运算都需要控制器执行输入和读取操作,导致矩阵乘法运算的速度受到限制。此外,该电路中各忆阻器的阻值调节方法较为复杂,这也导致更多的时间被消耗在忆阻器的阻值调节过程中。

[0005]

zhang y等人(zhang y,wang x,friedman e g.memristor-based circuit design for multilayer neural networks[j].ieee transactions on circuits and systems i:regular papers,2017,65(2):677-686)用多个忆阻器阵列设计了一种多层人工神经网络硬件电路。该电路用一个忆阻器阵列表示一层神经网络,而神经网络的突触权重则由阵列中各忆阻器的电导值表示。当在忆阻器阵列的各行施加电压后,它的输出电压

就是向量矩阵乘法运算的结果,同时作为下一层神经网络的输入电压施加到下一个忆阻器阵列的各行中,依次完成每层神经网络中的向量矩阵乘法运算。虽然该电路以模拟计算的方式提高了矩阵乘法运算速度,但由于该电路只能执行向量矩阵乘法运算,故每执行一次运算都需要重新施加电压到忆阻器阵列的各行,使得运算的速度难以进一步提高。

[0006]

cai r z等人(ruizhe cai,ao ren,sucheta soundarajan,yanzhi wang.a low-computation-complexity,energy-efficient,and high-performance linear program solver based on primal dual interior point method using memristor crossbars[j].nano communication networks,2018,18:62-71)设计了一种基于忆阻器阵列的线性方程求解器。忆阻器阵列中每个忆阻器的电导值和阵列中各行所施加的电压分别表示方程组系数矩阵中的系数和解向量,然后使用忆阻器阵列进行向量和矩阵的乘法运算,并通过外部控制器进行比较、迭代等操作以得到方程的最优解。虽然整个系统实现了计算过程的模拟运算,但算法的实现需要由外部控制器来完成,因此,该方法的运算速度受到了控制器运算速度的约束。此外,该电路中的忆阻器阵列只能保存正数,无法直接运算含有负数的矩阵。

[0007]

冉德成等人(冉德成,吴东,钱磊.面向深度学习推理的矩阵乘法加速器设计[j].计算机工程,2019,45(10):40-45.doi:10.19678/j.issn.1000-3428.0052372.)设计了一种面向深度学习推理的矩阵乘法运算电路。该电路主要通过多组数字电路模块完成矩阵乘法运算。虽然此方法能够在一定程度上提高矩阵乘法运算的速度,但是其控制功能是通过软件实现的,这使得矩阵运算速度始终受计算机性能的影响,无法获得更大提升。

技术实现要素:

[0008]

本发明旨在克服现有技术的缺陷,目的是提出一种运算速度快且操作简单的基于忆阻器阵列的矩阵乘法运算电路,该电路能够对任意二个包含正数和负数元素的实数矩阵进行矩阵乘法运算。

[0009]

为实现上述目的,本发明采用的技术方案是:

[0010]

为叙述简便起见,先将所述基于忆阻器阵列的矩阵乘法运算电路简称为矩阵乘法运算电路,且对所述矩阵乘法运算电路中的字母所表示的物理意义统一描述如下:

[0011]

i、j、k分别为大于等于2的自然数,m、n、l为符合下述相关不等式的自然数:

[0012]

1≤i≤m;

[0013]

1≤j≤n;

[0014]

1≤k≤l。

[0015]

所述矩阵乘法运算电路包括m个采样延时电路、2n+l个阻值调节电路、矩阵元素存储模块、n个一级运算电路、矩阵元素存储及运算模块、l个二级运算电路、矩阵运算结果存储模块、矩阵电阻和矩阵开关电路。

[0016]

所述矩阵乘法运算电路中:

[0017]

第1采样延时电路的端子clk、

……

、第i采样延时电路的端子clk、

……

、第m采样延时电路的端子clk与矩阵乘法运算电路的端子v

clk1

分别连接;第1采样延时电路的端子dn与第2采样延时电路的端子d

in

连接,

……

,第i-1采样延时电路的端子dn与第i采样延时电路的端子d

in

连接,

……

,第m-1采样延时电路的端子dn与第m采样延时电路的端子d

in

连接;第1采

样延时电路的端子d

in

与矩阵乘法运算电路的端子v

din

连接。

[0018]

第11阻值调节电路的端子clk、

……

、第1j阻值调节电路的端子clk、

……

、第1n阻值调节电路的端子clk、第21阻值调节电路的端子clk、

……

、第2j阻值调节电路的端子clk、

……

、第2n阻值调节电路的端子clk、第31阻值调节电路的端子clk、

……

、第3k阻值调节电路的端子clk、

……

、第3l阻值调节电路的端子clk与矩阵乘法运算电路的端子v

clk2

分别连接。

[0019]

第11阻值调节电路的端子w0、

……

、第1j阻值调节电路的端子w0、

……

、第1n阻值调节电路的端子w0、第21阻值调节电路的端子w0、

……

、第2j阻值调节电路的端子w0、

……

、第2n阻值调节电路的端子w0与矩阵乘法运算电路的端子v

w0

分别连接;第31阻值调节电路的端子w0、

……

、第3k阻值调节电路的端子w0、

……

、第3l阻值调节电路的端子w0与矩阵开关电路的端子s1分别连接,第31阻值调节电路的端子w0、

……

、第3k阻值调节电路的端子w0、

……

、第3l阻值调节电路的端子w0与矩阵电阻的端子r0分别连接。

[0020]

第11阻值调节电路的端子w

ref

、

……

、第1j阻值调节电路的端子w

ref

、

……

、第1n阻值调节电路的端子w

ref

、第21阻值调节电路的端子w

ref

、

……

、第2j阻值调节电路的端子w

ref

、

……

、第2n阻值调节电路的端子w

ref

、第31阻值调节电路的端子w

ref

、

……

、第3k阻值调节电路的端子w

ref

……

、第3l阻值调节电路的端子w

ref

与矩阵乘法运算电路的端子v

wref

分别连接。

[0021]

第11阻值调节电路的端子w1、

……

、第1j阻值调节电路的端子w1、

……

、第1n阻值调节电路的端子w1、第21阻值调节电路的端子w1、

……

、第2j阻值调节电路的端子w1、

……

、第2n阻值调节电路的端子w1、第31阻值调节电路的端子w1、

……

、第3k阻值调节电路的端子w1……

、第3l阻值调节电路的端子w1与矩阵乘法运算电路的端子v

w1

分别连接。

[0022]

第11阻值调节电路的端子w

in

与矩阵乘法运算电路的端子v

wa1

连接,

……

,第1j阻值调节电路的端子w

in

与矩阵乘法运算电路的端子v

wa

j连接,

……

,第1n阻值调节电路的端子w

in

与矩阵乘法运算电路的端子v

wan

连接;第21阻值调节电路的端子w

in

与矩阵乘法运算电路的端子v

wb1

连接,

……

,第2j阻值调节电路的端子w

in

与矩阵乘法运算电路的端子v

wbj

连接,

……

,第2n阻值调节电路的端子w

in

与矩阵乘法运算电路的端子v

wbn

连接;第31阻值调节电路的端子w

in

与第1二级运算电路的端子o

bout

连接,

……

,第3k阻值调节电路的端子w

in

与第k二级运算电路的端子o

bout

连接,

……

,第3l阻值调节电路中的端子w

in

与第l二级运算电路的端子o

bout

连接。

[0023]

矩阵元素存储模块的端子a

w1

与第11阻值调节电路的端子w

out

连接,

……

,矩阵元素存储模块的端子a

wj

与第1j阻值调节电路的端子w

out

连接,

……

,矩阵元素存储模块的端子a

wn

与第1n阻值调节电路的端子w

out

连接;矩阵元素存储模块的端子a

d1

与第1采样延时电路的端子d

out

连接,

……

,矩阵元素存储模块的端子a

di

与第i采样延时电路的端子d

out

连接,

……

,矩阵元素存储模块的端子a

dm

与第m采样延时电路的端子d

out

连接;矩阵元素存储模块的端子a

out1

与第1一级运算电路的端子o

ain

连接,

……

,矩阵元素存储模块的端子a

outj

与第j一级运算电路的端子o

ain

连接,

……

,矩阵元素存储模块的端子a

outn

与第n一级运算电路的端子o

ain

连接;矩阵元素存储模块的端子a

ws1

、

……

、a

wsi

、

……

、a

wsm

与矩阵乘法运算电路的端子v

aws1

、

……

、v

awsi

、

……

、v

awsm

对应连接;矩阵元素存储模块的端子a1、a

s1

、a

res

、a

s2

与矩阵乘法运算电路的端子v

a1

、v

s1

、v

res

、v

s2

对应连接。

[0024]

第1一级运算电路的端子o

astd

、

……

、第j一级运算电路的端子o

astd

、

……

、第n一级运算电路的端子o

astd

分别与矩阵乘法运算电路的端子v

astd

连接;第1一级运算电路的端子o

aout

与矩阵元素存储及运算模块的端子b

in1

连接,

……

,第j一级运算电路的端子o

aout

与矩阵元素存储及运算模块的端子b

inj

连接、

……

、第n一级运算电路的端子o

aout

与矩阵元素存储及运算模块的端子b

inn

连接。

[0025]

矩阵元素存储及运算模块的端子b

w1

与第21阻值调节电路的端子w

out

连接,

……

,矩阵元素存储及运算模块的端子b

wj

与第2j阻值调节电路的端子w

out

连接,

……

,矩阵元素存储及运算模块的端子b

wn

与第2n阻值调节电路的端子w

out

连接;矩阵元素存储及运算模块的端子b

out11

、b

out12

与第1二级运算电路的端子o

bin1

、o

bin2

对应连接,

……

,矩阵元素存储及运算模块的端子b

outk1

、b

outk2

与第k二级运算电路的端子o

bin1

、o

bin2

对应连接,

……

,矩阵元素存储及运算模块的端子b

outl1

、b

outl2

与第l二级运算电路的端子o

bin1

、o

bin2

连接;矩阵元素存储及运算模块的端子b

s1

与矩阵乘法运算电路的端子v

s1

对应连接。

[0026]

第1二级运算电路的端子o

bres

、o

bstd

、o

bs1

、o

bs2

、o

bsel1

、o

bsel2

与矩阵乘法运算电路的端子v

res

、v

bstd

、v

s1

、v

s2

、v

bs11

、v

bs12

对应连接,

……

,第k二级运算电路的端子o

bres

、o

bstd

、o

bs1

、o

bs2

、o

bsel1

、o

bsel2

与矩阵乘法运算电路的端子v

res

、v

bstd

、v

s1

、v

s2

、v

bsk1

、v

bsk2

对应连接,

……

,第l二级运算电路的端子o

bres

、o

bstd

、o

bs1

、o

bs2

、o

bsel1

、o

bsel2

与矩阵乘法运算电路的端子v

res

、v

bstd

、v

s1

、v

s2

、v

bsl1

、v

bsl2

对应连接。

[0027]

矩阵运算结果存储模块的端子c

d1

与第1采样延时电路的端子d

out

连接,

……

,矩阵运算结果存储模块的端子c

di

与第i采样延时电路的端子d

out

连接,

……

,矩阵运算结果存储模块的端子c

dm

与第m采样延时电路的端子d

out

连接;矩阵运算结果存储模块的端子c

w1

与第31阻值调节电路的端子w

out

连接,

……

,矩阵运算结果存储模块的端子c

wk

与第3k阻值调节电路的端子w

out

连接,

……

,矩阵运算结果存储模块的端子c

wl

与第3l阻值调节电路的端子w

out

连接;矩阵运算结果存储模块的端子c

s1

与矩阵乘法运算电路的端子v

cs1

连接,矩阵运算结果存储模块的端子c

s2

与矩阵乘法运算电路的端子v

s2

连接,矩阵运算结果存储模块的端子c

res

与矩阵乘法运算电路的端子v

res

连接。

[0028]

矩阵电阻的端子r1与gnd连接;矩阵开关电路的端子s0与矩阵乘法运算电路的端子v

s0

连接,矩阵开关电路的端子sel与矩阵乘法运算电路的端子v

clk1

连接。

[0029]

所述矩阵乘法运算电路中的m个采样延时电路相同;每个采样延时电路包括第1运算放大器、采样延时nmos管、第2运算放大器、采样延时pmos管、第3运算放大器、第2采样延时电阻、第1采样延时电阻、第2电容和第1电容。

[0030]

第1运算放大器的端子f

+

与采样延时电路的端子d

in

连接,第1运算放大器的端子fo分别与采样延时nmos管的漏极和第1运算放大器的端子f-连接;采样延时nmos管的栅极、采样延时pmos管的栅极与采样延时电路的端子clk分别连接,采样延时nmos管的源极分别与第1电容的端子c0和第2运算放大器的端子f

+

连接;第2运算放大器的端子fo分别与采样延时pmos管的源极和第2运算放大器的端子f-连接;采样延时pmos管的漏极分别与第2电容的端子c0、采样延时电路的端子dn和第3运算放大器的端子f

+

连接;第3运算放大器的端子f-分别与第1采样延时电阻的端子r0和第2采样延时电阻的端子r0连接,第3运算放大器的端子fo分别与第2采样延时电阻的端子r1和采样延时电路的端子d

out

连接;第1电容的端子c1、第2电容的端子c1和第1采样延时电阻的端子r1与gnd分别连接。

[0031]

所述矩阵乘法运算电路中的2n+l个阻值调节电路相同;每个阻值调节电路包括第1计数器、d触发器、第4运算放大器、阻值调节nmos管、阻值调节pmos管、阻值调节逻辑非门、第2计数器和模数转换器。

[0032]

第1计数器的端子clk、第2计数器的端子clk、模数转换器的端子clk分别与阻值调节电路的端子clk连接,第1计数器的端子max/min与第1计数器的端子cten、d触发器的端子clk和第2计数器的端子load分别连接,第1计数器的端子load与第2计数器的端子d/u、d触发器的端子d、阻值调节电路的端子w0分别连接,第1计数器的端子d/u、a0、

……

、ai、

……

、a7分别与gnd连接;d触发器的端子q

+

与第4运算放大器的端子f-连接,d触发器的端子q-与第2计数器的端子cten连接,d触发器的端子r与阻值调节逻辑非门的端子n

out

连接;第4运算放大器的端子fo与第4运算放大器的端子f

+

和阻值调节nmos管的漏极分别连接;阻值调节nmos管的源极与阻值调节pmos管的源极和阻值调节电路的端子w

out

分别连接,阻值调节nmos管的栅极与阻值调节pmos管的栅极和阻值调节电路的端子w1分别连接;阻值调节pmos管的漏极与gnd连接;阻值调节逻辑非门的端子n

in

与第2计数器的端子max/min连接;第2计数器的端子a0、

……

、ai、

……

、a7与模数转换器的端子d0、

……

、di、

……

、d7对应连接;模数转换器的端子v

adin

与阻值调节电路的端子w

in

连接,模数转换器的端子v

adref

与阻值调节电路的端子w

ref

连接。

[0033]

所述矩阵乘法运算电路中的矩阵元素存储模块包括2

×

m个元素存储nmos管、m+1个元素存储选通器、2

×

n个存储开关电路、元素存储逻辑非门和m

×

n个元素存储忆阻器。

[0034]

第11元素存储nmos管的栅极、

……

、第1i元素存储nmos管的栅极、

……

、第1m元素存储nmos管的栅极与矩阵元素存储模块的端子a

d1

、

……

、a

di

、

……

、a

dm

对应连接,第11元素存储nmos管的漏极、

……

、第1i元素存储nmos管的漏极、

……

、第1m元素存储nmos管的漏极分别与矩阵元素存储模块的端子a1连接,第11元素存储nmos管的源极、

……

、第1i元素存储nmos管的源极、

……

、第1m元素存储nmos管的源极与第11元素存储选通器的端子0_chan、

……

、第1i元素存储选通器的端子0_chan、

……

、第1m元素存储选通器的端子0_chan对应连接。

[0035]

第21元素存储nmos管的栅极、

……

、2i元素存储nmos管的栅极、

……

、2m元素存储nmos管的栅极与矩阵元素存储模块的端子a

ws1

、

……

、a

wsi

、

……

、a

wsm

对应连接,第21元素存储nmos管的源极、

……

、2i元素存储nmos管的源极、

……

、2m元素存储nmos管的源极分别与第2元素存储选通器的端子out连接,第21元素存储nmos管的漏极、

……

、2i元素存储nmos管的漏极、

……

、2m元素存储nmos管的漏极与第11元素存储选通器的端子1_chan、

……

、第1i元素存储选通器的端子1_chan、

……

、第1m元素存储选通器的端子1_chan对应连接。

[0036]

第11元素存储选通器的端子sel、

……

、第1i元素存储选通器的端子sel、

……

、第1m元素存储选通器的端子sel、第11存储开关电路的端子sel、

……

、第1j存储开关电路的端子sel、

……

、第1n存储开关电路的端子sel、元素存储逻辑非门的端子n

in

分别与矩阵元素存储模块的端子a

s1

连接;第1行的n个元素存储忆阻器的端子r

m1

分别与第11元素存储选通器的端子out连接,

……

,第i行的n个元素存储忆阻器的端子r

m1

分别与第1i元素存储选通器的端子out连接,

……

,第m行的n个元素存储忆阻器的端子r

m1

分别与第1m元素存储选通器的端子out连接。

[0037]

第2元素存储选通器的端子1_chan与gnd连接,第2元素存储选通器的端子0_chan

与矩阵元素存储模块的端子a

res

连接,第2元素存储选通器的端子sel与矩阵元素存储模块的端子a

s2

连接。

[0038]

第11存储开关电路的端子s1、

……

、第1j存储开关电路的端子s1、

……

、第1n存储开关电路的端子s1与矩阵元素存储模块的端子a

w1

、

……

、a

wj

、

……

、a

wn

对应连接,第21存储开关电路的端子s0、

……

、第2j存储开关电路的端子s0、

……

、第2n存储开关电路的端子s0与矩阵元素存储模块的端子a

out1

、

……

、a

outj

、

……

、a

outn

对应连接,第21存储开关电路的端子sel、

……

、第2j存储开关电路的端子sel、

……

、第2n存储开关电路的端子sel分别与元素存储逻辑非门的端子n

out

连接。

[0039]

第1列的m个元素存储忆阻器的端子r

m0

分别与第11存储开关电路的端子s0连接,第1列的m个元素存储忆阻器的端子r

m0

分别与第21存储开关电路的端子s1连接,

……

,第j列的m个元素存储忆阻器的端子r

m0

分别与第1j存储开关电路的端子s0连接,第j列的m个元素存储忆阻器的端子r

m0

分别与第2j存储开关电路的端子s1连接,

……

,第n列的m个元素存储忆阻器的端子r

m0

分别与第1n存储开关电路的端子s0连接,第n列的m个元素存储忆阻器的端子r

m0

分别与第2n存储开关电路的端子s1连接。

[0040]

所述矩阵乘法运算电路中的n个一级运算电路相同;每个一级运算电路包括第1一级运算电阻、第2一级运算电阻、第4一级运算电阻、第6运算放大器、第6一级运算电阻、第3一级运算电阻、第5运算放大器和第5一级运算电阻。

[0041]

第5运算放大器的端子f-与一级运算电路的端子o

ain

和第1一级运算电阻的端子r0分别连接,第5运算放大器的端子f

+

与第5一级运算电阻的端子r0连接,第5运算放大器的端子fo与第1一级运算电阻的端子r1和第3一级运算电阻的端子r0分别连接;第2一级运算电阻的端子r0与一级运算电路的端子o

astd

连接,第2一级运算电阻的端子r1与第3一级运算电阻的端子r1、第4一级运算电阻的端子r0和第6运算放大器的端子f-分别连接;第6运算放大器的端子f

+

与第6一级运算电阻的端子r0连接,第6运算放大器的端子fo与第4一级运算电阻的端子r1和一级运算电路的端子o

aout

分别连接;第5一级运算电阻的端子r1和第6一级运算电阻的端子r1分别与gnd连接。

[0042]

所述矩阵乘法运算电路中的矩阵元素存储及运算模块包括2

×

n个运算开关电路、运算逻辑非门和n

×

l

×

2个运算忆阻器。

[0043]

第1行的2

×

l个运算忆阻器的端子r

m0

分别与第11运算开关电路的端子s1连接,

……

,第j行的2

×

l个运算忆阻器的端子r

m0

分别与第1j运算开关电路的端子s1连接,

……

,第n行的2

×

l个运算忆阻器的端子r

m0

分别与第1n运算开关电路的端子s1连接。

[0044]

第1行的2

×

l个运算忆阻器的端子r

m0

分别与第21运算开关电路的端子s0连接,

……

,第j行的2

×

l个运算忆阻器的端子r

m0

分别与第2j运算开关电路的端子s0连接,

……

,第n行的2

×

l个运算忆阻器的端子r

m0

分别与第2n运算开关电路的端子s0连接。

[0045]

第11运算开关电路的端子s0与矩阵元素存储及运算模块的端子b

in1

连接,

……

,第1j运算开关电路的端子s0与矩阵元素存储及运算模块的端子b

inj

连接,

……

,第1n运算开关电路的端子s0与矩阵元素存储及运算模块的端子b

inn

连接,第11运算开关电路的端子sel、

……

、第1j运算开关电路的端子sel、

……

、第1n运算开关电路的端子sel分别与运算逻辑非门的端子n

out

连接。

[0046]

第21运算开关电路的端子s1与矩阵元素存储及运算模块的端子b

w1

连接,

……

,第

2j运算开关电路的端子s1与矩阵元素存储及运算模块的端子b

wj

连接,

……

,第2n运算开关电路的端子s1与矩阵元素存储及运算模块的端子b

wn

连接,第21运算开关电路的端子sel、

……

、第2j运算开关电路的端子sel、

……

、第2n运算开关电路的端子sel分别与运算逻辑非门的端子n

in

连接,第21运算开关电路的端子sel、

……

、第2j运算开关电路的端子sel、

……

、第2n运算开关电路的端子sel分别与矩阵元素存储及运算模块的端子b

s1

连接。

[0047]

第1列的n个运算忆阻器的端子r

m1

分别与矩阵元素存储及运算模块的端子b

out11

连接,第2列的n个运算忆阻器的端子r

m1

分别与矩阵元素存储及运算模块的端子b

out12

连接,

……

,第2

×

k-1列的n个运算忆阻器的端子r

m1

分别与矩阵元素存储及运算模块的端子b

outk1

连接,第2

×

k列的n个运算忆阻器的端子r

m1

分别与矩阵元素存储及运算模块的端子b

outk2

连接,

……

,第2

×

l-1列的n个运算忆阻器的端子r

m1

分别与矩阵元素存储及运算模块的端子b

outl1

连接,第2

×

l列的n个运算忆阻器的端子r

m1

分别与矩阵元素存储及运算模块的端子b

outl2

连接。

[0048]

所述矩阵乘法运算电路中的l个二级运算电路相同;每个二级运算电路包括二级运算选通器a、二级运算nmos管a、第1二级运算电阻、第7运算放大器、第2二级运算电阻、第4二级运算电阻、第3二级运算电阻、第8二级运算电阻、第10二级运算电阻、第10运算放大器、第11二级运算电阻、第9二级运算电阻、第9运算放大器、第7二级运算电阻、第6二级运算电阻、第8运算放大器、第5二级运算电阻、二级运算选通器c、第12二级运算电阻、二级运算nmos管b和二级运算选通器b。

[0049]

二级运算选通器a的端子out与二级运算电路的端子o

bin1

连接,二级运算选通器a的端子1_chan与二级运算nmos管a的漏极连接,二级运算选通器a的端子0_chan与第7运算放大器的端子f-和第2二级运算电阻的端子r0分别连接,二级运算选通器a的端子sel与二级运算选通器b的端子sel和二级运算电路的端子o

bs1

分别连接。

[0050]

二级运算nmos管a的栅极与二级运算电路的端子o

bsel1

连接,二级运算nmos管a的源极与二级运算nmos管b的源极和二级运算选通器c的端子out分别连接。

[0051]

第1二级运算电阻的端子r1、第8二级运算电阻的端子r1、第11二级运算电阻的端子r1、第5二级运算电阻的端子r1、二级运算选通器c的端子1_chan分别与gnd连接。

[0052]

第7运算放大器的端子f

+

与第1二级运算电阻的端子r0连接,第7运算放大器的端子fo与第2二级运算电阻的端子r1和第3二级运算电阻的端子r0分别连接。

[0053]

第10运算放大器的端子f

+

与第11二级运算电阻的端子r0连接,第10运算放大器的端子f-与第3二级运算电阻的端子r1、第10二级运算电阻的端子r0和第9二级运算电阻的端子r0分别连接,第10运算放大器的端子fo与第10二级运算电阻的端子r1和二级运算电路的端子o

bout

分别连接。

[0054]

第9运算放大器的端子f

+

与第8二级运算电阻的端子r0连接,第9运算放大器的端子f-与第6二级运算电阻的端子r1、第12二级运算电阻的端子r1和第7二级运算电阻的端子r0分别连接,第9运算放大器的端子fo与第7二级运算电阻的端子r1和第9二级运算电阻的端子r1分别连接;第12二级运算电阻的端子r0与二级运算电路的端子b

std

连接。

[0055]

第8运算放大器的端子f

+

与第5二级运算电阻的端子r0连接,第8运算放大器的端子f-与第4二级运算电阻的端子r0和二级运算选通器b的端子0_chan分别连接,第8运算放大器的端子fo与第4二级运算电阻的端子r1和第6二级运算电阻的端子r0分别连接。

[0056]

二级运算选通器c的端子sel与二级运算电路的端子o

bs2

连接,二级运算选通器c的端子0_chan与二级运算电路的端子b

res

连接。

[0057]

二级运算选通器b的端子out与二级运算电路的端子o

bin2

连接,二级运算选通器b的端子1_chan与二级运算nmos管b的漏极连接,二级运算nmos管b的栅极与二级运算电路的端子o

bsel2

连接。

[0058]

所述矩阵乘法运算电路中的矩阵运算结果存储模块包括m

×

l个结果存储忆阻器、m

×

l个结果存储nmos管、m个结果开关电路、结果存储逻辑非门和结果存储选通器。

[0059]

第1列的m个结果存储忆阻器的端子r

m0

分别与矩阵运算结果存储模块的端子c

w1

连接,

……

,第k列的m个结果存储忆阻器的端子r

m0

分别与矩阵运算结果存储模块的端子c

wk

连接,

……

,第l列的m个结果存储忆阻器的端子r

m0

分别与矩阵运算结果存储模块的端子c

wl

连接;第1列的m个结果存储忆阻器的端子r

m1

与各自对应的结果存储nmos管的漏极连接,

……

,第k列的m个结果存储忆阻器的端子r

m1

与各自对应的结果存储nmos管的漏极连接,

……

,第l列的m个结果存储忆阻器的端子r

m1

与各自对应的结果存储nmos管的漏极连接。

[0060]m×

l个结果存储nmos管的源极分别与结果存储选通器的端子out连接,第1行的l个结果存储nmos管的栅极分别与矩阵运算结果存储模块的端子c

d1

连接,

……

,第i行的l个结果存储nmos管的栅极分别与矩阵运算结果存储模块的端子c

di

连接,

……

,第m行的l个结果存储nmos管的栅极分别与矩阵运算结果存储模块的端子c

dm

连接;第1行的l个结果存储nmos管的栅极分别与第1结果开关电路的端子s0连接,

……

,第i行的l个结果存储nmos管的栅极分别与第i结果开关电路的端子s0连接,

……

,第m行的l个结果存储nmos管的栅极分别与第m结果开关电路的端子s0连接。

[0061]

第1结果开关电路的端子s1、

……

、第i结果开关电路的端子s1、

……

、第m结果开关电路的端子s1分别与矩阵运算结果存储模块的端子c

s1

连接,第1结果开关电路的端子sel、

……

、第i结果开关电路的端子sel、

……

、第m结果开关电路的端子sel分别与结果存储逻辑非门的端子n

out

连接。

[0062]

结果存储逻辑非门的端子n

in

与结果存储选通器的端子sel和矩阵运算结果存储模块的端子c

s2

分别连接;结果存储选通器的端子1_chan与gnd连接,结果存储选通器的端子0_chan与矩阵运算结果存储模块的端子c

res

连接。

[0063]

所述矩阵乘法运算电路中的矩阵开关电路包括矩阵开关nmos管a和矩阵开关nmos管b。

[0064]

矩阵开关nmos管a的漏极与矩阵开关电路的端子s0连接,矩阵开关nmos管a的源极与矩阵开关nmos管b的源极连接,矩阵开关nmos管a的栅极与矩阵开关电路的端子sel和矩阵开关nmos管b的栅极分别连接;矩阵开关nmos管b的漏极与矩阵开关电路的端子s1连接。

[0065]

所述矩阵元素存储模块中的2n个存储开关电路、矩阵元素存储及运算模块中的2n个运算开关电路和矩阵运算结果存储模块中的m个结果开关电路均与基于忆阻器阵列的矩阵乘法运算电路中的矩阵开关电路相同。

[0066]

所述第1运算放大器为通用型、高速型、低功耗型运算放大器中的任意一种;所述第1运算放大器、第2运算放大器、第3运算放大器、第4运算放大器、第5运算放大器、第6运算放大器、第7运算放大器、第8运算放大器、第9运算放大器和第10运算放大器相同。

[0067]

所述矩阵元素存储模块中的m

×

n个元素存储忆阻器、矩阵元素存储及运算模块中

的n

×

l

×

2个运算忆阻器和矩阵运算结果存储模块中的m

×

l个结果存储忆阻器相同;所述矩阵元素存储模块中的m

×

n个元素存储忆阻器、矩阵元素存储及运算模块中的n

×

l

×

2个运算忆阻器和矩阵运算结果存储模块中的m

×

l个结果存储忆阻器均为具有阈值电压的忆阻器。

[0068]

所述第2一级运算电阻、第3一级运算电阻、第4一级运算电阻的阻值相同。

[0069]

所述第2二级运算电阻和第4二级运算电阻的阻值相同。

[0070]

一种基于忆阻器阵列的矩阵乘法运算电路的使用方法,所述使用方法的步骤如下:

[0071]

步骤一、所有忆阻器复位

[0072]

在矩阵乘法运算电路的端子v

w1

、v

s2

与端子gnd之间施加对应的低电平电压信号u

w1

、u

s2

,在矩阵乘法运算电路的端子v

s1

、v

res

、v

aws1

、

……

、v

awsi

、

……

、v

awsm

、v

bs11

、v

bs12

、

……

、v

bsk1

、v

bsk2

、

……

、v

bsl1

、v

bsl2

、v

cs1

与端子gnd之间施加对应的高电平电压信号u

s1

、u

res

、u

aws1

、

……

、u

awsi

、

……

、u

awsm

、u

bs11

、u

bs12

、

……

、u

bsk1

、u

bsk2

、

……

、u

bsl1

、u

bsl2

、u

cs1

。

[0073]

步骤二、写数据到矩阵元素存储模块

[0074]

在矩阵乘法运算电路的端子v

w0

、v

w1

、v

s1

、v

s2

与端子gnd之间施加对应的高电平电压信号u

w0

、u

w1

、u

s1

、u

s2

;在矩阵乘法运算电路的端子u

wref

与端子gnd之间施加参考电压信号u

wref

;在矩阵乘法运算电路的端子v

clk2

与端子gnd之间施加时钟电压信号u

clk2

;在矩阵乘法运算电路的端子v

aws1

、

……

、v

awsi

、

……

、v

awsm

与端子gnd之间施加对应的高电平电压信号u

aws1

、

……

、u

awsi

、

……

、u

awsm

,在矩阵乘法运算电路的端子v

wa1

、

……

、v

waj

、

……

、v

wan

与端子gnd之间施加对应的阻值调节电压信号u

wa1

、

……

、u

waj

、

……

、u

wan

。

[0075]

步骤三、写数据到矩阵元素存储及运算模块

[0076]

在矩阵乘法运算电路的端子v

w0

、v

w1

、v

s1

、v

s2

与端子gnd之间施加对应的高电平电压信号u

w0

、u

w1

、u

s1

、u

s2

,在矩阵乘法运算电路的端子v

wref

与端子gnd之间施加参考电压信号u

wref

,在矩阵乘法运算电路的端子v

clk2

与端子gnd之间施加时钟电压信号u

cllk2

;在矩阵乘法运算电路的端子v

bs11

、v

bs12

、

……

、v

bsk1

、v

bsk2

、

……

、v

bsl1

、v

bsl2

与端子gnd之间依次施加对应的高电平电压信号u

bs11

、u

bs12

、

……

、u

bsk1

、u

bsk2

、

……

、u

bsl1

、u

bsl2

,同时在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

。

[0077]

步骤四、执行矩阵乘法运算

[0078]

在矩阵乘法运算电路的端子v

s1

与端子gnd之间施加低电平电压信号u

s1

;在矩阵乘法运算电路的端子v

s2

、v

s0

、v

w1

与端子gnd之间施加对应的高电平电压信号u

s2

、u

s0

、u

w1

;在矩阵乘法运算电路的端子u

wref

与端子gnd之间施加参考电压信号u

wref

;在矩阵乘法运算电路的端子v

a1

、v

astd

、v

bstd

与端子gnd之间施加对应的运算电压信号u

a1

、u

astd

、u

bstd

;在矩阵乘法运算电路的端子v

clk1

、v

clk2

与端子gnd之间施加对应的时钟电压信号u

clk1

、u

clk2

;在矩阵乘法运算电路的端子v

din

与端子gnd之间施加脉冲电压信号u

din

。

[0079]

由于采用上述技术方案,本发明具有如下积极效果:

[0080]

本发明中,当只需输入相应的电压信号就能够对各忆阻器阵列进行复位操作,能将所述矩阵乘法运算电路中的所有忆阻器均调节为高阻状态;当只需输入矩阵元素对应大小的电压到阻值调节电路中,并配合相应的高电平电压控制信号,就能将所要计算矩阵中

的元素保存到忆阻器阵列中,因此本发明操作简单。

[0081]

本发明中,采样延时电路所输出的高电平电压信号能使矩阵元素存储模块和矩阵运算结果存储模块中的各行元素存储忆阻器依次被选中,进而使得矩阵元素存储模块分别输出被选中行元素存储忆阻器的电导所对应的电压,而矩阵元素存储模块输出的电压分别施加到矩阵元素存储及运算模块中的忆阻器阵列各行后,矩阵元素存储及运算模块输出对应的向量与矩阵相乘结果的电压,该电压则通过阻值调节电路保存到矩阵运算结果存储模块的忆阻器阵列中所被选中行的元素存储忆阻器内,计算过程中省去了存储器和运算器之间进行数据传输的过程,数据的存储和运算都在忆阻器阵列中完成,从而提高了矩阵乘法运算的速度。

[0082]

本发明在矩阵元素存储及运算模块中以两个忆阻器电导的差值表示对应的一个矩阵元素,进而使矩阵元素存储及运算模块中忆阻器的电导所表示数值的范围从正数扩展到正、负数和零,故能够矩阵对任意二个包含正数和负数元素的实数矩阵进行矩阵乘法运算。

[0083]

因此,本发明不仅操作简单、运算速度快,且能够对任意二个包含正数和负数元素的实数矩阵进行矩阵乘法运算。

附图说明

[0084]

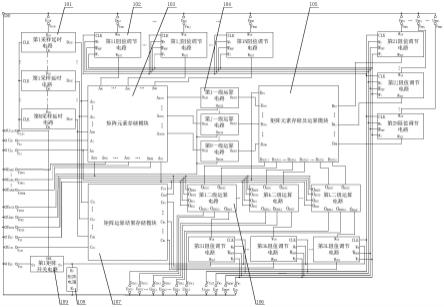

图1为本发明的一种结构示意图;

[0085]

图2为图1中采样延时电路101的一种结构示意图;

[0086]

图3为图1中阻值调节电路102的一种结构示意图;

[0087]

图4为图1中矩阵元素存储模块103的一种结构示意图;

[0088]

图5为图1中一级运算电路104的一种结构示意图;

[0089]

图6为图1中矩阵元素存储及运算模块105的一种结构示意图;

[0090]

图7为图1中二级运算电路106的一种结构示意图;

[0091]

图8为图1中矩阵运算结果存储模块107的一种结构示意图;

[0092]

图9为图1中开关电路109的一种结构示意图。

具体实施方式

[0093]

下面结合附图和具体实施方式对本发明作进一步描述,并非对其保护范围的限制。

[0094]

实施例1

[0095]

一种基于忆阻器阵列的矩阵乘法运算电路及其使用方法。所述基于忆阻器阵列的矩阵乘法运算电路简称为矩阵乘法运算电路。

[0096]

如图1所示,所述矩阵乘法运算电路包括m个采样延时电路101、2n+l个阻值调节电路102、矩阵元素存储模块103、n个一级运算电路104、矩阵元素存储及运算模块105、l个二级运算电路106、矩阵运算结果存储模块107、矩阵电阻108和矩阵开关电路109。

[0097]

所述矩阵乘法运算电路中:

[0098]

如图1所示,第1采样延时电路101的端子clk、

……

、第i采样延时电路101的端子clk、

……

、第m采样延时电路101的端子clk与矩阵乘法运算电路的端子v

clk1

分别连接;第1

采样延时电路101的端子dn与第2采样延时电路101的端子d

in

连接,

……

,第i-1采样延时电路101的端子dn与第i采样延时电路101的端子d

in

连接,

……

,第m-1采样延时电路101的端子dn与第m采样延时电路101的端子d

in

连接;第1采样延时电路101的端子d

in

与矩阵乘法运算电路的端子v

din

连接。

[0099]

如图1所示,第11阻值调节电路102的端子clk、

……

、第1j阻值调节电路102的端子clk、

……

、第1n阻值调节电路102的端子clk、第21阻值调节电路102的端子clk、

……

、第2j阻值调节电路102的端子clk、

……

、第2n阻值调节电路102的端子clk、第31阻值调节电路102的端子clk、

……

、第3k阻值调节电路102的端子clk、

……

、第3l阻值调节电路102的端子clk与矩阵乘法运算电路的端子v

clk2

分别连接。

[0100]

如图1所示,第11阻值调节电路102的端子w0、

……

、第1j阻值调节电路102的端子w0、

……

、第1n阻值调节电路102的端子w0、第21阻值调节电路102的端子w0、

……

、第2j阻值调节电路102的端子w0、

……

、第2n阻值调节电路102的端子w0与矩阵乘法运算电路的端子v

w0

分别连接;第31阻值调节电路102的端子w0、

……

、第3k阻值调节电路102的端子w0、

……

、第3l阻值调节电路102的端子w0与矩阵开关电路109的端子s1分别连接,第31阻值调节电路102的端子w0、

……

、第3k阻值调节电路102的端子w0、

……

、第3l阻值调节电路102的端子w0与矩阵电阻108的端子r0分别连接。

[0101]

如图1所示,第11阻值调节电路102的端子w

ref

、

……

、第1j阻值调节电路102的端子w

ref

、

……

、第1n阻值调节电路102的端子w

ref

、第21阻值调节电路102的端子w

ref

、

……

、第2j阻值调节电路102的端子w

ref

、

……

、第2n阻值调节电路102的端子w

ref

、第31阻值调节电路102的端子w

ref

、

……

、第3k阻值调节电路102的端子w

ref

……

、第3l阻值调节电路102的端子w

ref

与矩阵乘法运算电路的端子v

wref

分别连接。

[0102]

如图1所示,第11阻值调节电路102的端子w1、

……

、第1j阻值调节电路102的端子w1、

……

、第1n阻值调节电路102的端子w1、第21阻值调节电路102的端子w1、

……

、第2j阻值调节电路102的端子w1、

……

、第2n阻值调节电路102的端子w1、第31阻值调节电路102的端子w1、

……

、第3k阻值调节电路102的端子w1……

、第3l阻值调节电路102的端子w1与矩阵乘法运算电路的端子v

w1

分别连接。

[0103]

如图1所示,第11阻值调节电路102的端子w

in

与矩阵乘法运算电路的端子v

wa1

连接,

……

,第1j阻值调节电路102的端子w

in

与矩阵乘法运算电路的端子v

waj

连接,

……

,第1n阻值调节电路102的端子w

in

与矩阵乘法运算电路的端子v

wan

连接;第21阻值调节电路102的端子w

in

与矩阵乘法运算电路的端子v

wb1

连接,

……

,第2j阻值调节电路102的端子w

in

与矩阵乘法运算电路的端子v

wbj

连接,

……

,第2n阻值调节电路102的端子w

in

与矩阵乘法运算电路的端子v

wbn

连接;第31阻值调节电路102的端子w

in

与第1二级运算电路106的端子o

bout

连接,

……

,第3k阻值调节电路102的端子w

in

与第k二级运算电路106的端子o

bout

连接,

……

,第3l阻值调节电路102中的端子w

in

与第l二级运算电路106的端子o

bout

连接。

[0104]

如图1所示,矩阵元素存储模块103的端子a

w1

与第11阻值调节电路102的端子w

out

连接,

……

,矩阵元素存储模块103的端子a

wj

与第1j阻值调节电路102的端子w

out

连接,

……

,矩阵元素存储模块103的端子a

wn

与第1n阻值调节电路102的端子w

out

连接;矩阵元素存储模块103的端子a

d1

与第1采样延时电路101的端子d

out

连接,

……

,矩阵元素存储模块103的端子a

di

与第i采样延时电路101的端子d

out

连接,

……

,矩阵元素存储模块103的端子a

dm

与第m采

样延时电路101的端子d

out

连接;矩阵元素存储模块103的端子a

out1

与第1一级运算电路104的端子o

ain

连接,

……

,矩阵元素存储模块103的端子a

outj

与第j一级运算电路104的端子o

ain

连接,

……

,矩阵元素存储模块103的端子a

outn

与第n一级运算电路104的端子o

ain

连接;矩阵元素存储模块103的端子a

ws1

、

……

、a

wsi

、

……

、a

wsm

与矩阵乘法运算电路的端子v

aws1

、

……

、v

awsi

、

……

、v

awsm

对应连接;矩阵元素存储模块103的端子a1、a

s1

、a

res

、a

s2

与矩阵乘法运算电路的端子v

a1

、v

s1

、v

res

、v

s2

对应连接。

[0105]

如图1所示,第1一级运算电路104的端子o

astd

、

……

、第j一级运算电路104的端子o

astd

、

……

、第n一级运算电路104的端子o

astd

分别与矩阵乘法运算电路的端子v

astd

连接;第1一级运算电路104的端子o

aout

与矩阵元素存储及运算模块105的端子b

in1

连接,

……

,第j一级运算电路104的端子o

aout

与矩阵元素存储及运算模块105的端子b

inj

连接、

……

、第n一级运算电路104的端子o

aout

与矩阵元素存储及运算模块105的端子b

inn

连接。

[0106]

如图1所示,矩阵元素存储及运算模块105的端子b

w1

与第21阻值调节电路102的端子w

out

连接,

……

,矩阵元素存储及运算模块105的端子b

wj

与第2j阻值调节电路102的端子w

out

连接,

……

,矩阵元素存储及运算模块105的端子b

wn

与第2n阻值调节电路102的端子w

out

连接;矩阵元素存储及运算模块105的端子b

out11

、b

out12

与第1二级运算电路106的端子o

bin1

、o

bin2

对应连接,

……

,矩阵元素存储及运算模块105的端子b

outk1

、b

outk2

与第k二级运算电路106的端子o

bin1

、o

bin2

对应连接,

……

,矩阵元素存储及运算模块105的端子b

outl1

、b

outl2

与第l二级运算电路106的端子o

bin1

、o

bin2

连接;矩阵元素存储及运算模块105的端子b

s1

与矩阵乘法运算电路的端子v

s1

对应连接。

[0107]

如图1所示,第1二级运算电路106的端子o

bres

、o

bstd

、o

bs1

、o

bs2

、o

bsel1

、o

bsel2

与矩阵乘法运算电路的端子v

res

、v

bstd

、v

s1

、v

s2

、v

bs11

、v

bs12

对应连接,

……

,第k二级运算电路106的端子o

bres

、o

bstd

、o

bs1

、o

bs2

、o

bsel1

、o

bsel2

与矩阵乘法运算电路的端子v

res

、v

bstd

、v

s1

、v

s2

、v

bsk1

、v

bsk2

对应连接,

……

,第l二级运算电路106的端子o

bres

、o

bstd

、o

bs1

、o

bs2

、o

bsel1

、o

bsel2

与矩阵乘法运算电路的端子v

res

、v

bstd

、v

s1

、v

s2

、v

bsl1

、v

bsl2

对应连接。

[0108]

如图1所示,矩阵运算结果存储模块107的端子c

d1

与第1采样延时电路101的端子d

out

连接,

……

,矩阵运算结果存储模块107的端子c

di

与第i采样延时电路101的端子d

out

连接,

……

,矩阵运算结果存储模块107的端子c

dm

与第m采样延时电路101的端子d

out

连接;矩阵运算结果存储模块107的端子c

w1

与第31阻值调节电路102的端子w

out

连接,

……

,矩阵运算结果存储模块107的端子c

wk

与第3k阻值调节电路102的端子w

out

连接,

……

,矩阵运算结果存储模块107的端子c

wl

与第3l阻值调节电路102的端子w

out

连接;矩阵运算结果存储模块107的端子c

s1

与矩阵乘法运算电路的端子v

cs1

连接,矩阵运算结果存储模块107的端子c

s2

与矩阵乘法运算电路的端子v

s2

连接,矩阵运算结果存储模块107的端子c

res

与矩阵乘法运算电路的端子v

res

连接。

[0109]

如图1所示,矩阵电阻108的端子r1与gnd连接;矩阵开关电路109的端子s0与矩阵乘法运算电路的端子v

s0

连接,矩阵开关电路109的端子sel与矩阵乘法运算电路的端子v

clk1

连接。

[0110]

如图2所示,矩阵乘法运算电路中所述m个采样延时电路101相同;每个采样延时电路101包括第1运算放大器201、采样延时nmos管202、第2运算放大器203、采样延时pmos管204、第3运算放大器205、第2采样延时电阻206、第1采样延时电阻207、第2电容208和第1电

容209。

[0111]

如图2所示,第1运算放大器201的端子f

+

与采样延时电路101的端子d

in

连接,第1运算放大器201的端子fo分别与采样延时nmos管202的漏极和第1运算放大器201的端子f-连接;采样延时nmos管202的栅极、采样延时pmos管204的栅极与采样延时电路101的端子clk分别连接,采样延时nmos管202的源极分别与第1电容209的端子c0和第2运算放大器203的端子f

+

连接;第2运算放大器203的端子fo分别与采样延时pmos管204的源极和第2运算放大器203的端子f-连接;采样延时pmos管204的漏极分别与第2电容208的端子c0、采样延时电路101的端子dn和第3运算放大器205的端子f

+

连接;第3运算放大器205的端子f-分别与第1采样延时电阻207的端子r0和第2采样延时电阻206的端子r0连接,第3运算放大器205的端子fo分别与第2采样延时电阻206的端子r1和采样延时电路101的端子d

out

连接;第1电容209的端子c1、第2电容208的端子c1和第1采样延时电阻207的端子r1与gnd分别连接。

[0112]

如图3所示,矩阵乘法运算电路中所述2n+l个阻值调节电路102相同;每个阻值调节电路102包括第1计数器301、d触发器302、第4运算放大器303、阻值调节nmos管304、阻值调节pmos管305、阻值调节逻辑非门306、第2计数器307和模数转换器308。

[0113]

如图3所示,第1计数器301的端子clk、第2计数器307的端子clk、模数转换器308的端子clk分别与阻值调节电路102的端子clk连接,第1计数器301的端子max/min与第1计数器301的端子cten、d触发器302的端子clk和第2计数器307的端子load分别连接,第1计数器301的端子load与第2计数器307的端子d/u、d触发器302的端子d、阻值调节电路102的端子w0分别连接,第1计数器301的端子d/u、a0、

……

、ai、

……

、a7分别与gnd连接;d触发器302的端子q

+

与第4运算放大器303的端子f-连接,d触发器302的端子q-与第2计数器307的端子cten连接,d触发器302的端子r与阻值调节逻辑非门306的端子n

out

连接;第4运算放大器303的端子fo与第4运算放大器303的端子f

+

和阻值调节nmos管304的漏极分别连接;阻值调节nmos管304的源极与阻值调节pmos管305的源极和阻值调节电路102的端子w

out

分别连接,阻值调节nmos管304的栅极与阻值调节pmos管305的栅极和阻值调节电路102的端子w1分别连接;阻值调节pmos管305的漏极与gnd连接;阻值调节逻辑非门306的端子n

in

与第2计数器307的端子max/min连接;第2计数器307的端子a0、

……

、ai、

……

、a7与模数转换器308的端子d0、

……

、di、

……

、d7对应连接;模数转换器308的端子v

adin

与阻值调节电路102的端子w

in

连接,模数转换器308的端子v

adref

与阻值调节电路102的端子w

ref

连接。

[0114]

如图4所示,矩阵乘法运算电路中所述矩阵元素存储模块103包括2

×

m个元素存储nmos管401、m+1个元素存储选通器402、2

×

n个存储开关电路403、元素存储逻辑非门404和m

×

n个元素存储忆阻器405。

[0115]

如图4所示,第11元素存储nmos管401的栅极、

……

、第1i元素存储nmos管401的栅极、

……

、第1m元素存储nmos管401的栅极与矩阵元素存储模块103的端子a

d1

、

……

、a

di

、

……

、a

dm

对应连接,第11元素存储nmos管401的漏极、

……

、第1i元素存储nmos管401的漏极、

……

、第1m元素存储nmos管401的漏极分别与矩阵元素存储模块103的端子a1连接,第11元素存储nmos管401的源极、

……

、第1i元素存储nmos管401的源极、

……

、第1m元素存储nmos管401的源极与第11元素存储选通器402的端子0_chan、

……

、第1i元素存储选通器402的端子0_chan、

……

、第1m元素存储选通器402的端子0_chan对应连接。

[0116]

如图4所示,第21元素存储nmos管401的栅极、

……

、2i元素存储nmos管401的栅

极、

……

、2m元素存储nmos管401的栅极与矩阵元素存储模块103的端子a

ws1

、

……

、a

wsi

、

……

、a

wsm

对应连接,第21元素存储nmos管401的源极、

……

、2i元素存储nmos管401的源极、

……

、2m元素存储nmos管401的源极分别与第2元素存储选通器402的端子out连接,第21元素存储nmos管401的漏极、

……

、2i元素存储nmos管401的漏极、

……

、2m元素存储nmos管401的漏极与第11元素存储选通器402的端子1_chan、

……

、第1i元素存储选通器402的端子1_chan、

……

、第1m元素存储选通器402的端子1_chan对应连接。

[0117]

如图4所示,第11元素存储选通器402的端子sel、

……

、第1i元素存储选通器402的端子sel、

……

、第1m元素存储选通器402的端子sel、第11存储开关电路403的端子sel、

……

、第1j存储开关电路403的端子sel、

……

、第1n存储开关电路403的端子sel、元素存储逻辑非门404的端子n

in

分别与矩阵元素存储模块103的端子a

s1

连接;第1行的n个元素存储忆阻器405的端子r

m1

分别与第11元素存储选通器402的端子out连接,

……

,第i行的n个元素存储忆阻器405的端子r

m1

分别与第1i元素存储选通器402的端子out连接,

……

,第m行的n个元素存储忆阻器405的端子r

m1

分别与第1m元素存储选通器402的端子out连接。

[0118]

如图4所示,第2元素存储选通器402的端子1_chan与gnd连接,第2元素存储选通器402的端子0_chan与矩阵元素存储模块103的端子a

res

连接,第2元素存储选通器402的端子sel与矩阵元素存储模块103的端子a

s2

连接。

[0119]

如图4所示,第11存储开关电路403的端子s1、

……

、第1j存储开关电路403的端子s1、

……

、第1n存储开关电路403的端子s1与矩阵元素存储模块103的端子a

w1

、

……

、a

wj

、

……

、a

wn

对应连接,第21存储开关电路403的端子s0、

……

、第2j存储开关电路403的端子s0、

……

、第2n存储开关电路403的端子s0与矩阵元素存储模块103的端子a

out1

、

……

、a

outj

、

……

、a

outn

对应连接,第21存储开关电路403的端子sel、

……

、第2j存储开关电路403的端子sel、

……

、第2n存储开关电路403的端子sel分别与元素存储逻辑非门404的端子n

out

连接。

[0120]

如图4所示,第1列的m个元素存储忆阻器405的端子r

m0

分别与第11存储开关电路403的端子s0连接,第1列的m个元素存储忆阻器405的端子r

m0

分别与第21存储开关电路403的端子s1连接,

……

,第j列的m个元素存储忆阻器405的端子r

m0

分别与第1j存储开关电路403的端子s0连接,第j列的m个元素存储忆阻器405的端子r

m0

分别与第2j存储开关电路403的端子s1连接,

……

,第n列的m个元素存储忆阻器405的端子r

m0

分别与第1n存储开关电路403的端子s0连接,第n列的m个元素存储忆阻器405的端子r

m0

分别与第2n存储开关电路403的端子s1连接。

[0121]

如图5所示,矩阵乘法运算电路中所述n个一级运算电路104相同;每个一级运算电路104包括第1一级运算电阻501、第2一级运算电阻502、第4一级运算电阻503、第6运算放大器504、第6一级运算电阻505、第3一级运算电阻506、第5运算放大器507和第5一级运算电阻508。

[0122]

如图5所示,第5运算放大器507的端子f-与一级运算电路104的端子o

ain

和第1一级运算电阻501的端子r0分别连接,第5运算放大器507的端子f

+

与第5一级运算电阻508的端子r0连接,第5运算放大器507的端子fo与第1一级运算电阻501的端子r1和第3一级运算电阻506的端子r0分别连接;第2一级运算电阻502的端子r0与一级运算电路104的端子o

astd

连接,第2一级运算电阻502的端子r1与第3一级运算电阻506的端子r1、第4一级运算电阻503的端

子r0和第6运算放大器504的端子f-分别连接;第6运算放大器504的端子f

+

与第6一级运算电阻505的端子r0连接,第6运算放大器504的端子fo与第4一级运算电阻503的端子r1和一级运算电路104的端子o

aout

分别连接;第5一级运算电阻508的端子r1和第6一级运算电阻505的端子r1分别与gnd连接。

[0123]

如图6所示,矩阵乘法运算电路中所述矩阵元素存储及运算模块105包括2

×

n个运算开关电路601、运算逻辑非门602和n

×

l

×

2个运算忆阻器603。

[0124]

如图6所示,第1行的2

×

l个运算忆阻器603的端子r

m0

分别与第11运算开关电路601的端子s1连接,

……

,第j行的2

×

l个运算忆阻器603的端子r

m0

分别与第1j运算开关电路601的端子s1连接,

……

,第n行的2

×

l个运算忆阻器603的端子r

m0

分别与第1n运算开关电路601的端子s1连接。

[0125]

如图6所示,第1行的2

×

l个运算忆阻器603的端子r

m0

分别与第21运算开关电路601的端子s0连接,

……

,第j行的2

×

l个运算忆阻器603的端子r

m0

分别与第2j运算开关电路601的端子s0连接,

……

,第n行的2

×

l个运算忆阻器603的端子r

m0

分别与第2n运算开关电路601的端子s0连接。

[0126]

如图6所示,第11运算开关电路601的端子s0与矩阵元素存储及运算模块105的端子b

in1

连接,

……

,第1j运算开关电路601的端子s0与矩阵元素存储及运算模块105的端子b

inj

连接,

……

,第1n运算开关电路601的端子s0与矩阵元素存储及运算模块105的端子b

inn

连接,第11运算开关电路601的端子sel、

……

、第1j运算开关电路601的端子sel、

……

、第1n运算开关电路601的端子sel分别与运算逻辑非门602的端子n

out

连接。

[0127]

如图6所示,第21运算开关电路601的端子s1与矩阵元素存储及运算模块105的端子b

w1

连接,

……

,第2j运算开关电路601的端子s1与矩阵元素存储及运算模块105的端子b

wj

连接,

……

,第2n运算开关电路601的端子s1与矩阵元素存储及运算模块105的端子b

wn

连接,第21运算开关电路601的端子sel、

……

、第2j运算开关电路601的端子sel、

……

、第2n运算开关电路601的端子sel分别与运算逻辑非门602的端子n

in

连接,第21运算开关电路601的端子sel、

……

、第2j运算开关电路601的端子sel、

……

、第2n运算开关电路601的端子sel分别与矩阵元素存储及运算模块105的端子b

s1

连接。

[0128]

如图6所示,第1列的n个运算忆阻器603的端子r

m1

分别与矩阵元素存储及运算模块105的端子b

out11

连接,第2列的n个运算忆阻器603的端子r

m1

分别与矩阵元素存储及运算模块105的端子b

out12

连接,

……

,第2

×

k-1列的n个运算忆阻器603的端子r

m1

分别与矩阵元素存储及运算模块105的端子b

outk1

连接,第2

×

k列的n个运算忆阻器603的端子r

m1

分别与矩阵元素存储及运算模块105的端子b

outk2

连接,

……

,第2

×

l-1列的n个运算忆阻器603的端子r

m1

分别与矩阵元素存储及运算模块105的端子b

outl1

连接,第2

×

l列的n个运算忆阻器603的端子r

m1

分别与矩阵元素存储及运算模块105的端子b

outl2

连接。

[0129]

如图7所示,矩阵乘法运算电路中所述l个二级运算电路106相同;每个二级运算电路106包括二级运算选通器a701、二级运算nmos管a702、第1二级运算电阻703、第7运算放大器704、第2二级运算电阻705、第4二级运算电阻706、第3二级运算电阻707、第8二级运算电阻708、第10二级运算电阻709、第10运算放大器710、第11二级运算电阻711、第9二级运算电阻712、第9运算放大器713、第7二级运算电阻714、第6二级运算电阻715、第8运算放大器716、第5二级运算电阻717、二级运算选通器c718、第12二级运算电阻719、二级运算nmos管

b720和二级运算选通器b721。

[0130]

如图7所示,二级运算选通器a701的端子out与二级运算电路106的端子o

bin1

连接,二级运算选通器a701的端子1_chan与二级运算nmos管a702的漏极连接,二级运算选通器a701的端子0_chan与第7运算放大器704的端子f-和第2二级运算电阻705的端子r0分别连接,二级运算选通器a701的端子sel与二级运算选通器b721的端子sel和二级运算电路106的端子o

bs1

分别连接。

[0131]

如图7所示,二级运算nmos管a702的栅极与二级运算电路106的端子o

bsel1

连接,二级运算nmos管a702的源极与二级运算nmos管b720的源极和二级运算选通器c718的端子out分别连接。

[0132]

如图7所示,第1二级运算电阻703的端子r1、第8二级运算电阻708的端子r1、第11二级运算电阻711的端子r1、第5二级运算电阻717的端子r1、二级运算选通器c718的端子1_chan分别与gnd连接。

[0133]

如图7所示,第7运算放大器704的端子f

+

与第1二级运算电阻703的端子r0连接,第7运算放大器704的端子fo与第2二级运算电阻705的端子r1和第3二级运算电阻707的端子r0分别连接。

[0134]

如图7所示,第10运算放大器710的端子f

+

与第11二级运算电阻711的端子r0连接,第10运算放大器710的端子f-与第3二级运算电阻707的端子r1、第10二级运算电阻709的端子r0和第9二级运算电阻712的端子r0分别连接,第10运算放大器710的端子fo与第10二级运算电阻709的端子r1和二级运算电路106的端子o

bout

分别连接。

[0135]

如图7所示,第9运算放大器713的端子f

+

与第8二级运算电阻708的端子r0连接,第9运算放大器713的端子f-与第6二级运算电阻715的端子r1、第12二级运算电阻719的端子r1和第7二级运算电阻714的端子r0分别连接,第9运算放大器713的端子fo与第7二级运算电阻714的端子r1和第9二级运算电阻712的端子r1分别连接;第12二级运算电阻719的端子r0与二级运算电路106的端子b

std

连接。

[0136]

如图7所示,第8运算放大器716的端子f

+

与第5二级运算电阻717的端子r0连接,第8运算放大器716的端子f-与第4二级运算电阻706的端子r0和二级运算选通器b721的端子0_chan分别连接,第8运算放大器716的端子fo与第4二级运算电阻706的端子r1和第6二级运算电阻715的端子r0分别连接。

[0137]

如图7所示,二级运算选通器c718的端子sel与二级运算电路106的端子o

bs2

连接,二级运算选通器c718的端子0_chan与二级运算电路106的端子b

res

连接。

[0138]

如图7所示,二级运算选通器b721的端子out与二级运算电路106的端子o

bin2

连接,二级运算选通器b721的端子1_chan与二级运算nmos管b720的漏极连接,二级运算nmos管b720的栅极与二级运算电路106的端子o

bsel2

连接。

[0139]

如图8所示,矩阵乘法运算电路中所述矩阵运算结果存储模块107包括m

×

l个结果存储忆阻器801、m

×

l个结果存储nmos管802、m个结果开关电路803、结果存储逻辑非门804和结果存储选通器805。

[0140]

如图8所示,第1列的m个结果存储忆阻器801的端子r

m0

分别与矩阵运算结果存储模块107的端子c

w1

连接,

……

,第k列的m个结果存储忆阻器801的端子r

m0

分别与矩阵运算结果存储模块107的端子c

wk

连接,

……

,第l列的m个结果存储忆阻器801的端子r

m0

分别与矩阵运

算结果存储模块107的端子c

wl

连接;第1列的m个结果存储忆阻器801的端子r

m1

与各自对应的结果存储nmos管802的漏极连接,

……

,第k列的m个结果存储忆阻器801的端子r

m1

与各自对应的结果存储nmos管802的漏极连接,

……

,第l列的m个结果存储忆阻器801的端子r

m1

与各自对应的结果存储nmos管802的漏极连接。

[0141]

如图8所示,m

×

l个结果存储nmos管802的源极分别与结果存储选通器805的端子out连接,第1行的l个结果存储nmos管802的栅极分别与矩阵运算结果存储模块107的端子c

d1

连接,

……

,第i行的l个结果存储nmos管802的栅极分别与矩阵运算结果存储模块107的端子c

di

连接,

……

,第m行的l个结果存储nmos管802的栅极分别与矩阵运算结果存储模块107的端子c

dm

连接;第1行的l个结果存储nmos管802的栅极分别与第1结果开关电路803的端子s0连接,

……

,第i行的l个结果存储nmos管802的栅极分别与第i结果开关电路803的端子s0连接,

……

,第m行的l个结果存储nmos管802的栅极分别与第m结果开关电路803的端子s0连接。

[0142]

如图8所示,第1结果开关电路803的端子s1、

……

、第i结果开关电路803的端子s1、

……

、第m结果开关电路803的端子s1分别与矩阵运算结果存储模块107的端子c

s1

连接,第1结果开关电路803的端子sel、

……

、第i结果开关电路803的端子sel、

……

、第m结果开关电路803的端子sel分别与结果存储逻辑非门804的端子n

out

连接。

[0143]

如图8所示,结果存储逻辑非门804的端子n

in

与结果存储选通器805的端子sel和矩阵运算结果存储模块107的端子c

s2

分别连接;结果存储选通器805的端子1_chan与gnd连接,结果存储选通器805的端子0_chan与矩阵运算结果存储模块107的端子c

res

连接。

[0144]

如图9所示,矩阵乘法运算电路中所述矩阵开关电路109包括矩阵开关nmos管a901和矩阵开关nmos管b902。

[0145]

如图9所示,矩阵开关nmos管a901的漏极与矩阵开关电路109的端子s0连接,矩阵开关nmos管a901的源极与矩阵开关nmos管b902的源极连接,矩阵开关nmos管a901的栅极与矩阵开关电路109的端子sel和矩阵开关nmos管b902的栅极分别连接;矩阵开关nmos管b902的漏极与矩阵开关电路109的端子s1连接。

[0146]

本实施例中:

[0147]

所述矩阵元素存储模块103中的2n个存储开关电路403、矩阵元素存储及运算模块105中的2n个运算开关电路601和矩阵运算结果存储模块107中的m个结果开关电路803均与基于忆阻器阵列的矩阵乘法运算电路中的矩阵开关电路109相同。

[0148]

所述第1运算放大器201为通用型、高速型、低功耗型运算放大器中的任意一种;所述第1运算放大器201与第2运算放大器203、第3运算放大器205、第4运算放大器303、第5运算放大器507、第6运算放大器504、第7运算放大器704、第8运算放大器716、第9运算放大器713和第10运算放大器710相同。

[0149]

所述矩阵元素存储模块103中的m

×

n个元素存储忆阻器405、矩阵元素存储及运算模块105中的n

×

l

×

2个运算忆阻器603和矩阵运算结果存储模块107中的m

×

l个结果存储忆阻器801相同;所述矩阵元素存储模块103中的m

×

n个元素存储忆阻器405、矩阵元素存储及运算模块105中的n

×

l

×

2个运算忆阻器603和矩阵运算结果存储模块107中的m

×

l个结果存储忆阻器801均为具有阈值电压的忆阻器。

[0150]

所述第2一级运算电阻502、第3一级运算电阻506、第4一级运算电阻503的阻值相

同。

[0151]

所述第2二级运算电阻705和第4二级运算电阻706的阻值相同。

[0152]

本实施例中:m、n、l依次为6、6、6。

[0153]

本实施例所述基于忆阻器阵列的矩阵乘法运算电路的使用方法。所述使用方法的步骤如下:

[0154]

步骤一、所有忆阻器复位

[0155]

在矩阵乘法运算电路的端子v

w1

、v

s2

与端子gnd之间施加对应的低电平电压信号u

w1

=0v、u

s2

=0v,在矩阵乘法运算电路的端子v

s1

、v

res

、v

aws1

、

……

、v

awsi

、

……

、v

awsm

、v

bs11

、v

bs12

、

……

、v

bsk1

、v

bsk2

、

……

、v

bsl1

、v

bsl2

、v

cs1

与端子gnd之间施加对应的高电平电压信号u

s1

=5v、u

res

=3.5v、u

aws1

=5v、

……

、u

awsi

=5v、

……

、u

awsm

=5v、u

bs11

=5v、u

bs12

=5v、

……

、u

bsk1

=5v、u

bsk2

=5v、

……

、u

bsl1

=5v、u

bsl2

=5v、u

cs1

=5v。

[0156]

此时,在矩阵乘法运算电路的端子v

res

、v

aws1

、

……

、v

awsi

、

……

、v

awsm

、v

bs11

、v

bs12

、

……

、v

bsk1

、v

bsk2

、

……

、v

bsl1

、v

bsl2

、v

cs1

输入对应的高电平电压信号u

res

、u

aws1

、

……

、u

awsi

、

……

、u

awsm

、u

bs11

、u

bs12

、

……

、u

bsk1

、u

bsk2

、

……

、u

bsl1

、u

bsl2

、u

cs1

,使矩阵元素存储模块103中的第21元素存储nmos管401、

……

、第2i元素存储nmos管401、

……

、第2m元素存储nmos管401、各二级运算电路106中各自的二级运算nmos管a702和二级运算nmos管b720、矩阵运算结果存储模块107中的各行结果存储nmos管802均处于导通状态,高电平电压信号u

res

施加在矩阵元素存储模块103、矩阵元素存储及运算模块105和矩阵运算结果存储模块107中所有忆阻器的端子r

m1

上,高电平电压信号u

res

的值大于元素存储忆阻器405的阈值电压且持续时间超过元素存储忆阻器405复位所需的最大时间t

max

,使得所有的元素存储忆阻器405、运算忆阻器603和结果存储忆阻器801都复位为高阻态。

[0157]

本实施例中所有忆阻器在高阻态的阻值均复位至所设定的5000ω。

[0158]

步骤二、写数据到矩阵元素存储模块

[0159]

在矩阵乘法运算电路的端子v

w0

、v

w1

、v

s1

、v

s2

与端子gnd之间施加对应的高电平电压信号u

w0

=3.5v、u

w1

=5v、u

s1

=5v、u

s2

=3.5v;在矩阵乘法运算电路的端子v

wref

与端子gnd之间施加参考电压信号u

wref

=2.4v;在矩阵乘法运算电路的端子v

clk2

与端子gnd之间施加频率为1000khz的时钟电压信号u

clk2

;在矩阵乘法运算电路的端子v

aws1

与端子gnd之间施加对应的高电平电压信号u

aws1

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

、v

wa4

、v

wa5

、v

wa6

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0.8v、u

wa2

=0.8v、u

wa3

=0.8v、u

wa4

=0.8v、u

wa5

=0.8v、u

wa6

=0.8v,在矩阵乘法运算电路的端子v

aws2

与端子gnd之间施加对应的高电平电压信号u

aws2

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

、v

wa4

、v

wa5

、v

wa6

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0.0449v、u

wa2

=0.2852v、u

wa3

=0.1363v、u

wa4

=0.0311v、u

wa5

=0.0544v、u

wa6

=0.0593v,在矩阵乘法运算电路的端子v

aws3

与端子gnd之间施加对应的高电平电压信号u

aws3

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

、v

wa4

、v

wa5

、v

wa6

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0.322v、u

wa2

=0.1025v、u

wa3

=0.1151v、u

wa4

=0.0402v、u

wa5

=0.0966v、u

wa6

=0.0449v,在矩阵乘法运算电路的端子v

aws4

与端子gnd之间施加对应的高电平电压信号u

aws4

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

、v

wa4

、v

wa5

、v

wa6

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0.0966v、u

wa2

=0.0693v、u

wa3

=0.0852v、u

wa4

=0.0311v、u

wa5

=0.0449v、u

wa6

=0.0132v,在矩阵乘法运算电

路的端子v

was5

与端子gnd之间施加对应的高电平电压信号u

aws5

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

、v

wa4

、v

wa5

、v

wa6

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0v、u

wa2

=0.0966v、u

wa3

=0.0642v、u

wa4

=0.1441v、u

wa5

=0.1815v、u

wa6

=0.171v,在矩阵乘法运算电路的端子v

aws6

与端子gnd之间施加对应的高电平电压信号u

aws6

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

、v

wa4

、v

wa5

、v

wa6

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0.2208v、u

wa2

=0.0449v、u

wa3

=0.0966v、u

wa4

=0.1441v、u

wa5

=0.0176v、u

wa6

=0.0221v。

[0160]

此时,矩阵元素存储模块103中第21元素存储nmos管401处于导通状态,同时第11阻值调节电路102、

……

、第1j阻值调节电路102、

……

、第1n阻值调节电路102分别输出阻值调节电压信号u

wa1

、

……

、u

waj

、

……

、u

wan

的值所对应时长的脉冲电压信号,这些脉冲电压信号使得矩阵元素存储模块103中第1行元素存储忆阻器405的阻值得到调整。所述脉冲电压信号的大小为3.5v,脉冲电压信号的时长为t。

[0161]

所述脉冲电压信号的时长t与阻值调节电压信号u

waj

大小之间的关系为:

[0162][0163]

式(1)中:

[0164]uwaj

表示第1j阻值调节电路102端子w

in

的电压,v;

[0165]vref

表示参考电压u

wref

的值,v;

[0166]

f表示时钟电压信号u

clk2

的时钟频率,hz。

[0167]

按照矩阵元素存储模块103中第1行元素存储忆阻器405阻值的调整方法,对矩阵元素存储模块103中第2行、

……

、第i行、

……

、第m行元素存储忆阻器405依次操作,实现对矩阵元素存储模块103中所有元素存储忆阻器405的阻值进行调整的功能。

[0168]

所述阻值调节过程中各元素存储忆阻器405两端所施加电压的时长t与其阻值大小的对应关系为:

[0169][0170]

式(2)中:

[0171]woff

表示所使用元素存储忆阻器405模型内部状态变量w的最大值,nm;

[0172]koff

表示元素存储忆阻器405材料的常量,m/s;

[0173]vi

表示阻值调节电路102所输出脉冲电压信号的大小,v;

[0174]woff

表示元素存储忆阻器405的阈值电压,v;

[0175]

w表示所使用元素存储忆阻器405模型的状态变量,nm。

[0176]

所使用元素存储忆阻器405模型的状态变量w与元素存储忆阻器405阻值之间的关系为;

[0177][0178]

式(3)中:

[0179]rm

表示元素存储忆阻器405的阻值,ω;

[0180]ron

表示元素存储忆阻器405的最小阻值,ω;

[0181]roff

表示元素存储忆阻器405的最大阻值,ω;

[0182]won

表示所使用元素存储忆阻器405模型状态变量w的最小值,nm;

[0183]woff

表示所使用元素存储忆阻器405模型状态变量w的最大值,nm。

[0184]

本实施例中:w

off

=10nm;w

on

=0nm;k

off

=0.0004m/s;v

off

=1.5v;r

on

=1000ω;r

off

=5000ω。

[0185]

至此,矩阵元素存储模块103中第1行的6个忆阻器的阻值依次被调整为1000ω、1000ω、1000ω、1000ω、1000ω、1000ω,矩阵元素存储模块103中第2行的6个忆阻器的阻值依次被调整为4000ω、1300ω、2400ω、4300ω、3800ω、3700ω,矩阵元素存储模块103中第3行的6个忆阻器的阻值依次被调整为1200ω、2900ω、2700ω、4100ω、3000ω、4000ω,矩阵元素存储模块103中第4行的6个忆阻器的阻值依次被调整为3000ω、3500ω、3200ω、4300ω、4000ω、4700ω,矩阵元素存储模块103中第5行的6个忆阻器的阻值依次被调整为5000ω、3000ω、3600ω、2300ω、1900ω、2000ω,矩阵元素存储模块103中第6行的6个忆阻器的阻值依次被调整为1600ω、4000ω、3000ω、2300ω、4600ω、4500ω。

[0186]

步骤三、写数据到矩阵元素存储及运算模块

[0187]

在矩阵乘法运算电路的端子v

w0

、v

w1

、v

s1

、v

s2

与端子gnd之间施加对应的高电平电压信号u

w0

=3.5v、u

w1

=5v、u

s1

=5v、u

s2

=3.5v,在矩阵乘法运算电路的端子v

wref

与端子gnd之间施加参考电压信号u

wref

=2.4v,在矩阵乘法运算电路的端子v

clk2

与端子gnd之间施加频率为1000khz的时钟电压信号u

clk2

。

[0188]

在矩阵乘法运算电路的端子v

bs11

与端子gnd之间施加高电平电压信号u

bs11

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

,在矩阵乘法运算电路的端子v

bs12

与端子gnd之间施加高电平电压信号u

bs12

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.322v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

。

[0189]

在矩阵乘法运算电路的端子v

bs21

与端子gnd之间施加高电平电压信号u

bs21

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.238v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

,在矩阵乘法运算电路的端子v

bs22

与端子gnd之间施加高电平电压信号u

bs22

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

。

[0190]

在矩阵乘法运算电路的端子v

bs31

与端子gnd之间施加高电平电压信号u

bs31

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.0852v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

,在矩阵乘法运算电路的端子v

bs32

与端子gnd之间施加高电平电压信号u

bs32

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.238v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

。

[0191]

在矩阵乘法运算电路的端子v

bs41

与端子gnd之间施加高电平电压信号u

bs41

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.1289v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

,在矩阵乘法运算电路的端子v

bs42

与端子gnd之间施加高电平电压信号u

bs42

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.0221v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

。

[0192]

在矩阵乘法运算电路的端子v

bs51

与端子gnd之间施加高电平电压信号u

bs51

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.0449v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

,在矩阵乘法运算电路的端子v

bs52

与端子gnd之间施加高电平电压信号u

bs52

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.238v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

。

[0193]

在矩阵乘法运算电路的端子v

bs61

与端子gnd之间施加高电平电压信号u

bs61

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.1614v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

,在矩阵乘法运算电路的端子v

bs62

与端子gnd之间施加高电平电压信号u

bs62

=5v,在矩阵乘法运算电路的端子v

wb1

、

……

、v

wbj

、

……

、v

wbn

与端子gnd之间分别施加电压均为0.0221v的阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

。

[0194]

此时,第1二级运算电路106中的二级运算nmos管a702处于导通状态,第21阻值调节电路102、

……

、第2j阻值调节电路102、

……

、第2n阻值调节电路102分别完成与步骤二中的阻值调节电路102相同的运算,并依次输出阻值调节电压信号u

wb1

、

……

、u

wbj

、

……

、u

wbn

的电压所对应时长的脉冲电压信号,所述脉冲电压信号使得矩阵元素存储及运算模块105中第1列运算忆阻器603的阻值得到调整。

[0195]

相应地,第1二级运算电路106中的二级运算nmos管b720处于导通状态,第21阻值调节电路102、

……

、第2j阻值调节电路102、

……

、第2n阻值调节电路102所输出的对应时长的脉冲电压信号使得矩阵元素存储及运算模块105中第2列运算忆阻器603的阻值得到调整。

[0196]

按照矩阵元素存储及运算模块105中第1列运算忆阻器603和第1列运算忆阻器603阻值的调整方法,对矩阵元素存储及运算模块105中第3列、第4列、

……

、第2

×

k-1列、第2

×

k列、

……

、第2

×

l-1列、第2

×

l列运算忆阻器603依次操作,实现对矩阵元素存储及运算模块105中所有运算忆阻器603的阻值进行调整的功能。

[0197]

步骤三中,以矩阵元素存储及运算模块105第1列中各运算忆阻器603电导和第2列中对应运算忆阻器603电导之差值表示矩阵第1列中对应元素的值,

……

,同理,第2

×

l-1列中各运算忆阻器603电导和第2

×

l列中对应运算忆阻器603电导之差值表示矩阵第l列中对应元素的值。

[0198]

矩阵元素存储及运算模块105中第j行第2

×

k-1列运算忆阻器603的电导和第j行第2

×

k列运算忆阻器603的电导所表示的矩阵元素b

jk

:

[0199][0200]

式(4)中:

[0201]rmj2

×

k-1

表示矩阵元素存储及运算模块105中第j行第2

×

k-1列运算忆阻器603的阻值,ω;

[0202]rmj2

×k表示矩阵元素存储及运算模块105中第j行第2

×

k列运算忆阻器603的阻值,ω。

[0203]

式4中,当r

mj2

×

k-1

等于r

mj2

×k时,矩阵元素b

jk

为0;当r

mj2

×

k-1

大于r

mj2

×k时,矩阵元素bjk

为负数;当r

mj2

×

k-1

小于r

mj2

×k时,矩阵元素b

jk

为正数。

[0204]

至此,矩阵元素存储及运算模块105:第1列的6个忆阻器的阻值均被调整为5000ω;第2列的6个忆阻器的阻值均被调整为1200ω;第3列的6个忆阻器的阻值均被调整为1500ω;第4列的6个忆阻器的阻值均被调整为5000ω;第5列的6个忆阻器的阻值均被调整为3200ω;第6列的6个忆阻器的阻值均被调整为1500ω;第7列的6个忆阻器的阻值均被调整为2500ω;第8列的6个忆阻器的阻值均被调整为4500ω;第9列的6个忆阻器的阻值均被调整为4000ω;第10列的6个忆阻器的阻值均被调整为1500ω;第11列的6个忆阻器的阻值均被调整为2100ω;第12列的6个忆阻器的阻值均被调整为4500ω。

[0205]

步骤四、执行矩阵乘法运算

[0206]

在矩阵乘法运算电路的端子v

s1

与端子gnd之间施加低电平电压信号u

s1

=0v;在矩阵乘法运算电路的端子v

s2

、v

s0

、v

w1

与端子gnd之间施加对应的高电平电压信号u

s2

=3.5v、u

s0

=3.5v、u

w1

=5v;在矩阵乘法运算电路的端子v

wref

与端子gnd之间施加参考电压信号u

wref

=2.4v;在矩阵乘法运算电路的端子v

a1

、v

astd

、v

bstd

与端子gnd之间施加对应的运算电压信号u

a1

=1v、u

astd

=0.5v、u

bstd

=4.8v;在矩阵乘法运算电路的端子v

clk1

、v

clk2

与端子gnd之间施加对应的时钟电压信号u

clk1

、u

clk2

,其中时钟电压信号u

clk1

的时钟周期为500hz,时钟电压信号u

clk2

的时钟周期为1000khz;在矩阵乘法运算电路的端子v

din

与端子gnd之间施加时长为1ms的脉冲电压信号u

din

=0.5v。

[0207]

本实施例中:第2一级运算电阻502、第3一级运算电阻506、第4一级运算电阻503阻值均为1000ω;第7二级运算电阻714、第6二级运算电阻715、第12二级运算电阻719的阻值均为1000ω。

[0208]

当矩阵乘法运算电路的端子v

clk1

输入的时钟电压信号u

clk1

第1次为高电平时,所有采样延时电路101中的采样延时nmos管202均处于导通状态,采样延时pmos管204均处于截止状态,此时从矩阵乘法运算电路的端子v

din

施加的脉冲电压u

din

使得第1采样延时电路101中的第1电容209开始充电;当矩阵乘法运算电路的端子v

clk1

输入的时钟电压信号u

clk1

第1次为低电平时,所有采样延时电路101中的采样延时nmos管202均处于截止状态,采样延时pmos管204均处于导通状态,此时第1采样延时电路101中的第1电容209开始放电,使得第1采样延时电路101的端子d

out

和dn输出高电平,同时第1采样延时电路101中的第2电容208开始充电。

[0209]

当矩阵乘法运算电路的端子v

clk1

输入的时钟电压信号u

clk1

第2次为高电平时,所有采样延时电路101中的采样延时nmos管202均处于导通状态,采样延时pmos管204均处于截止状态,此时第1采样延时电路101中的第2电容208开始放电,使得第1采样延时电路101的端子d

out

和dn继续输出高电平,同时采样延时电路101的端子dn输出的高电平电压信号使得第2采样延时电路101中的第1电容209开始充电。

[0210]

重复本步骤上述过程,并在矩阵乘法运算电路的端子v

a1

、v

astd

、v

bstd

与端子gnd之间分别施加运算电压信号u

a1

、u

astd

、u

bstd

。在矩阵乘法运算电路的端子v

clk1

输入时钟电压信号u

clk1

期间,第1采样延时电路101、

……

、第i采样延时电路101、

……

、第m采样延时电路101的端子d

out

依次输出高电平电压信号。

[0211]

当第1采样延时电路101的端子d

out

输出高电平电压信号时,第11元素存储nmos管401和第1行结果存储nmos管802均处于导通状态,使第1行元素存储忆阻器405端子r

m1

处的

电压为运算电压信号u

a1

的值,第1一级运算电路104、

……

、第j一级运算电路104、

……

、第n一级运算电路104端子o

aout

输出的电压依次为v

aout1

、

……

、v

aoutj

、

……

、v

aoutn

;其中:

[0212]

第1一级运算电路104端子o

aout

输出的电压v

aout1

:

[0213][0214]

式(5)中:

[0215]r11

表示第1一级运算电路104中第1一级运算电阻501的阻值,r

11

=1500ω;

[0216]rm11

表示矩阵元素存储模块103中第1行1列元素存储忆阻器405的阻值,r

m11

=1000ω;

[0217]ua1

表示从矩阵乘法运算电路的端子v

a1

所施加电压,u

a1

=1v;

[0218]uastd

表示从矩阵乘法运算电路的端子v

astd

所施加电压,u

astd

=0.5v。

[0219]

则,第1一级运算电路104端子o

aout

输出的电压v

aout1

=1v。

[0220]

同理:第2一级运算电路104、

……

、第j一级运算电路104、

……

、第n一级运算电路104中端子o

aout

依次输出的电压为1v、1v、1v、1v、1v。

[0221]

从矩阵乘法运算电路的端子v

astd

施加运算电压信号u

astd

后,第1一级运算电路104、

……

、第j一级运算电路104、

……

、第n一级运算电路104端子o

aout

的输出电压变为矩阵元素存储模块103的输出电压与运算电压信号u

astd

的电压之差,将矩阵元素存储模块103中各元素存储忆阻器405的电导所表示的包含正、负数的矩阵元素转变为对应的正、负电压。其中,所施加的运算电压信号u

astd

:

[0222][0223]

式(6)中:

[0224]r11

表示第1一级运算电阻501的阻值,r

11

=1500ω;

[0225]ron

表示元素存储忆阻器405的最小阻值,r

on

=1000ω;

[0226]roff

表示元素存储忆阻器405的最大阻值,r

off

=5000ω;

[0227]ua1

表示从矩阵乘法运算电路的端子v

a1

所施加电压,u

a1

=1v。

[0228]

则,所施加的运算电压信号u

astd

=0.5v。

[0229]

由于n个一级运算电路104的输出端o

aout

同时分别输出电压v

aout1

、

……

、v

aoutj

、

……

、v

aoutn

后,l个二级运算电路106的输出端o

bout

同时分别输出电压v

bout1

、

……

、v

boutk

、

……

、v

boutl

。其中,

[0230]

第1二级运算电路106的输出端o

bout

的输出电压v

bout1

:

[0231][0232]

式(7)中:

[0233]r22

表示第2二级运算电阻705的阻值,r

22

=1000ω;

[0234]r23

表示第3二级运算电阻707的阻值,r

23

=9600ω;

[0235]r24

表示第4二级运算电阻706的阻值,r

24

=1000ω;

[0236]r29

表示第9二级运算电阻712的阻值,r

29

=9600ω;

[0237]r210

表示第10二级运算电阻709的阻值,r

210

=800ω;

[0238]

n表示一级运算电路104的个数,n=6;

[0239]rm11

、r

m12

、

……

、r

mj1

、r

mj2

、

……

、r

mn1

、r

mn2

依次表示矩阵元素存储及运算模块105中第1行第1列、第1行第2列、

……

、第j行第1列、第j行第2列、

……

、第n行第1列、第n行第2列忆阻器的阻值,r

m11

、r

m12

、

……

、r

mj1

、r

mj2

、

……

、r

mn1

、r

mn2

的阻值依次为5000ω、1200ω、5000ω、1200ω、5000ω、1200ω、5000ω、1200ω、5000ω、1200ω、5000ω、1200ω;

[0240]ubstd

表示从矩阵乘法运算电路的端子v

bstd

所施加的运算电压信号,u

bstd

=4.8v。则,所施加的运算电压信号v

bout1

=0.0833v。

[0241]

由于所有二级运算电路106都可以输出正、负数运算结果所对应的双极性电压,故从矩阵乘法运算电路的端子v

bstd

施加一个正电压u

bstd

使得二级运算电路106的所有输出电压都为正值,以便于将矩阵乘法运算的结果保存到矩阵运算结果存储模块107中。

[0242]

其中,所施加的运算电压信号u

bstd

:

[0243][0244]

式(8)中:

[0245]r11

表示第1一级运算电阻501的阻值,r

11

=1500ω;

[0246]r24

表示第4二级运算电阻706的阻值,r

24

=1000ω;

[0247]

n表示一级运算电路106的个数,n=6;

[0248]ron

表示元素存储忆阻器405的最小阻值,r

on

=1000ω;

[0249]roff

表示元素存储忆阻器405的最大阻值,r

off

=5000ω;

[0250]ua1

表示从矩阵乘法运算电路的端子v

a1

所施加电压,u

a1

=1v;

[0251]uastd

表示从矩阵乘法运算电路的端子v

astd

所施加电压,u

astd

=0.5v。

[0252]

则,所施加的运算电压信号u

bstd

=4.8v。

[0253]

同理:第2二级运算电路104、

……

、第k二级运算电路104、

……

、第l二级运算电路104中端子o

bout

依次输出的电压为0.633v、0.223v、0.489v、0.192v、0.527v。

[0254]

第31阻值调节电路102、

……

、第3k阻值调节电路102、

……

、第3l阻值调节电路102依次输出v

bout1

、

……

、v

boutk

、

……

、v

boutl

对应时长的脉冲电压信号,此时矩阵运算结果存储模块107中第1行的结果存储nmos管802均处于导通状态,使矩阵运算结果存储模块107中第1行结果存储忆阻器801的阻值按照第1二级运算电路106、

……

、第k二级运算电路106、

……

、第l二级运算电路106对应输出的电压v

bout1

、

……

、v

boutk

、

……

、v

boutl

同时被调整。

[0255]

同理,重复本步骤上述过程直至第m采样延时电路101的端子d

out

输出高电平电压信号后,本实施例的矩阵乘法运算结束,矩阵运算结果存储模块107中保存了矩阵乘法运算的结果:

[0256]

第1行的第1列、

……

、第k列、

……

、第l列结果存储忆阻器801的阻值依次为3234ω、1006ω、1587ω、1031ω、1812ω、1020ω;

[0257]

第2行的第1列、

……

、第k列、

……

、第l列结果存储忆阻器801的阻值依次为1100ω、1073ω、1092ω、1079ω、1094ω、1078ω;

[0258]

第3行的第1列、

……

、第k列、

……

、第l列结果存储忆阻器801的阻值依次为1117

ω、1065ω、1101ω、1076ω、1104ω、1073ω;

[0259]

第4行的第1列、

……

、第k列、

……

、第l列结果存储忆阻器801的阻值依次为1060ω、1107ω、1069ω、1092ω、1067ω、1096ω;

[0260]

第5行的第1列、

……

、第k列、

……

、第l列结果存储忆阻器801的阻值依次为1107ω、1070ω、1096ω、1078ω、1098ω、1076ω;

[0261]

第6行的第1列、

……

、第k列、

……

、第l列结果存储忆阻器801的阻值依次为1090ω、1079ω、1087ω、1082ω、1088ω、1081ω。

[0262]

实施例2

[0263]

一种基于忆阻器阵列的矩阵乘法运算电路及其使用方法。所述基于忆阻器阵列的矩阵乘法运算电路简称为矩阵乘法运算电路。

[0264]

本实施例所述矩阵乘法运算电路除m、n、l依次为2、3、2外,其余同实施例1所述矩阵乘法运算电路。

[0265]

本实施例所述基于忆阻器阵列的矩阵乘法运算电路的使用方法。所述使用方法的步骤如下:

[0266]

步骤一、所有忆阻器复位

[0267]

在矩阵乘法运算电路的端子v

w1

、v

s2

与端子gnd之间施加对应的低电平电压信号u

w1

=0v、u

s2

=0v,在矩阵乘法运算电路的端子v

s1

、v

res

、v

aws1

、

……

、v

awsi

、

……

、v

awsm

、v

bs11

、v

bs12

、

……

、v

bsk1

、v

bsk2

、

……

、v

bsl1

、v

bsl2

、v

cs1

与端子gnd之间施加对应的高电平电压信号u

s1

=5v、u

res

=3.5v、u

aws1

=5v、

……

、u

awsi

=5v、

……

、u

awsm

=5v、u

bs11

=5v、u

bs12

=5v、

……

、u

bsk1

=5v、u

bsk2

=5v、

……

、u

bsl1

=5v、u

bsl2

=5v、u

cs1

=5v。

[0268]

至此,所有的元素存储忆阻器405、运算忆阻器603和结果存储忆阻器801都复位为高阻态。本实施例中所有忆阻器在高阻态的阻值均复位至所设定的5000ω。

[0269]

步骤二、写数据到矩阵元素存储模块

[0270]

在矩阵乘法运算电路的端子v

w0

、v

w1

、v

s1

、v

s2

与端子gnd之间施加对应的高电平电压信号u

w0

=3.5v、u

w1

=5v、u

s1

=5v、u

s2

=3.5v;在矩阵乘法运算电路的端子v

wref

与端子gnd之间施加参考电压信号u

wref

=2.4v;在矩阵乘法运算电路的端子v

clk2

与端子gnd之间施加频率为1000khz的时钟电压信号u

clk2

;在矩阵乘法运算电路的端子v

aws1

与端子gnd之间施加对应的高电平电压信号u

aws1

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0.8v、u

wa2

=0.0966v、u

wa3

=0v,在矩阵乘法运算电路的端子v

aws2

与端子gnd之间施加对应的高电平电压信号u

aws2

=5v,在矩阵乘法运算电路的端子v

wa1

、v

wa2

、v

wa3

与端子gnd之间施加对应的阻值调节电压信号u

wa1

=0.171v、u

wa2

=0.0221v、u

wa3

=0.0693v。

[0271]

至此,矩阵元素存储模块103:第1行的3个忆阻器的阻值依次被调整为1000ω、3000ω、5000ω;第2行的3个忆阻器的阻值依次被调整为2000ω、4500ω、3500ω。

[0272]

步骤三、写数据到矩阵元素存储及运算模块

[0273]

在矩阵乘法运算电路的端子v

w0

、v

w1

、v

s1

、v

s2

与端子gnd之间施加对应的高电平电压信号u

w0

=3.5v、u

w1

=5v、u

s1

=5v、u

s2

=3.5v,在矩阵乘法运算电路的端子v

wref

与端子gnd之间施加参考电压信号u

wref

=2.4v,在矩阵乘法运算电路的端子v

clk2

与端子gnd之间施加频率为1000khz的时钟电压信号u

clk2

。

[0274]

在矩阵乘法运算电路的端子v

bs11

与端子gnd之间施加高电平电压信号u

bs11

=5v,在矩阵乘法运算电路的端子v

wb1

、v

wb2

、v

wb3

与端子gnd之间分别施加对应的阻值调节电压信号u

wb1

=0.171v、u

wb2

=0.238v、u

wb3

=0.0798v,在矩阵乘法运算电路的端子v

bs12

与端子gnd之间施加高电平电压信号u

bs12

=5v,在矩阵乘法运算电路的端子v

wb1

、v

wb2

、v

wb3

与端子gnd之间分别施加对应的阻值调节电压信号u

wb1

=0.1151v、u

wb2

=0.0449v、u

wb3

=0.322v。

[0275]

在矩阵乘法运算电路的端子v

bs21

与端子gnd之间施加高电平电压信号u

bs21

=5v,在矩阵乘法运算电路的端子v

wb1

、v

wb2

、v

wb3

与端子gnd之间分别施加对应的阻值调节电压信号u

wb1

=0.0642v、u

wb2

=0.1289v、u

wb3

=0v,在矩阵乘法运算电路的端子v

bs22

与端子gnd之间施加高电平电压信号u

bs22

=5v,在矩阵乘法运算电路的端子v

wb1

、v

wb2

、v

wb3

与端子gnd之间分别施加对应的阻值调节电压信号u

wb1

=0.8v、u

wb2

=0.0544v、u

wb3

=0.0221v。

[0276]

至此,矩阵元素存储及运算模块105:第1列的3个忆阻器的阻值依次被调整为2000ω、1500ω、3300ω;第2列的3个忆阻器的阻值依次被调整为2700ω、4000ω、1200ω;第3列的3个忆阻器的阻值依次被调整为3600ω、2500ω、5000ω;第4列的3个忆阻器的阻值依次被调整为1000ω、3800ω、4500ω。

[0277]

步骤四、执行矩阵乘法运算

[0278]

在矩阵乘法运算电路的端子v

s1

与端子gnd之间施加低电平电压信号u

s1

=0v;在矩阵乘法运算电路的端子v

s2

、v

s0

、v

w1

与端子gnd之间施加对应的高电平电压信号u

s2

=3.5v、u

s0

=3.5v、u

w1

=5v;在矩阵乘法运算电路的端子v

wref

与端子gnd之间施加参考电压信号u

wref

=2.4v;在矩阵乘法运算电路的端子v

a1

、v

astd

、v

bstd

与端子gnd之间施加对应的运算电压信号u

a1

=1v、u

astd

=0.5v、u

bstd

=2.4v;在矩阵乘法运算电路的端子v

clk1

、v

clk2

与端子gnd之间施加对应的时钟电压信号u

clk1

、u

clk2

,其中时钟电压信号u

clk1

的时钟周期为500hz,时钟电压信号u

clk2

的时钟周期为1000khz;在矩阵乘法运算电路的端子v

din

与端子gnd之间施加时长为1ms的脉冲电压信号u

din

=0.5v。

[0279]

至此,矩阵运算结果存储模块107:第1行结果存储忆阻器801的阻值依次被调节为1067ω,2350ω;矩阵运算结果存储模块107中第2行结果存储忆阻器801的阻值依次被调节为1745ω,1885ω。

[0280]

本具体实施方式具有如下积极效果:

[0281]

本具体实施方式中,当只需输入相应的电压信号就能够对各忆阻器阵列进行复位操作,能将所述矩阵乘法运算电路中的所有忆阻器均调节为高阻状态;当只需输入矩阵元素对应大小的电压到阻值调节电路102中,并配合相应的高电平电压控制信号,就能将所要计算矩阵中的元素保存到忆阻器阵列中,因此本具体实施方式操作简单。

[0282]

本具体实施方式中,采样延时电路101所输出的高电平电压信号能使矩阵元素存储模块103和矩阵运算结果存储模块107中的各行元素存储忆阻器405依次被选中,进而使得矩阵元素存储模块103分别输出被选中行元素存储忆阻器405的电导所对应的电压,而矩阵元素存储模块103输出的电压分别施加到矩阵元素存储及运算模块105中的忆阻器阵列各行后,矩阵元素存储及运算模块105输出对应的向量与矩阵相乘结果的电压,该电压则通过阻值调节电路102保存到矩阵运算结果存储模块107的忆阻器阵列中所被选中行的元素存储忆阻器405内,计算过程中省去了存储器和运算器之间进行数据传输的过程,数据的存储和运算都在忆阻器阵列中完成,从而提高了矩阵乘法运算的速度。

[0283]

本具体实施方式在矩阵元素存储及运算模块105中以两个忆阻器电导的差值表示对应的一个矩阵元素,进而使矩阵元素存储及运算模块105中忆阻器的电导所表示数值的范围从正数扩展到正、负数和零,故能够矩阵对任意二个包含正数和负数元素的实数矩阵进行矩阵乘法运算。

[0284]

因此,本具体实施方式不仅操作简单、运算速度快,且能够对任意二个包含正数和负数元素的实数矩阵进行矩阵乘法运算。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1