输出测试结果的存储器件及测试其的方法与流程

发明构思的各种示例实施例涉及半导体器件,并且更具体地,涉及存储器件、包括该存储器件的系统、测试存储器件的方法和/或一种非暂时性计算机可读介质,该非暂时性计算机可读介质包括用于测试存储器件并且将通过使用低性能测试设备执行的封装测试的结果输出到该低性能测试设备以降低成本的计算机可读指令。

背景技术:

1、半导体芯片通过半导体制造工艺来制造并且由测试设备在半导体晶片、裸片或封装件的状态下测试。通过测试(例如,缺陷测试等)选择和/或标识缺陷或有缺陷的芯片,并且,当一些存储单元被标识为是有缺陷的时,执行修复操作以挽救和/或修复半导体芯片。随着像动态随机存取存储器(dram)一样的半导体芯片持续小型化,在半导体制造工艺期间更有可能发生错误。另外,即使在初始测试(例如,在制造阶段期间执行的测试)期间未检测到错误,在芯片工作期间也可能发生错误。

2、由于对大量数据的稳定快速的实时处理的需求不断增加,对高容量dram的需求也在增加。然而,dram的性能质量会随着时间的推移而改变。存储器系统可以预期dram的可靠性、可用性和可维护性(ras)能力。因此,dram可以包括对存储单元阵列(mca)执行测试操作和/或修复操作的内置自测试(bist)电路。该bist电路是提供用于检测mca中的有缺陷的单元的测试模式的测试模式生成(tpg)电路,并且内置自修复(bisr)电路包括控制将mca中的有缺陷的存储单元修复为冗余存储单元的内置冗余分析(bira)电路等。由于这样的bist电路具有复杂的硬件配置并且占据dram芯片很大的物理面积,所以一些dram可能不提供这种能力。

3、另一方面,测试dram的工艺可以包括如下测试:测试晶片状态的芯片的电裸片分选(eds)测试,在eds测试中被确定为好的芯片通过组装工艺封装之后执行的封装测试,在好的封装后的芯片被安装在模块上之后执行的模块测试,以及在好的模块被安装在板上之后执行的安装测试。存储器芯片是否通过测试是根据每个测试阶段是否存在缺陷来确定的。在一般测试方法中,为了保证好的产品,各个阶段的通过测试的样品被处理直到最后的模块/安装测试,最后通过测试的样品被处理为好的产品,而各个阶段的有缺陷的样品被处理为有故障的产品。

4、用于eds测试的测试设备可以包括昂贵的高性能测试设备以最初确定存储单元是否有故障,并且确定是否可以修复故障。用于封装测试的测试设备可以执行封装后的dram芯片的dc参数测试、动态功能测试、器件分选验证测试和/或低功率测试,并且与用于eds测试的测试设备相比,可以包括相对和/或有时便宜的低性能测试设备。当封装测试未通过时,可以对对应的dram芯片执行封装后修复(ppr)。当dram芯片在ppr之后有故障时,可以将该dram芯片处理为有缺陷的产品。

5、当不包括bist电路的dram芯片在使用低性能测试设备执行的封装测试中的ppr之后不合格并且仍然可修复时,可以提高生产率。

技术实现思路

1、发明构思的各种示例实施例提供一种存储器件、一种包括该存储器件的系统、一种包括用于执行测试存储器件的方法的计算机可读指令的非暂时性计算机可读介质、和/或一种测试存储器件以便将修复操作的测试结果输出到测试装置来提高生产率的方法。

2、根据发明构思的至少一个示例实施例,提供了一种存储器件,所述存储器件包括:存储单元阵列,所述存储单元阵列包括多个存储单元和多个冗余存储单元,所述多个存储单元布置在多个行和多个列的交叉点处,所述多个冗余存储单元被配置为修复所述多个存储单元当中的故障存储单元;以及修复电路,所述修复电路被配置为:对所述多个存储单元当中的第一故障存储单元执行修复操作,并且向位于所述存储器件外部的外部目的地输出脏信号,所述修复操作包括:选择所述多个冗余存储单元的第一冗余地址而不是所述第一故障存储单元的第一故障地址,存储所述第一故障地址到所述第一冗余地址的第一冗余映射,以及,响应于确定出所述多个存储单元当中的第二故障存储单元的第二故障地址与所述第一故障地址匹配,忽略所述第一冗余映射,并且其中,所述脏信号对应于所述第一故障地址并且引起要所述第一故障地址映射到所述冗余存储单元的与所述第一冗余地址不同的第二冗余地址的第二冗余映射。

3、根据发明构思的至少一个示例实施例,提供了一种存储器件,所述存储器件包括:存储单元阵列,所述存储单元阵列包括多个存储单元和多个冗余存储单元,所述多个存储单元布置在多个行和多个列的交叉点处,所述多个冗余存储单元被配置为修复所述多个存储单元当中的故障存储单元;以及修复电路,所述修复电路被配置为:对所述多个存储单元当中的第一故障存储单元执行修复操作,并且向位于所述存储器件外部的外部目的地输出溢出标志信号,所述修复操作包括:选择所述冗余存储单元的第一冗余地址而不是所述第一故障存储单元的第一故障地址,以及存储所述第一故障地址到所述第一冗余地址的第一冗余映射,其中所述溢出标志信号指示了用于存储所述多个存储单元当中的第二故障存储单元的第二故障地址到第二冗余地址的第二冗余映射的存储空间不足。

4、根据发明构思的至少一个示例实施例,提供了一种存储器件,所述存储器件包括:存储单元阵列,所述存储单元阵列包括多个存储单元和多个冗余存储单元,所述多个存储单元布置在多个行和多个列的交叉点处,所述多个冗余存储单元被配置为修复所述多个存储单元当中的故障存储单元;以及修复电路,所述修复电路被配置为,在对所述故障存储单元执行修复操作之后对所述存储单元阵列执行存储器测试操作,并且向位于所述存储器件外部的外部目的地输出第一信号,所述第一信号是作为所述存储器测试操作的结果而获得的并且指示被修复的冗余存储单元的故障。

5、根据发明构思的至少一个示例实施例,提供了一种测试存储器件的方法,所述存储器件包括多个存储单元和多个冗余存储单元,所述方法包括:对所述多个存储单元当中的第一故障存储单元执行第一修复操作,所述第一修复操作包括选择所述冗余存储单元的第一冗余地址而不是所述第一故障存储单元的第一故障地址;根据所述第一修复操作的结果来存储所述第一故障地址到所述第一冗余地址的第一冗余映射;将所述多个存储单元当中的第二故障存储单元的第二故障地址与所述第一故障地址进行比较;响应于所述第二故障地址与所述第一故障匹配,忽略所述第一冗余映射;基于所述比较的结果来生成对应于所述第一故障地址的脏信号,所述脏信号引起所述第一故障地址到与所述第一冗余地址不同的第二冗余地址的第二冗余映射;以及将所述脏信号输出到位于所述存储器件外部的测试主机装置。

技术特征:

1.一种存储器件,所述存储器件包括:

2.根据权利要求1所述的存储器件,其中,所述修复电路还被配置为存储所述第一故障地址、所述第一冗余映射和所述脏信号。

3.根据权利要求2所述的存储器件,其中,所述修复电路包括反熔丝阵列。

4.根据权利要求2所述的存储器件,其中,所述修复电路还被配置为:响应于所述第二故障地址与所述第一故障地址匹配,激活所述脏信号。

5.根据权利要求4所述的存储器件,其中,所述外部目的地包括测试主机装置,并且所述修复电路还被配置为通过所述存储器件的数据线将被激活的所述脏信号传输到所述测试主机装置。

6.根据权利要求2所述的存储器件,其中,所述修复电路还被配置为与所述第二故障地址对应地存储所述第一故障地址。

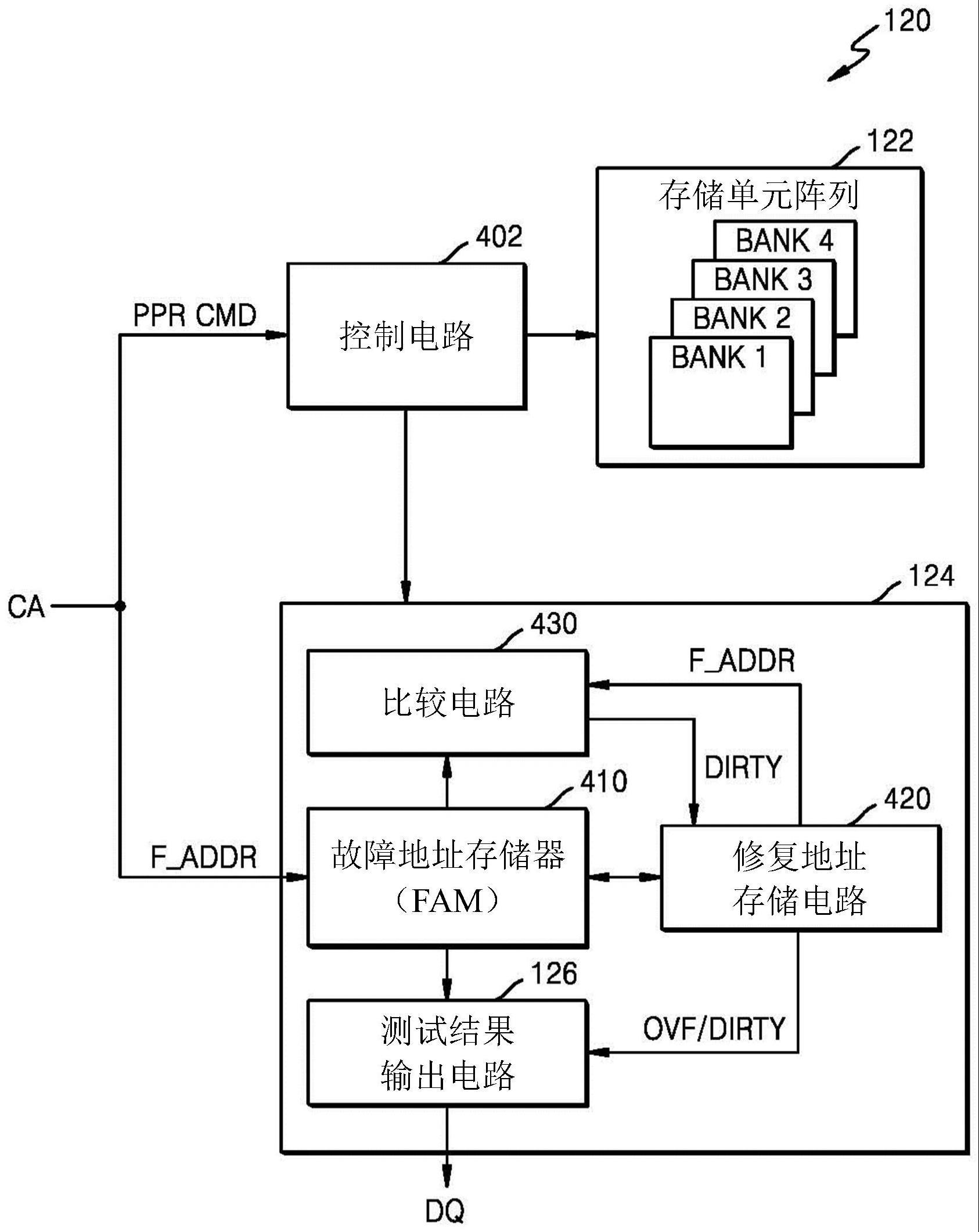

7.根据权利要求6所述的存储器件,其中,所述修复电路包括其中存储有所述第二故障地址的fam,所述fam即故障地址存储器,并且所述修复电路进一步被配置为通过将存储在所述修复电路中的所述第一故障地址与存储在所述fam中的所述第二故障地址进行比较来生成所述脏信号。

8.根据权利要求6所述的存储器件,其中,所述修复电路包括寄存器阵列。

9.根据权利要求6所述的存储器件,其中

10.一种存储器件,所述存储器件包括:

11.根据权利要求10所述的存储器件,其中,所述外部目的地包括测试主机装置,并且所述修复电路还被配置为通过所述存储器件的数据线将所述溢出标志信号输出到所述测试主机装置。

12.根据权利要求10所述的存储器件,其中,所述修复电路还被配置为存储所述第一故障地址。

13.根据权利要求12所述的存储器件,其中,所述修复电路包括反熔丝阵列,所述反熔丝阵列被配置为存储所述第一故障地址和所述第一冗余映射。

14.根据权利要求13所述的存储器件,其中,所述修复电路还被配置为响应于无法存储在所述反熔丝阵列中的新故障地址被生成而生成所述溢出标志信号。

15.根据权利要求12所述的存储器件,其中,所述修复电路还被配置为:

16.一种存储器件,所述存储器件包括:

17.根据权利要求16所述的存储器件,其中,所述修复电路还被配置为通过所述存储器件的数据线将所述第一信号传输到位于所述存储器件外部的测试主机装置。

18.根据权利要求16所述的存储器件,其中,所述修复电路还被配置为存储作为所述存储器测试操作的结果而获得的一个或更多个故障地址。

19.根据权利要求18所述的存储器件,其中,所述修复电路还被配置为向所述外部目的地输出第二信号,所述第二信号指示要存储的故障地址的数目超过了能够被存储在所述修复电路中的故障地址的数目。

20.根据权利要求19所述的存储器件,其中,所述修复电路还被配置为通过所述存储器件的数据线将所述第二信号传输到位于所述存储器件外部的测试主机装置。

技术总结

提供了一种输出测试结果的存储器件及测试其的方法。所述存储器件包括:存储单元阵列;以及修复电路,所述修复电路被配置为执行修复操作并且向位于所述存储器件外部的外部目的地输出脏信号。所述修复电路还执行如下操作:选择冗余存储单元的第一冗余地址而不是第一故障存储单元的第一故障地址,存储所述第一故障地址到所述第一冗余地址的第一冗余映射,以及响应于确定第二故障存储单元的第二故障地址与所述第一故障地址匹配,忽略所述第一冗余映射,并且输出脏信号,所述脏信号引起将所述第一故障地址映射到所述冗余存储单元的与所述第一冗余地址不同的第二冗余地址的第二冗余映射。

技术研发人员:孙钟弼

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!