一种拓扑相变材料忆阻器件的极性切换方法与流程

1.本发明属于半导体信息存储和人工突触器件技术领域,更具体地,涉及一种拓扑相变材料忆阻器件的极性切换方法。

背景技术:

[0002]“拓扑相变”是针对材料结构稳定性而言的一种表述,当材料中的构成元素被抽取一部分后依然具有稳定的晶格框架,其相应的物理结构以及化学性质会产生一定的变化,这类材料被称为拓扑相变材料。典型的拓扑相变材料srfeo

x

(sfo)通过得失氧可在srfeo3钙钛矿(perovskite,pv)相和srfeo

2.5

钙铁石(brownmillerite,bm)相之间互相转化。pv-sfo中的o 2p轨道转移一个电子到fe 3d轨道后处于未占满状态,电荷转移能量为负,没有带隙,呈金属导电相。bm-sfo中o 2p轨道到未占据的fe 3d轨道之间电荷转移能量为正,形成约2ev的带隙,呈绝缘相。通过外加电场可使sfo材料在pv相和bm相之间转化,材料的电阻值随之发生变化,根据这个性质可应用于忆阻器领域的研究,是近年来研究的热点。基于sfo材料的忆阻器件是通过氧离子的迁移来调控sfo忆阻器件的导电通道。置位(set)过程中通过施加电压使氧离子发生迁移,沿途路径上的bm-sfo接收氧离子会转化为pv-sfo形成导电丝通道连接上下电极,器件从高阻转化为低阻;复位(reset)过程通过施加反向电压,set过程形成的pv-sfo失去氧离子转化为bm-sfo从而断开导电通道。

[0003]

传统双极性忆阻器件的操作方向取决于功能层以及电极层的选择,在器件结构固定后,其操作方向很难进行切换调控,限制了忆阻器的可操作范围。图1、图2分别展示了忆阻器在构造与、或逻辑时的逻辑单元,可以看出,逻辑的切换需要依靠改变输入端忆阻器的极性来实现。此时,如果忆阻器m1和m2可以自由进行极性切换,图一和图二两个逻辑单元可以简并为一个。因此,有必要研究一种极性可切换的拓扑相变材料忆阻器件,以提供其在封装后的使用场景。

技术实现要素:

[0004]

针对现有技术的缺陷,本发明的目的在于提供一种拓扑相变材料忆阻器件的极性切换方法,通过施加偏压的方式改变忆阻器件极性,可有效提高忆阻器件的应用场景和潜力。

[0005]

为实现上述目的,第一方面,本发明提供了一种拓扑相变材料忆阻器件的极性切换方法,所述拓扑相变材料忆阻器件包括由下而上依次设置的衬底层、底电极层、存储介质层和顶电极层,所述存储介质层的材料采用纯相srfeo

2.5

或srcoo

2.5

,所述极性切换方法包括正向置位负向复位切换至负向置位正向复位的第一切换方法、及负向置位正向复位切换至正向置位负向复位的第二切换方法;

[0006]

其中,所述第一切换方法包括如下步骤:

[0007]

(1)将所述拓扑相变材料忆阻器件的底电极层接地,在其顶电极层施加0~-9v负向直流扫描电压完成电成型操作;

[0008]

(2)在所述顶电极层施加0~2v正向直流扫描电压完成set操作,然后在顶电极层施加0~-2.5v负向直流扫描电压完成reset操作,使得所述拓扑相变材料忆阻器件为正向置位负向复位状态;

[0009]

(3)在顶电极层施加0~+6v正向直流扫描电压,然后在所述顶电极层施加0~-2v负向直流扫描电压完成set操作,接着在顶电极施加0~+2.5v正向直流扫描电压完成reset操作,使得所述拓扑相变材料忆阻器件为负向置位正向复位;

[0010]

所述第二切换方法包括如下步骤:

[0011]

(4)在步骤(3)的拓扑相变材料忆阻器件中的顶电极层上施加0~-6v负向直流扫描电压,然后在所述顶电极层施加0~2v正向直流扫描电压完成set操作,接着在顶电极层施加0~-2.5v负向直流扫描电压完成reset操作,使得所述拓扑相变材料忆阻器件为正向置位负向复位状态。

[0012]

本发明提供的拓扑相变材料忆阻器件的极性切换方法,存储介质层采用纯相srfeo

2.5

或srcoo

2.5

,通过施加偏压的方式调控存储介质层中氧离子的迁移和聚集行为,可实现对忆阻器件的极性切换,有效提高该器件在封装后的使用场景。

[0013]

在其中一个实施例中,所述存储介质层的晶向为《111》或《110》方向,其厚度范围为30~50nm。

[0014]

在其中一个实施例中,所述底电极层的材料采用srruo3,其晶向为《111》或《110》方向,其厚度范围为50~100nm。

[0015]

在其中一个实施例中,所述顶电极层的材料采用纯相pt或au,其厚度范围为80~100nm。

[0016]

在其中一个实施例中,所述顶电极层的尺寸为60

×

60~100

×

100μm2。

[0017]

在其中一个实施例中,所述衬底层的材料采用纯相srtio3,其晶向为《111》方向。

[0018]

第二方面,本发明提供了一种用于实现与或功能的逻辑单元,包括两个上述所述的拓扑相变材料忆阻器件。

附图说明

[0019]

图1是传统与门逻辑单元的结构示意图;

[0020]

图2是传统或门逻辑单元的结构示意图;

[0021]

图3是本发明一实施例提供的拓扑相变材料忆阻器件的结构示意图;

[0022]

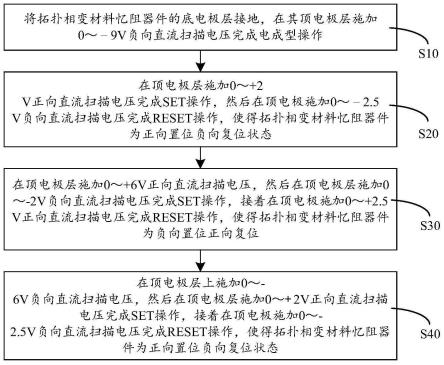

图4是图3提供的拓扑相变材料忆阻器件的极性切换方法的流程图;

[0023]

图5是本发明一实施例中存储介质层在步骤s20中施加的偏压下的电流变化曲线图;

[0024]

图6是本发明一实施例中存储介质层在步骤s30中施加的偏压下的电流变化曲线图;

[0025]

图7是本发明一实施例中存储介质层在步骤s40中施加的偏压下的电流变化曲线图;

[0026]

图8是本发明一实施例提供的拓扑相变材料忆阻器件的极性切换方法的原理示意图。

具体实施方式

[0027]

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0028]

图3是本发明一实施例提供的极性可切换的拓扑相变材料忆阻器件的结构示意图,如图3所示,本实施例提供的忆阻器件包括由下而上依次设置的衬底层、底电极层、存储介质层和顶电极层。

[0029]

在本实施例中,衬底层主要起支撑作用,其材料可纯相srtio3,其晶向可为《111》或《110》方向。底电极层和顶电极层为输入偏置电压的两电极,具体地,底电极层的材料可采用纯相srruo3,其晶向为《111》或《110》方向,其厚度范围为50~100nm;顶电极层的材料可采用纯相pt或au,其厚度范围为80~100nm,尺寸为60

×

60~100

×

100μm2。

[0030]

本实施例提供的存储介质层采用纯相srfeo

2.5

或srcoo

2.5

的相变材料制成,本发明主要通过调节施加在存储介质层上的偏置电压,调控纯相srfeo

2.5

或srcoo

2.5

中阳离子的迁移和聚集行为,来实现该拓扑相变材料忆阻器件的极性转变(操作方向转变),即正向置位负向复位和负向置位正向复位两种状态之间的切换。

[0031]

其中,如图4所示,正向置位负向复位切换至负向置位正向复位的切换方法,具体为:

[0032]

s10,将拓扑相变材料忆阻器件的底电极层接地,在其顶电极层施加0~-9v负向直流扫描电压完成电成型操作。

[0033]

s20,如图5所示,在顶电极层施加0~2v正向直流扫描电压完成set操作,然后在顶电极施加0~-2.5v负向直流扫描电压完成reset操作,使得拓扑相变材料忆阻器件为正向置位负向复位状态。

[0034]

s30,如图6所示,在顶电极层施加0~+6v正向直流扫描电压,然后在顶电极层施加0~-2v负向直流扫描电压完成set操作,接着在顶电极施加0~+2.5v正向直流扫描电压完成reset操作,使得拓扑相变材料忆阻器件为负向置位正向复位。

[0035]

负向置位正向复位切换至正向置位负向复位的切换方法,具体为:

[0036]

s40,如图7所示,在步骤3的拓扑相变材料忆阻器件中的顶电极上施加0~-6v负向直流扫描电压,重复上述步骤s20,即在顶电极层施加0~2v正向直流扫描电压完成set操作,接着在顶电极层施加0~-2.5v负向直流扫描电压完成reset操作,即可使拓扑相变材料忆阻器件为正向置位负向复位状态。

[0037]

本实施例提供的拓扑相变材料忆阻器件的极性切换原理为:

[0038]

如图8所示,图8中

①

显示为忆阻器件初始状态,施加9v的负偏压后,空气及表面的氧会通过顶电极层聚集至存储介质层的下界面,忆阻器件完成电成型,如图8中

②

所示。此时继续施加2v的正偏压,存储介质层底部的部分氧离子会向上迁移,形成导电丝,实现正向置位操作,如图8中

③

所示。当忆阻器件极性被施加2.5v的负偏压时,氧离子回到存储介质层底部,忆阻器件完成负向复位操作,如图8中

④

所示,使得此时的忆阻器件为正向置位负向复位状态。随后继续施加6v的正偏压,大量氧离子向上迁移至存储介质层的顶部,如图8中

⑤

所示,然后再继续施加2v的负偏压,部分上界面的氧离子向下迁移,形成自上而下的导电通道,忆阻器件实现负向置位操作,如图8中

⑥

所示,此时再施加2.5v正偏压,这一部分氧

离子回到上界面,忆阻器件完成正向复位操作,如图8中

⑦

所示,使得此时的忆阻器件为负向置位正向复位状态,从而完成正向置位负向复位到负向置位正向复位的极性切换。

[0039]

当忆阻器件为负向置位正向复位状态时,再施加6v负偏压,上界面的氧离子全部迁移回到下界面,器件回到刚刚完成电成型的状态,如图8中

⑧

所示。然后重复上述步骤2(原理可参见前述说明),即可使忆阻器件回到正向置位负向复位状态。

[0040]

本实施例提供的拓扑相变材料忆阻器件的极性切换方法,存储介质层采用纯相srfeo

2.5

或srcoo

2.5

,通过施加偏压的方式调控存储介质层中氧离子的迁移和聚集行为,可实现对忆阻器件的极性切换,有效提高该器件在封装后的使用场景。

[0041]

基于同样的发明构思,本发明还提供了一种用于实现与或功能的逻辑单元,包括两个前述实施例提供的拓扑相变材料忆阻器件,即将传统与门或或门的逻辑单元(如图1和图2所示)中的忆阻器件m1和m2替换成本发明提供的拓扑相变材料拓扑忆阻器件即可,替换后的逻辑单元通过上述实施例施加偏压的方式对该忆阻器件的极性进行切换,从而即可实现与功能,也可以实现或功能。

[0042]

以下结合具体实施例对本发明进行详细说明:

[0043]

实施例1提供了一种拓扑相变材料忆阻器件,包括:

[0044]

特征结构层

①

为衬底层,成分为纯相srtio3,其晶向为《111》方向。

[0045]

特征结构层

②

为底电极层,成分为纯相srruo3,其晶向为《111》方向,其厚度为50nm。

[0046]

特征结构层

③

为存储介质层,成分为纯相srfeo

2.5

,其晶向为《111》方向,其厚度范围为30nm。

[0047]

特征结构层

④

为顶电极层,成分为纯相au,其厚度范围为80~100nm,尺寸为60

×

60μm2。

[0048]

施加如下步骤切换器件极性:

[0049]

步骤一:将底电极接地,在顶电极施加0~-9v负向直流扫描电压完成电成型操作。

[0050]

步骤二:在顶电极施加2v正电压完成set操作。

[0051]

步骤三:在顶电极施加-2.5v负电压完成reset操作。

[0052]

步骤四:在顶电极施加+6v正电压完成正向切负向的极性切换操作。

[0053]

步骤五:在顶电极施加-2v负电压完成set操作。

[0054]

步骤六:在顶电极施加+2.5v正电压完成reset操作。

[0055]

步骤七:在顶电极施加-5v负电压完成负向切正向的极性切换操作。

[0056]

步骤八:在顶电极施加2v正电压完成set操作(重复步骤二)。

[0057]

步骤九:在顶电极施加-2.5v负电压完成reset操作(重复步骤三)。

[0058]

实施例2提供了一种拓扑相变材料忆阻器件,包括:

[0059]

特征结构层

①

为衬底层,成分为纯相srtio3,其晶向为《110》方向。

[0060]

特征结构层

②

为底电极层,成分为纯相srruo3,其晶向为《110》方向,其厚度范围为60nm。

[0061]

特征结构层

③

为存储介质层,成分为纯相srcoo

2.5

,其晶向为《110》方向,其厚度范围为40nm。

[0062]

特征结构层

④

为顶电极层,成分为纯相pt,其厚度范围为100nm,尺寸为80

×

80μ

m2。

[0063]

施加如下步骤切换器件极性:

[0064]

步骤一:将底电极接地,在顶电极施加0~-9v负向直流扫描电压完成电成型操作。

[0065]

步骤二:将器件底电极接地,在顶电极施加2v正电压完成set操作。

[0066]

步骤三:在顶电极施加-2.5v负电压完成reset操作。

[0067]

步骤四:在顶电极施加+6v正电压完成正向切负向的极性切换操作。

[0068]

步骤五:在顶电极施加-2v负电压完成set操作。

[0069]

步骤六:在顶电极施加+2.5v正电压完成reset操作。

[0070]

步骤七:在顶电极施加-5v负电压完成负向切正向的极性切换操作。

[0071]

步骤八:在顶电极施加2v正电压完成set操作(重复步骤二)。

[0072]

步骤九:在顶电极施加-2.5v负电压完成reset操作(重复步骤三)。

[0073]

本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1