非易失性存储器及其电压检测电路的制作方法

本发明涉及一种非易失性存储器及其内部电路,且特别涉及一种可处于闲置模式(idle mode)下的非易失性存储器(non-volatile memory)及其相关的电压检测电路。

背景技术:

1、众所周知,非易失性存储器(non-volatile memory)已经非常广泛的应用于各种电子产品。在低功耗(low power)的电子产品中,非易失性存储器会进入闲置模式(idlemode),以防止过多功率损耗。

2、请参照图1,其所绘示为已知电子产品中非易失性存储器示意图。非易失性存储器100包括一存储器模块(memory module)120、处理单元112与电源供应单元114。存储器模块120中包括一驱动电路122与一存储器阵列(memory array)124。

3、非易失性存储器100连接至一主机(host)180并接收一供应电压(supplyvoltage)vdd。举例来说,电子产品的电池提供供应电压vdd,使得非易失性存储器100接收供应电压vdd而运作。

4、处理单元112连接至主机180以及存储器模块120。当非易失性存储器100在正常模式(normal mode)时,处理单元112接收主机180发出的存取指令(access command),并产生控制信号ctrl来存取存储器模块120中的数据。

5、再者,电源供应单元114将供应电压vdd转换为阵列电压varray,并传递至存储器模块120的驱动电路122。举例来说,驱动电路122中至少包括一字线驱动器(word linedriver)。字线驱动器接收阵列电压varray,且字线驱动器连接至存储器阵列124的多条字线wl1~wln。

6、当处理单元112存取存储器模块120中的数据时,字线驱动器将阵列电压varray转换为字线电压(word line voltage),并根据控制信号ctrl来驱动存储器阵列124中的特定一条字线(word line)。

7、当主机180与非易失性存储器100之间未进行存取动作超过一特定时间之后,非易失性存储器100会切换为闲置模式(idle mode)。在闲置模式时,处理单元112有效(assert,又称之为“断言”)待机信号(standby signal,stb)并维持一小部分的内部电路运作。另外,电源供应单元114则根据待机信号stb而停止运作。因此,电源供应单元114停止产生阵列电压varray,使得存储器模块120也停止运作。

8、当主机180对非易失性存储器100再次进行存取动作时,非易失性存储器100会再次由闲置模式(idle mode)切换至正常模式(normal mode)。此时,处理单元112无效(deassert,又称之为“解除断言”)待机信号stb,电源供应单元114会再次启动(start-up)并产生阵列电压varray。

9、然而,由于电源供应单元114启动时间(start-up time)过长,在启动的过程中,阵列电压varray尚未准备好(ready),驱动电路122无法即时接收阵列电压varray来快速地(quickly)驱动字线。也就是说,当非易失性存储器100由闲置模式(idle mode)切换至正常模式(normal mode)时,由于电源供应单元114无法即时供阵列电压varray,将导致处理单元112无法即时存取存储器模块120中的数据,造成非易失性存储器100的存取效率(performance)降低。

10、为了解决非易失性存储器100由闲置模式切换至正常模式的初期,处理单元112无法即时存取存储器模块120的缺陷。在已知非易失性存储器100中可以设计一个启动时间(start-up time)短,能够快速准备好(ready)阵列电压varray的电源供应单元114。

11、然而,电源供应单元114至少包括:带差参考电路(bandgap reference circuit)、电压调整器(voltage regulator)与电荷泵(charge pump)。为了缩短电源供应单元114的启动时间(start-up time),需要的电荷泵尺寸(size)会非常大,会占据电源供应单元114很大的布局面积(layout area)。

12、请参照图2,其所绘示为已知另一非易失性存储器示意图。相较于图1的非易失性存储器100,非易失性存储器200中还包括一辅助电源供应单元210。

13、辅助电源供应单元210接收供应电压vdd以及待机信号stb,并产生阵列电压varray。在正常模式时,待机信号stb无效,辅助电源供应单元210未运作,由电源供应单元114产生阵列电压varray。在闲置模式时,待机信号stb有效,电源供应单元114未运作,由辅助电源供应单元210产生阵列电压varray。

14、如上所述,不论在闲置模式或正常模式时,非易失性存储器200中的存储器模块120皆能收到阵列电压varray。因此,当非易失性存储器200由闲置模式切换至正常模式时,由于存储器模块120已经接收到阵列电压varray,所以处理单元112可立刻存取存储器模块120中的数据。

15、然而,在非易失性存储器200中增加辅助电源供应单元210也会增加布5局面积(layout area),并且产生额外的功耗。

技术实现思路

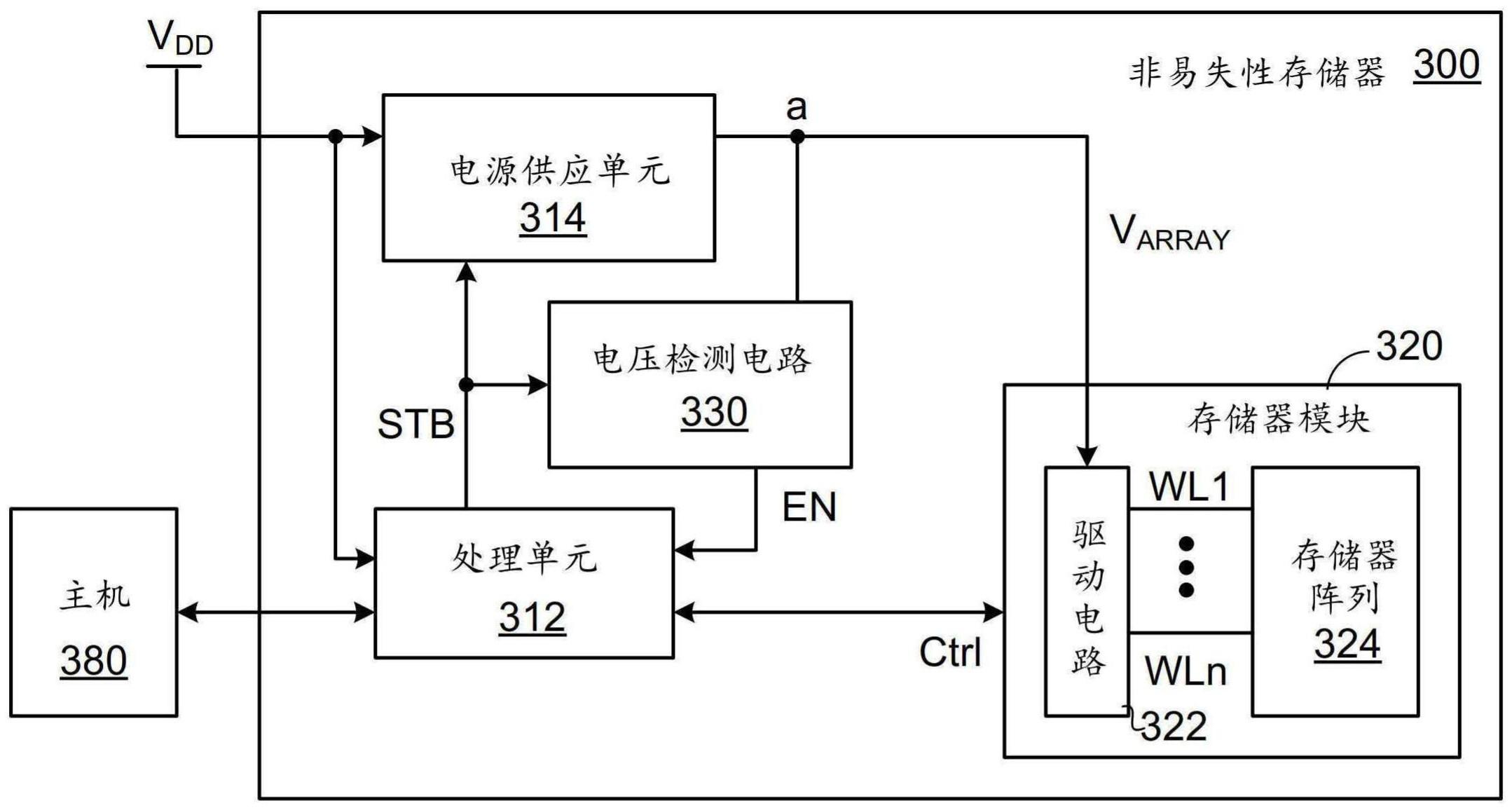

1、本发明涉及一种非易失性存储器,包括:一处理单元,产生一待机信号;

2、一电源供应单元,连接至一第一节点,该电源供应单元接收该待机信号,其0中当待机信号无效时,该电源供应单元将一供应电压转换为一第一数值的一

3、阵列电压,并输出该阵列电压至该第一节点,且当待机信号有效时,该电源供应单元停止产生该阵列电压;一电压检测电路,连接至该第一节点并接收该待机信号,其中当该待机信号有效时,该电压检测电路检测该第一节点上

4、的该阵列电压;以及,一存储器模块,连接至该第一节点并接收该阵列电压;5其中,当该阵列电压由该第一数值降低并到达一第二数值时,该电压检测电

5、路有效一致能信号以致能该处理单元,使得该处理单元使该待机信号无效;其中,当该阵列电压由该第二数值上升并到达该第一数值时,该处理单元使该待机信号有效,且该电压检测电路使该致能信号无效。

6、本发明涉及一种非易失性存储器中的一电压检测电路,该非易失性存储0器中包括一电源供应单元连接至一第一节点,当一待机信号无效时,该电源

7、供应单元输出一第一数值的一阵列电压至该第一节点,当该待机信号有效时,该电源供应单元停止输出该阵列电压,该电压检测电路包括:一初始电压产生器,该初始电压产生器接收一反相待机信号与一致能信号,该初始电压产

8、生器的一输出端连接至一第二节点;一电容器,该电容器的一第一端耦接至5该第一节点,该电容器的一第二端耦接至该第二节点;一锁存器,该锁存器的一输入端连接至该第二节点,该锁存器的一输出端连接至一第三节点,该锁存器的一第一电源端耦接至一供应电压,该锁存器的一第二电源端耦接至一接地端;以及,一组合逻辑电路,该组合逻辑电路的一输入端连接至该第三节点,该组合逻辑电路的一输出端产生该致能信号。

9、0为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,

10、并配合附图,作详细说明如下:

- 还没有人留言评论。精彩留言会获得点赞!