一种应用于DRAM外围晶体管的短期偏压温度不稳定性分析方法与流程

本发明涉及dram外围器件可靠性问题分析领域,具体涉及一种应用于dram外围晶体管的短期偏压温度不稳定性分析方法。

背景技术:

1、随着物联网与人工智能等技术发展,数据量呈井喷式增加,对存储器提出了更高的要求。而dram作为最广泛使用的存储器之一,对其可靠性的要求也愈发严格。为了满足目前亚20nm dram工艺需求,各大dram厂商纷纷引入高介电常数(high-k)材料到晶体管栅氧层上来抑制器件漏电问题,但随之也引入了大量原生陷阱到栅氧层中,这会使得器件的偏压温度不稳定性(bti)更加严重。此外,为了提高dram的保持时间,通常会用氢进行高温退火来钝化cell器件的缺陷,这会在氧化层与衬底界面处形成大量si-h键,降低bti的可靠性。dram目前操作速度已经高达gbp/s,因此只考虑长时bti是远远不够的,需要分析dram高速工作状态下的短时bti效应。

2、参考图1,目前常用的基于电容-电压(cvu)测试方法以及源测试单元(smu),虽然精度较高,但在时间尺度上只能达到毫秒(ms)量级;即使采用脉冲iv测试技术(piv)也只能达到微秒(μs)量级,并且还是在牺牲精度的前提下来完成。而电荷泵技术(cp)通过测试缺陷捕获释放过程产生的平均电流,可以同时保证高速与高精度两个矛盾的需求。除此以外,最近证据表明在bti中存在多种类型缺陷(电子陷阱和空穴陷阱)的影响,因此如何分离出不同类型陷阱并提取出各自的空间分布和能级位置也是一个难题。而传统的cp技术分离得到的陷阱能级位置相对粗糙并且无法计算得到氧化层陷阱。改进的“可变充放电时间和幅度的电荷泵技术”(vt2acp)虽然能得到氧化层陷阱的空间位置和能级分布,但也是粗略估算,不够准确。

3、综上所述,现有技术方案尚无法在dram外围器件上实现高速短时bti测试分析,需要一个可靠的技术方案,实现对dram外围器件在ghz高速工作条件下的bti引起的退化的准确预测。

技术实现思路

1、针对以上现有技术中存在的问题,本发明提出了一种应用于dram外围晶体管的短期偏压温度不稳定性分析方法。

2、本发明提供的技术方案如下:

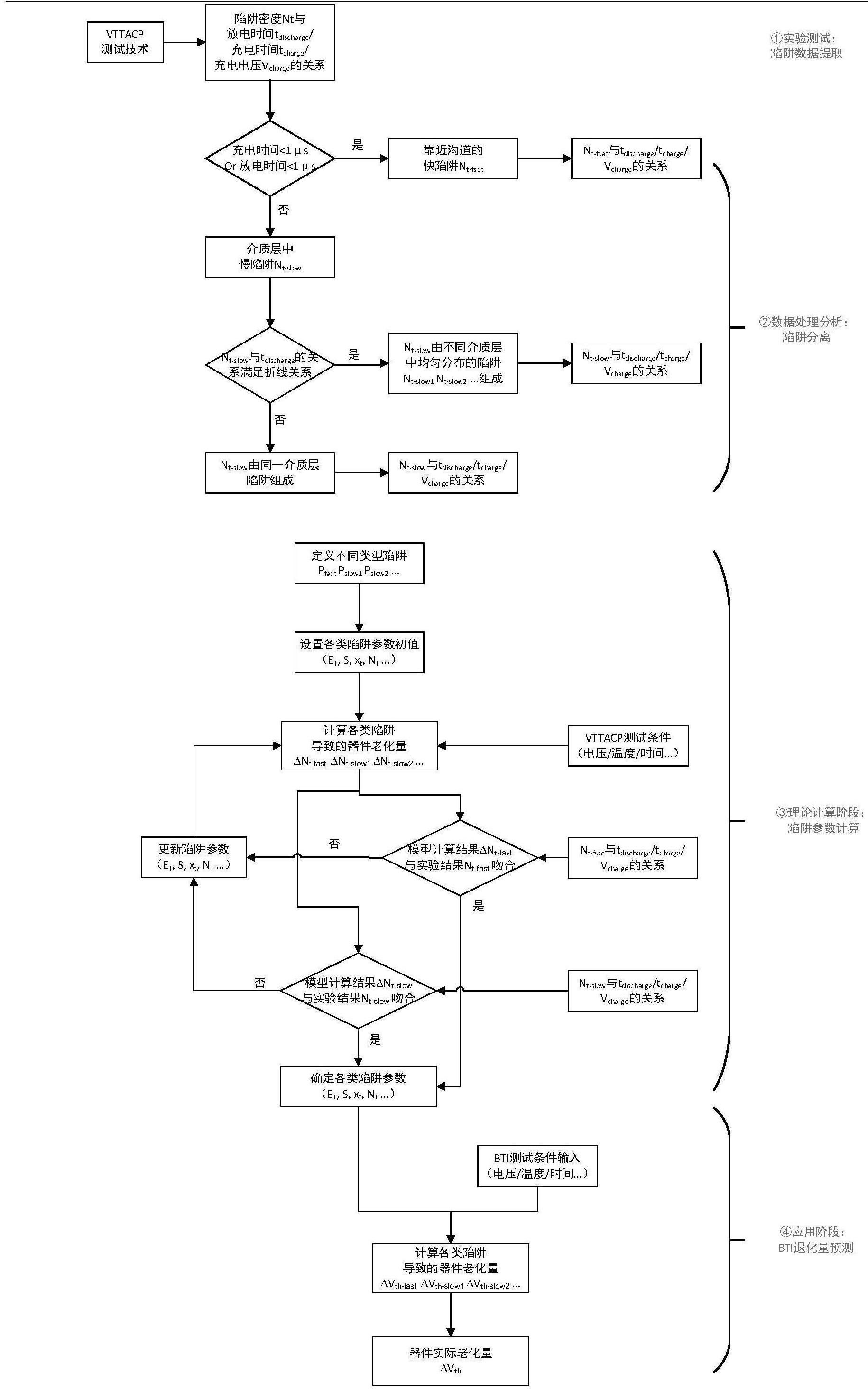

3、一种应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其步骤包括:

4、1)采用vt2acp技术原理,针对待分析晶体管进行实验,得到陷阱密度nt随tcharge、tdischarge和vcharge的变化关系;

5、2)根据充放电时间的大小来区分出靠近沟道的快陷阱nt-fast与分布在介质层中的慢陷阱nt-slow,并得到快陷阱nt-fast随tcharge、tdischarge和vcharge的变化关系;以及慢陷阱nt-slow随tdischarge、tdischarge和vcharge的变化关系;

6、3)设置各类陷阱的参数,包括陷阱能级et,陷阱弛豫能s,陷阱距离沟道的距离xt,陷阱的总密度nt;采用非辐射多声子理论对不同类型陷阱的时间动力学进行仿真计算,使得仿真结果nt-fast随tcharge、tdischarge和vcharge的变化关系,nt-slow随tdischarge、tdischarge和vcharge的变化关系与实验数据相匹配;

7、4)采用步骤3)获得的各类陷阱的参数计算出任意电压、温度、时间下待分析晶体管的不同陷阱的bti老化量,通过叠加不同类型陷阱的贡献,即可得到总的bti老化量。

8、进一步,步骤1)中实验具体为:结合晶体管正常工作电压条件,施加对应的电压信号到晶体管栅极,使得晶体管在反型状态下进行陷阱捕获载流子的过程与积累状态进行陷阱释放载流子的过程之间不断转换,从而让陷阱贡献到衬底电流ibulk中。

9、进一步,通过改变tcharge从1μs到500μs和tdischarge从100ns到10ms来实现让氧化层更深处陷阱参与到充放电过程中,通过改变充电电压vcharge从-1v到-1.8v来实现不同能级位置上的陷阱参与到充放电过程中。

10、进一步,步骤2)中如果充电时间或者放电时间小于μs量级,则该部分陷阱为快陷阱;如果充放电时间大于1μs,则该部分陷阱为慢陷阱。

11、进一步,步骤2)中判定慢陷阱位于多层介质中或存在于单一介质层的方法是,分析nt-slow与放电时间的关系,如果出现不同斜率的折线,则慢陷阱分布在不同介质层中,转折点即是不同介质层的接触位置;如果nt-slow与放电时间的关系为单一斜率的一次函数关系,则陷阱只分布在一种介质层中。

12、进一步,步骤3)中通过非线性优化的算法不断迭代优化各类陷阱的参数,直到匹配到一组最优的参数。

13、本发明的有益效果:本发明解决了传统缺陷分析技术的短板,可以测量并分离最短在ns量级捕获或者释放载流子的陷阱,对于开发工作在ghz的dram的可靠性模型以及可靠性模拟电路具有重大意义;此外本发明的测试方案操作性强、容易实施,并且基于底层缺陷参数和相应物理理论完成最终bti退化量预测,结果更加准确、可靠。

技术特征:

1.一种应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其步骤包括:

2.如权利要求1所述的应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其特征在于,步骤1)中实验具体为:结合晶体管正常工作电压条件,施加对应的电压信号到晶体管栅极,使得晶体管在反型状态下进行陷阱捕获载流子的过程与积累状态进行陷阱释放载流子的过程之间不断转换,从而让陷阱贡献到衬底电流ibulk中。

3.如权利要求2所述的应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其特征在于,通过改变tcharge从1μs到500μs和tdischarge从100ns到10ms来实现让氧化层更深处陷阱参与到充放电过程中,通过改变充电电压vcharge从-1v到-1.8v来实现不同能级位置上的陷阱参与到充放电过程中。

4.如权利要求1所述的应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其特征在于,步骤2)中如果充电时间或者放电时间小于μs量级,则该部分陷阱为快陷阱;如果充放电时间大于1μs,则该部分陷阱为慢陷阱。

5.如权利要求1所述的应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其特征在于,步骤2)中判定慢陷阱位于多层介质中或存在于单一介质层的方法是,分析nt-slow与放电时间的关系,如果出现不同斜率的折线,则慢陷阱分布在不同介质层中,转折点即是不同介质层的接触位置;如果nt-slow与放电时间的关系为单一斜率的一次函数关系,则陷阱只分布在一种介质层中。

6.如权利要求1所述的应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其特征在于,步骤3)中通过非线性优化的算法不断迭代优化各类陷阱的参数,直到匹配到一组最优的参数。

7.如权利要求1所述的应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其特征在于,步骤3)中陷阱能级et包括:高斯分布下的均值<et>与标准差σet。

8.如权利要求1所述的应用于dram外围晶体管的短期偏压温度不稳定性分析方法,其特征在于,步骤3)中陷阱弛豫能s包括:高斯分布下的均值<s>与标准差σs。

技术总结

本发明公开了一种应用于DRAM外围晶体管的短期偏压温度不稳定性分析方法,属于DRAM外围器件可靠性问题分析领域。本发明对待分析晶体管进行实验,区分出不同的陷阱类型,利用仿真计算得到任意电压、温度、时间下的不同陷阱的老化量。本发明解决了传统缺陷分析技术的短板,可以测量并分离最短在ns量级捕获或者释放载流子的陷阱,对于开发工作在GHz的DRAM的可靠性模型以及可靠性模拟电路具有重大意义;此外本发明的测试方案操作性强、容易实施,并且基于底层缺陷参数和相应物理理论完成最终BTI退化量预测,结果更加准确、可靠。

技术研发人员:王润声,纪志罡,王达,任鹏鹏

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!