测试只读存储器程序的方法、待测设计、测试设备和介质与流程

本发明涉及程序测试,尤其涉及测试只读存储器程序的方法、待测设计、测试设备和介质。

背景技术:

1、rom(read-only memory,只读存储器)内部存储的程序代码是在芯片制造过程中固化在芯片内部的,后期不能修改。如果rom中的程序代码出现了错误,将有可能导致rom所在的芯片或者智能设备无法正常工作。因此在制造之前需要确认rom的程序代码无误。

2、可以借助芯片原型验证平台,将rom程序代码加载到基于fpga(fieldprogrammable gate array,现场可编程门阵列)构造的rom模块内进行验证。在rom程序调试的初期,编写的程序代码中难免会有很多错误,需更多次修复更新rom程序代码。每更新一次rom程序代码就需要将原型验证平台的工程文件全部更新后,再载入fpga进行验证,耗费较大的人力以及较长的时间,测试效率较低。

技术实现思路

1、基于此,有必要针对上述问题,提出了测试只读存储器程序的方法、待测设计、测试设备和介质。

2、一种测试只读存储器程序的方法,应用于待测设计,所述待测设计包括测试存取器,所述测试存取器中存储有目标测试程序,包括至少一个写端口和至少一个读端口;

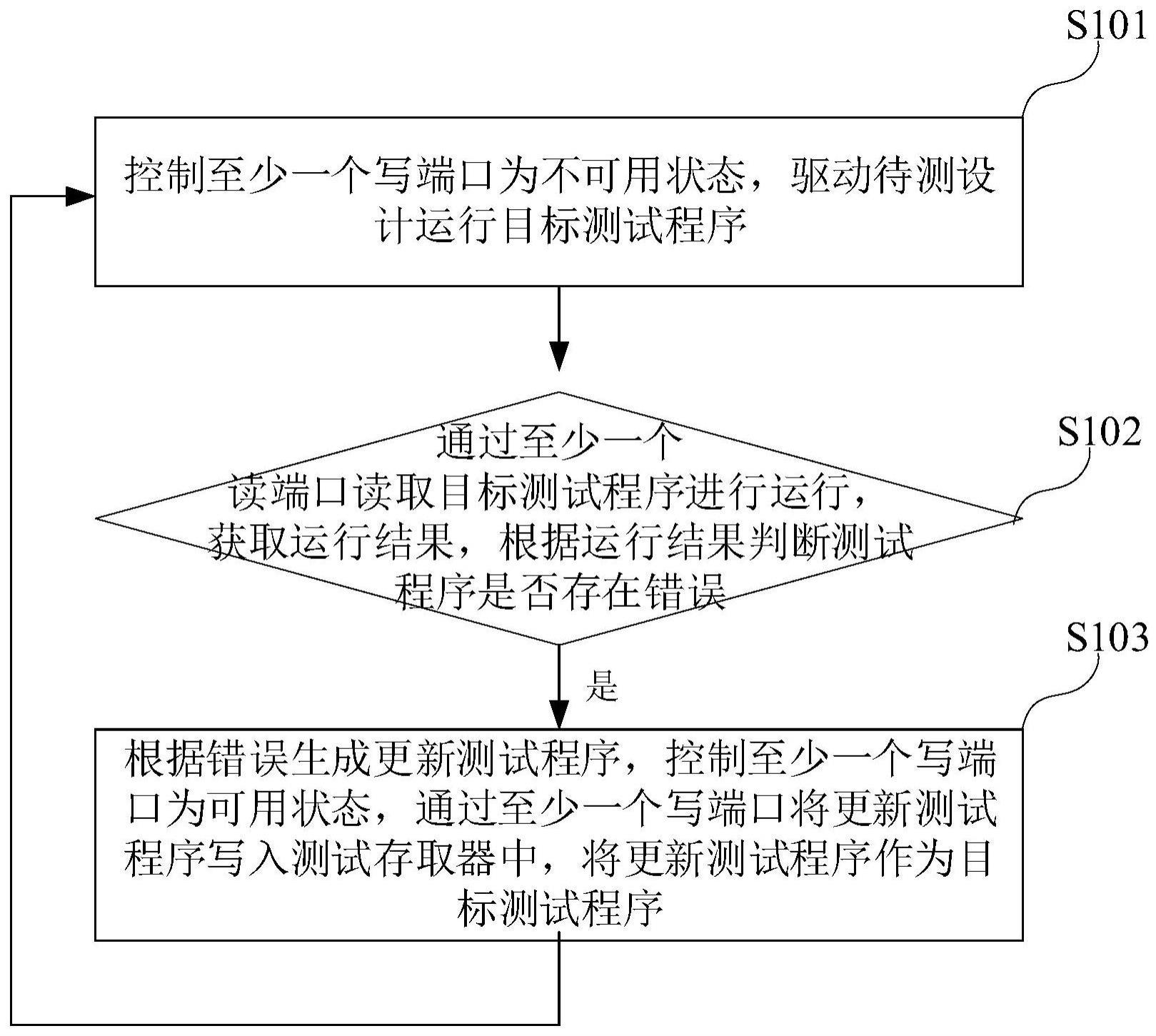

3、所述测试只读存储器的程序的方法包括如下步骤:

4、控制所述至少一个写端口为不可用状态,驱动所述待测设计运行所述目标测试程序;

5、通过所述至少一个读端口读取所述目标测试程序进行运行,获取运行结果,根据所述运行结果判断所述测试程序是否存在错误;

6、若根据所述运行结果判定所述测试程序存在错误,则根据所述错误生成更新测试程序,控制所述至少一个写端口为可用状态,通过所述至少一个写端口将所述更新测试程序写入所述测试存取器中,将所述更新测试程序作为新的目标测试程序,执行所述控制所述至少一个写端口为不可用状态的步骤,以及后续步骤。

7、其中,所述通过所述至少一个写端口将所述更新测试程序写入所述测试存取器中的步骤之前,包括:

8、将所述待测设计复位至初始状态;

9、所述通过所述至少一个写端口将所述更新测试程序写入所述测试存取器中的步骤之后,包括:

10、释放所述待测设计的复位,使得所述待测设计从初始状态恢复。

11、其中,所述控制所述至少一个写端口为不可用状态的步骤之前,包括:

12、通过交叉模块引用技术将所述至少一个写端口连接至所述待测设计外部,使在所述待测设计无需进行修改的条件下,使得所述至少一个写端口能够被所述待测设计外部的控制设备控制。

13、其中,所述通过交叉模块引用技术将所述至少一个写端口连接至所述待测设计外部的步骤之后,包括:

14、获取基于所述芯片原型验证平台和测试需求编译工程文件,将所述工程文件加载至所述芯片原型验证平台中,运行所述工程文件。

15、其中,所述根据所述运行结果判断所述测试程序是否存在错误的步骤之后,包括:

16、若根据所述运行结果判定所述测试程序不存在错误,则继续后续验证测试。

17、其中,所述至少一个写端口包括:写使能端口、写数据端口、写地址端口;

18、所述控制所述至少一个写端口为不可用状态的步骤,包括:

19、控制所述写使能端口为第一有效电平;或

20、控制所述写使能端口、所述写数据端口、所述写地址端口均为所述第一有效电平;

21、所述控制所述至少一个写端口为可用状态的步骤,包括:

22、控制所述写使能端口为第二有效电平;或

23、控制所述写使能端口、所述写数据端口、所述写地址端口均为所述第二有效电平。

24、一种芯片原型验证平台,用于运行如上所述的测试只读存储器程序的方法,包括:

25、待测设计,所述待测设计包括待测存取器模块,所述待测存取器模块包括测试存取器,所述测试存取器中存储有目标测试程序,包括至少一个写端口和至少一个读端口;

26、逻辑控制电路,连接所述至少一个写端口,用于控制所述至少一个写端口的状态为可用状态或者不可用状态;

27、通过接口模块,一端与所述逻辑控制电路连接,另一端与所述待测设计外部的测试电脑连接,用于接收所述测试电脑提供的更新测试程序,以使得所述更新测试程序能够通过所述逻辑控制电路写入所述测试存取器中。

28、其中,当需要对所述测试存取器中的所述目标测试程序进行验证测试时,所述逻辑控制电路控制所述至少一个写端口为不可用状态;

29、当需要更新所述测试存取器中的目标测试程序时,所述逻辑控制电路控制所述至少一个写端口为可用状态,从而所述测试电脑提供的更新测试程序能够通过所述逻辑控制电路写入所述测试存取器中。

30、一种计算机可读存储介质,存储有计算机程序,所述计算机程序被处理器执行时,使得所述处理器执行如上所述的步骤。

31、一种测试设备,包括存储器和处理器,所述存储器存储有计算机程序,所述计算机程序被所述处理器执行时,使得所述处理器执行如上所述的步骤。

32、采用本发明实施例,具有如下有益效果:

33、通过控制测试存取器的至少一个写端口的状态,实现测试存取器在ram模块的状态和rom模块的状态之间的切换,在更新目标测试程序时,至少一个写端口为可用状态,工程文件无需进行更新,仍然使用原先的工程文件,目标测试程序通过至少一个写端口写入了测试存取器,再将至少一个写端口调整为不可用状态,进行验证测试,在测试rom中的程序时,无需更新整个工程文件,只更新目标测试程序就能完成新一轮的验证测试,节约了大量的人力物力,提升了测试效率。

技术特征:

1.一种测试只读存储器程序的方法,其特征在于,应用于待测设计,所述待测设计包括测试存取器,所述测试存取器中存储有目标测试程序,包括至少一个写端口和至少一个读端口;

2.根据权利要求1所述的测试只读存储器程序的方法,其特征在于,所述通过所述至少一个写端口将所述更新测试程序写入所述测试存取器中的步骤之前,包括:

3.根据权利要求1所述的测试只读存储器程序的方法,其特征在于,所述控制所述至少一个写端口为不可用状态的步骤之前,包括:

4.根据权利要求3所述的测试只读存储器程序的方法,其特征在于,所述通过交叉模块引用技术将所述至少一个写端口连接至所述待测设计外部的步骤之后,包括:

5.根据权利要求1所述的测试只读存储器程序的方法,其特征在于,所述根据所述运行结果判断所述测试程序是否存在错误的步骤之后,包括:

6.根据权利要求1所述的测试只读存储器程序的方法,其特征在于,所述至少一个写端口包括:写使能端口、写数据端口、写地址端口;

7.一种芯片原型验证平台,其特征在于,用于运行权利要求1-6中任一项所述的测试只读存储器程序的方法,包括:

8.根据权利要求7所述的芯片原型验证平台,其特征在于,

9.一种计算机可读存储介质,存储有计算机程序,所述计算机程序被处理器执行时,使得所述处理器执行如权利要求1至6中任一项所述方法的步骤。

10.一种测试设备,包括存储器和处理器,所述存储器存储有计算机程序,所述计算机程序被所述处理器执行时,使得所述处理器执行如权利要求1至6中任一项所述方法的步骤。

技术总结

本发明涉及程序测试技术领域,公开了测试只读存储器程序的方法、待测设计、测试设备和介质。测试只读存储器的程序的方法包括如下步骤:控制至少一个写端口为不可用状态,驱动待测设计运行目标测试程序;通过至少一个读端口读取目标测试程序并进行运行,获取运行结果,根据运行结果判断测试程序是否存在错误;若根据运行结果判定测试程序存在错误,则根据错误生成更新测试程序,控制至少一个写端口为可用状态,通过至少一个写端口将更新测试程序写入测试存取器中,将更新测试程序作为新的目标测试程序,执行控制至少一个写端口为不可用状态的步骤,以及后续步骤。本发明能够有效节约大量的人力物力,提升测试效率。

技术研发人员:卢臣臣,蔡权雄,熊超,牛昕宇

受保护的技术使用者:深圳鲲云信息科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!