一种SRAM重置方法、电路、芯片、装置与介质与流程

本申请涉及芯片电路设计,尤其是一种sram重置方法、电路、装置与存储介质。

背景技术:

1、sram是一种专门定制的ip,一般没有复位功能。在一些应用场景下,需要在一个时钟周期内对sram进行复位,复位完成后,再次被写之前,从sram中所有地址读取的数据为全0或全1。比如spi nand中,load program data操作,只会向数据buffer的部分地址写入数据,没有使用到的地址需要重重为ff。因此,亟需一种新的sram 重置方法。

技术实现思路

1、本申请的目的在于至少一定程度上解决现有技术中存在的技术问题之一。

2、为此,本申请实施例的一个目的在于提供一种sram重置方法、电路、装置与存储介质,该方法可以提高sram的适配性,提高sram的实用性。

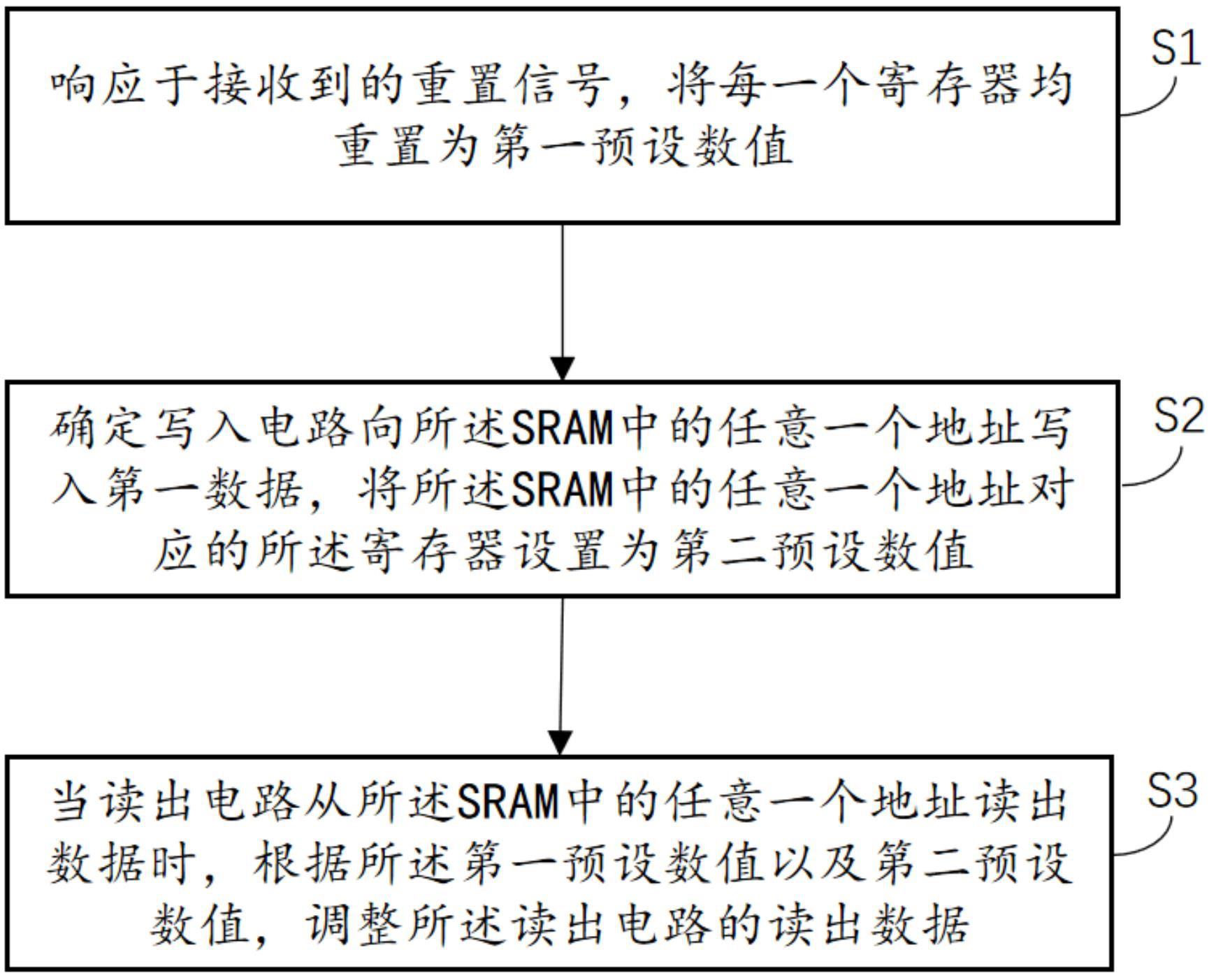

3、为了达到上述技术目的,本申请实施例所采取的技术方案包括:一种sram 重置方法,用于通过sram外围电路对sram进行重置;所述sram外围电路包括若干个寄存器;所述寄存器的数量与所述sram的地址的数量相等;所述sram的任意一个地址对应任意一个寄存器,重置方法包括:响应于接收到的重置信号,将每一个寄存器均重置为第一预设数值;确定写入电路向所述sram中的任意一个地址写入第一数据,将所述sram中的任意一个地址对应的所述寄存器设置为第二预设数值;当读出电路从所述sram中的任意一个地址读出数据时,根据所述第一预设数值以及第二预设数值,调整所述读出电路的读出数据。

4、另外,根据本发明中上述实施例的一种sram重置的方法,还可以有以下附加的技术特征:

5、进一步地,本申请实施例中,所述根据所述第一预设数值以及第二预设数值,调整所述读出电路的读出数据这一步骤,包括确定所述sram中的任意一个地址对应的所述寄存器为第一预设数值,将所述读出电路的读出数据调整为重置数据;确定所述sram中的任意一个地址对应的所述寄存器为第二预设数值,将所述所述读出电路的读出数据调整为第一数据。

6、进一步地,本申请实施例中,所述重置数据为sram中任意一地址对应的每个位区均为1或者任意一地址对应的每个位区均为0。

7、进一步地,本申请实施例中,所述第一预设数值为0,第二预设数值为1。

8、另一方面,本申请实施例还提供一种sram重置电路,用于执行上述实施例任一项所述的sram重置方法,包括:

9、写入电路、读出电路、sram以及若干个寄存器;所述写入电路与所述sram连接;所述读出电路与所述sram以及所述若干个寄存器连接;所述寄存器的数量与所述sram的地址的数量相同。

10、另一方面,本申请还提供一种sram重置装置,包括:

11、至少一个处理器;

12、至少一个存储器,用于存储至少一个程序;

13、当所述至少一个程序被所述至少一个处理器执行,使得所述至少一个处理器实现如

技术实现要素:

中任一项所述一种sram重置方法。

14、此外,本申请还提供一种存储介质,其中存储有处理器可执行的指令,所述处理器可执行的指令在由处理器执行时用于执行如上述任一项所述一种sram重置方法。

15、本申请的优点和有益效果将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本申请的实践了解到:

16、本申请可以先设置若干个与sram的地址数量相同的寄存器,在数据写入前,可以先通过重置将任意一个地址对应的寄存器设置为第一预设数值,确定写入电路向所述sram中的任意一个地址写入第一数据时,将所述sram中的任意一个地址对应的所述寄存器设置为第二预设数值;当读出电路从所述sram中的任意一个地址读出数据时,根据所述第一预设数值以及第二预设数值,调整读出电路的读出数据。本方法可以在数据写入前,可以先通过重置将任意一个地址对应的寄存器设置为第一预设数值可以避免数据读出后再对sram进行重置,使sram不局限于不需重置的应用场景,可以提高sram的适配性,可以提高sram的实用性。

技术特征:

1.一种sram 重置方法,其特征在于,用于通过sram外围电路对sram进行重置;所述sram外围电路包括若干个寄存器;所述寄存器的数量与所述sram的地址的数量相等;所述sram的任意一个地址对应任意一个寄存器,重置方法包括:

2.根据权利要求1所述一种sram重置方法,其特征在于,所述根据所述第一预设数值以及第二预设数值,调整所述读出电路的读出数据这一步骤,包括

3.根据权利要求2所述一种sram重置方法,其特征在于,所述重置数据为sram中任意一地址对应的每个位区均为1或者任意一地址对应的每个位区均为0。

4.根据权利要求1所述一种sram重置方法,其特征在于,所述第一预设数值为0,第二预设数值为1。

5.一种sram重置电路,其特征在于,用于执行上述权利要求1-4任一项所述的sram重置方法,包括:

6.一种内存芯片,其特征在于,包括上述权利要求5所述的sram重置电路。

7.一种sram重置装置,其特征在于包括:

8.一种存储介质,其中存储有处理器可执行的指令,其特征在于,所述处理器可执行的指令在由处理器执行时用于执行如权利要求1-4任一项所述的sram重置方法。

技术总结

本申请公开了一种SRAM重置方法、电路、芯片、装置和存储介质,方法用于通过外围电路对SRAM进行重置;外围电路包括寄存器;寄存器的数量与SRAM的地址的数量相等;SRAM的任意一个地址对应任意一个寄存器,方法包括:响应于接收到的重置信号,将每一个寄存器均重置为第一预设数值;确定写入电路向所述SRAM中的任意一个地址写入第一数据,将SRAM中的任意一个地址对应的寄存器设置为第二预设数值;当读出电路从SRAM中的任意一个地址读出数据时,根据第一预设数值以及第二预设数值,调整读出电路的读出数据。本方法可以可以提高SRAM的适配性,提高SRAM的实用性。本申请可广泛应用于芯片电路设计技术领域内。

技术研发人员:付本涛,刘弋波,赖鼐,龚晖

受保护的技术使用者:珠海妙存科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!