一种用于FLASH冗余修复的地址译码控制电路的制作方法

本发明涉及一种用于flash冗余修复的地址译码控制电路,属于存储器芯片设计。

背景技术:

1、在flash存储器的生产过程中,由于存在工艺的不确定性,会导致存储单元一致性差异,容易产生有缺陷的存储单元。传统字线地址译码器仅能根据输入字线地址信号选中对应的目标字线,当目标字线上存在缺陷存储单元时,无法对其进行正常的读取或者写擦操作,致使整个存储器无法正常使用。尤其是随着存储器技术的不断发展,存储密度越来越高,制造工艺越来越复杂,由此也往往会产生越来越多的工艺缺陷,导致flash存储器的成品率进一步降低,难以提高存储器产品产量。

技术实现思路

1、本发明的目的在于:克服现有技术的不足,提供一种用于flash冗余修复的地址译码控制电路,通过增加对字线地址译码器实施控制的电路结构,实现屏蔽存在缺陷存储单元的标准字线,同时利用冗余字线进行替换修复,完成修复后的存储器能够正常使用,从而显著提高flash存储器的成品率。

2、本发明的上述目的主要是通过如下技术方案予以实现的:

3、一种用于flash冗余修复的地址译码控制电路,包括:字线地址译码控制电路和字线冗余替换修复电路;字线地址译码控制电路对有缺陷存储单元的标准字线进行屏蔽,同时字线冗余替换修复电路利用冗余字线对被屏蔽的标准字线进行替换修复,完成对有缺陷存储单元的存储器的修复。

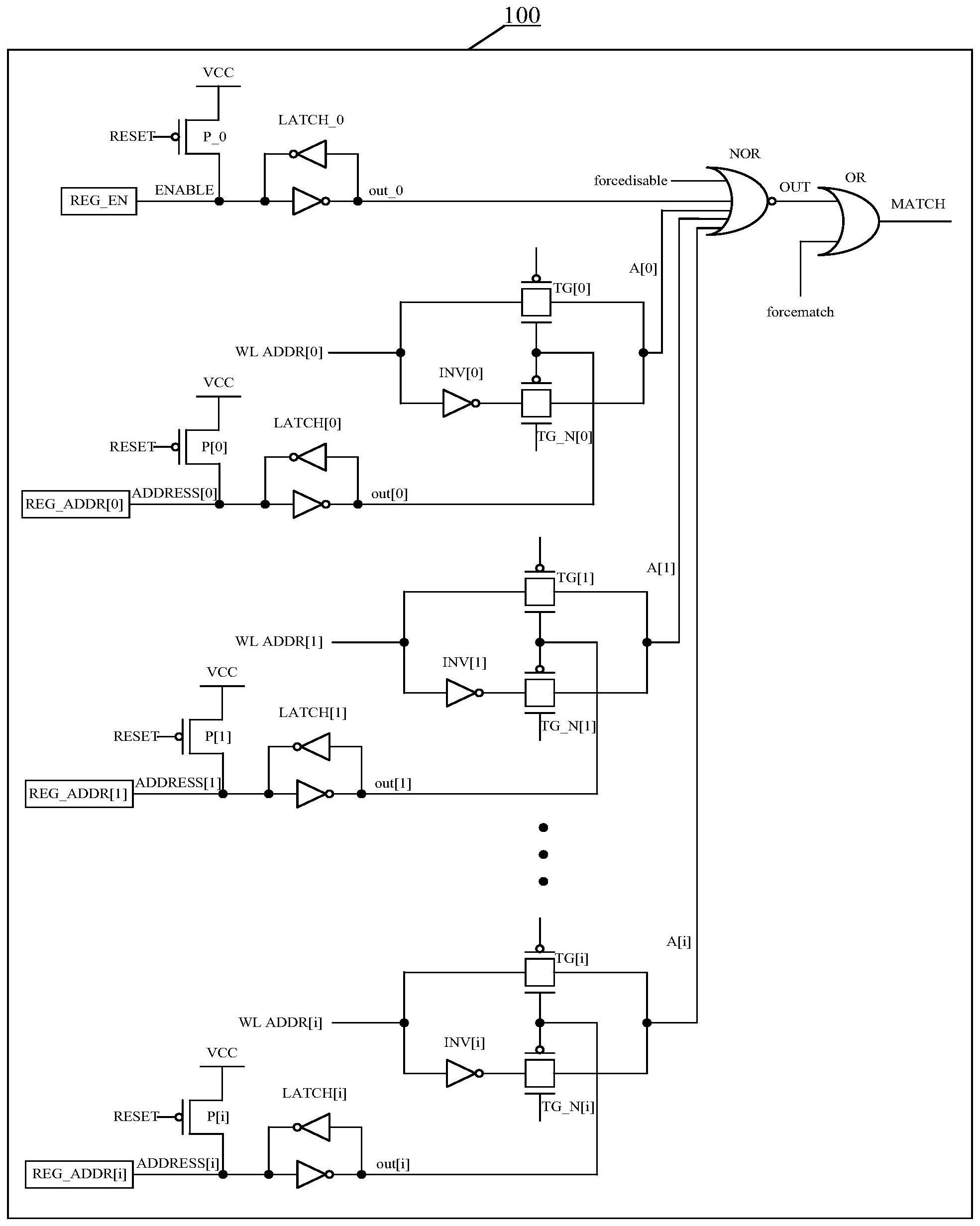

4、进一步的,所述字线地址译码控制电路包含一个使能寄存器reg_en、若干个地址寄存器reg_addr[0:i]、若干个pmos晶体管p_0和p[0:i]、若干个锁存器latch_0和latch[0:i]、若干个反相器inv[0:i]、若干个传输门tg[0:i]和tg_n[0:i];

5、所述一个使能寄存器reg_en用于使能字线地址译码控制电路来对存在缺陷存储单元的标准字线进行屏蔽以及冗余替换;所述若干个地址寄存器reg_addr[0:i]用于存储一个有缺陷存储单元的标准字线的地址;

6、所述若干个pmos晶体管p_0和p[0:i]、若干个锁存器latch_0和latch[0:i]用于将使能寄存器reg_en中信号enable和地址寄存器reg_addr[0:i]中信号address[0:i]传送至锁存器latch_0和latch[0:i],并锁存为反相信号out_0和out[0:i];

7、所述若干个反相器inv[0:i]、传输门tg[0:i]和tg_n[0:i]用于根据信号out[0:i]控制传输门开关,将输入字线地址wl addr[0:i]信号或其反相信号输出为a[0:i]信号。

8、进一步的,所述字线地址译码控制电路还包含一个nor门和一个or门;所述nor门输入forcedisable信号、out_0信号和a[0:i]信号,输出out信号;

9、所述or门输入out信号和forcematch信号,输出match信号;

10、所述forcedisable信号为高且所述forcematch信号为低时match信号被强制置为低,所述forcematch信号为高时match信号被强制置为高。

11、进一步的,使能寄存器reg_en中存储信号enable为所述字线地址译码控制电路的使能信号,地址寄存器reg_addr[0:i]中存储信号address[0:i]为一个有缺陷存储单元的标准字线的地址。

12、进一步的,上电时,初始reset信号置为低,pmos晶体管p_0和p[0:i]开启,复位锁存器latch_0和latch[0:i];

13、之后reset信号置为高,pmos晶体管p_0和p[0:i]关闭,使能寄存器reg_en和地址寄存器reg_addr[0:i]中存储的enable信号和address[0:i]信号传送至锁存器latch_0和latch[0:i],并锁存为反相信号out_0和out[0:i]。

14、进一步的,out[0:i]信号控制传输门tg[0:i]和tg_n[0:i]开关,将输入字线地址信号wl addr[0:i]通过tg[0:i]输出为a[0:i]信号,或将wl addr[0:i]经过反相器inv[0:i]的反相信号通过tg_n[0:i]输出为a[0:i]信号;

15、在address[a]信号为高的情况下,tg[a]关闭,tg_n[a]打开,当wl addr[a]信号为高时通过inv[a]后输出的a[a]信号为低,表示输入字线地址和地址寄存器中存储的有缺陷存储单元的标准字线地址相同,反之a[a]信号为高,表示两个地址不相同;

16、在address[a]信号为低的情况下,tg[a]打开,tg_n[a]关闭,当wl addr[a]信号为低时输出的a[a]信号为低,表示输入字线地址和地址寄存器中存储的有缺陷存储单元的标准字线地址相同,反之a[a]信号为高,表示两个地址不相同。

17、进一步的,out_0信号、a[0:i]信号和forcedisable信号共同输入nor门,当全部信号都为低时nor门输出的out信号为高,否则out信号为低;out信号和forcematch信号共同输入or门,当两个信号都为低时or门输出的match信号为低,否则match信号为高;当forcedisable信号为高且forcematch信号为低时match信号被强制置为低,当forcematch信号为高时match信号被强制置为高。

18、进一步的,所述字线冗余替换修复电路包括一个nor门、一个字线地址译码器wldec、若干个字线驱动wldr、若干个冗余字线rwl[0:m]以及若干个标准字线wl[0:n];

19、所述nor门由所述若干个字线地址译码控制电路输出的match[0:m]信号共同输入,nor门输出标准字线屏蔽信号disable;

20、所述一个字线地址译码器wl dec由输入字线地址wl addr[0:i]和所述标准字线屏蔽信号disable控制,对所述标准字线wl[0:n]进行屏蔽或正常译码;

21、所述冗余字线rwl[0:m]用于替换修复标准字线wl[0:n]中的有缺陷存储单元的字线。

22、所述若干个字线驱动wldr的输入为字线地址译码器wl dec输出的信号或字线地址译码控制电路输出的match[0:m]信号,用于输出驱动标准字线wl[0:n]或冗余字线rwl[0:m]所需的电压。

23、进一步的,所有字线地址译码控制电路输出的match[0:m]信号一起输入nor门,nor门输出标准字线屏蔽信号disable;输入字线地址wl addr[0:i]和标准字线屏蔽信号disable被传送至字线地址译码器wl dec;

24、当所有match[0:m]信号均为低时,nor门输出的disable信号为高,字线地址译码器wl dec输出信号为正常译码信号,与之相连接的所有标准字线不被屏蔽;

25、当某个字线地址译码控制电路输出的match[b]信号为高时,nor门输出的disable信号为低,字线地址译码器wl dec输出信号为低,与之相连接的所有标准字线被屏蔽。

26、进一步的,每一个字线地址译码控制电路连接一个冗余字线,控制是否用其替换修复标准字线;

27、当所有字线地址译码控制电路中的使能寄存器reg_en中存储信号都为低时,输出的match[0:m]信号均为低,不选中任何一个冗余字线来替换修复标准字线;

28、当某个与冗余字线rwl[b]相连接的字线地址译码控制电路中的使能寄存器reg_en中存储信号为高,且地址寄存器reg_addr[0:i]中存储信号为有缺陷存储单元的标准字线wl[c]的地址时,表示利用冗余字线rwl[b]替换修复标准字线wl[c];此时当输入的字线地址wl addr[0:i]与地址寄存器reg_addr[0:i]中存储的地址wl[c]相同时,字线地址译码控制电路输出的match[b]信号为高,与之相连接的冗余字线rwl[b]被选中,其余冗余字线不被选中。

29、本发明与现有技术相比的有益效果是:

30、本发明在flash存储器中传统字线地址译码器的基础上增加了一种用于冗余修复的地址译码控制电路,通过此控制电路输出信号match[0:m]能够控制屏蔽有缺陷存储单元的标准字线,同时选中对应的冗余字线对被屏蔽的标准字线进行替换修复,全部生产过程中造成的缺陷存储单元都被成功替换修复后,存储器可以正常使用。本发明提供的一种用于flash冗余修复的地址译码控制电路能够显著提高存储器的成品率。

- 还没有人留言评论。精彩留言会获得点赞!