半导体器件的失效分析方法及系统与流程

本发明涉及半导体技术中快闪存储器,特别涉及一种半导体器件的失效分析方法及系统。

背景技术:

1、通常,用于存储数据的半导体存储器分为易失性存储器和非易失性存储器,易失性存储器在电源中断时易于丢失数据,而非易失性存储器在电源关闭后仍可及时保存存储器内部信息。闪存是一种长寿命的非易失性存储器,数据删除是以固定的扇区为单位进行。

2、具体的,用于存储数据的半导体存储器通常形成在晶圆上,芯片在生产过程中包括多个工艺步骤,各工艺步骤形成对应的工艺层,在各工艺层之后通常会进行缺陷检测。

3、通常,在检测到缺陷之后,还需要对缺陷进行分类,这样能够方便对异常机台进行调查以及能辅助良率分析。在现有的失效分析过程中,往往需要通过各种电性测试和物理切片定位来锁定工艺缺陷导致的低良问题。而具体对于flash产品,产线存在很多工艺缺陷类型(金属桥连,栅极层短接,ct孔被阻挡等),如果还是利用现有技术中所采用的利用电性测试和物理切片定位来锁定工艺缺陷,则势必导致缺陷定位效率低、晶圆报废率高的问题。

技术实现思路

1、本发明的目的在于提供一种半导体器件的失效分析方法及系统,以解决利用现有技术中所采用的利用电性测试和物理切片定位来锁定工艺缺陷,则势必导致缺陷定位效率低、晶圆报废率高的问题。

2、第一方面,为解决上述技术问题,本发明提供一种半导体器件的失效分析方法,其中,所述半导体器件包含数据存储阵列,所述数据存储阵列包括多个扇区,每个所述扇区包含多个存储单元。

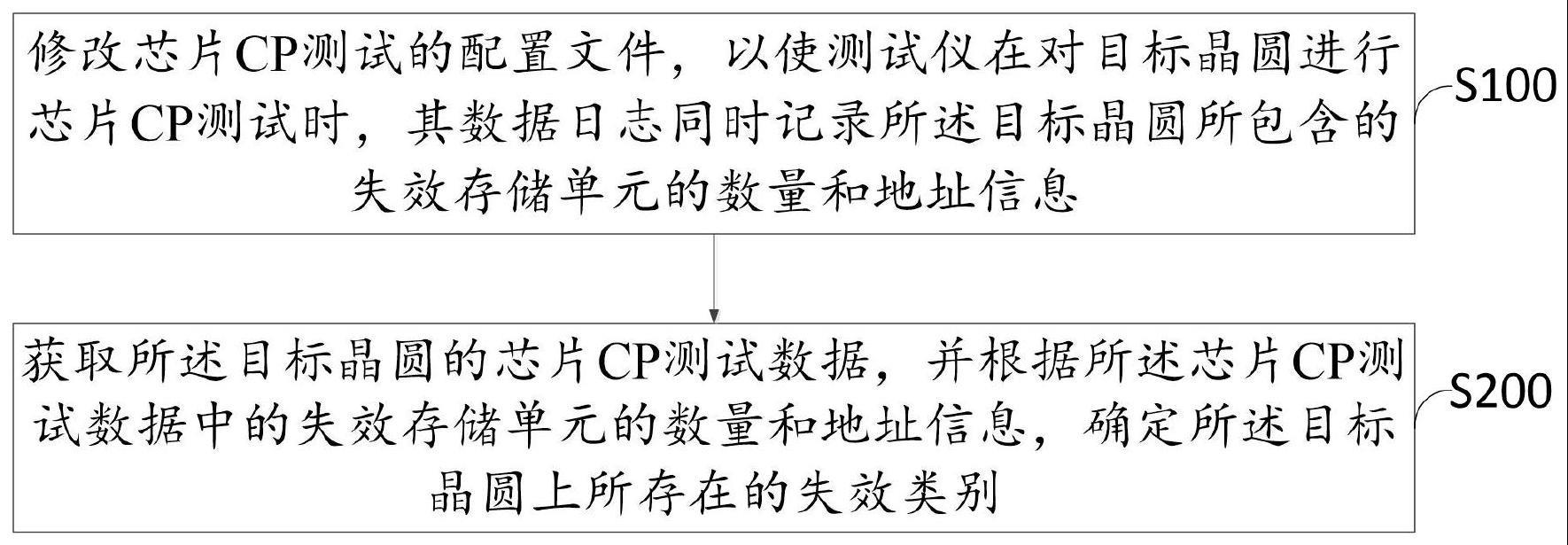

3、具体的,本发明所提供的所述失效分析方法至少可以包括如下步骤:

4、修改芯片cp测试的配置文件,以使测试仪在对目标晶圆进行芯片cp测试时,其数据日志同时记录所述目标晶圆所包含的失效存储单元的数量和地址信息;

5、获取所述目标晶圆的芯片cp测试数据,并根据所述芯片cp测试数据中的失效存储单元的数量和地址信息,确定所述目标晶圆上所存在的失效类别和失效位置。

6、进一步的,在修改芯片cp测试的配置文件之后,且在获取所述目标晶圆的芯片cp测试数据之前,本发明所提供的所述失效分析方法还可以包括:对所述目标晶圆进行芯片cp测试的步骤。

7、进一步的,在获取所述目标晶圆的芯片cp测试数据之后,本发明所提供的所述失效分析方法还包括如下步骤:

8、通过对所述获取的失效存储单元的数量和地址进行分析,提炼出所述失效存储单元的地址规律,并建立经验失效模型数据库,其中,所述经验失效模型数据库包含晶圆的失效存储单元的地址规律与失效类别的对应关系。

9、进一步的,根据所述芯片cp测试数据中的失效存储单元的数量和地址信息,确定所述目标晶圆上所存在的失效类别的步骤,具体可以包括:

10、将所述失效存储单元的数量和地址信息,自动与所述经验失效模型数据库中的信息进行对比,以在所述经验失效模型数据库中查找是否存在该地址信息所对应的地址规律;

11、若存在,则根据所述经验失效模型数据库中所包含的对应关系,确定出所述目标晶圆上的失效存储单元的失效类别。

12、更进一步的,本发明所提供的所述失效分析方法还可以包括如下步骤:

13、若所述经验失效模型数据库不存在获取的所述失效存储单元的地址信息所对应的对应关系,则对所述失效存储单元进行efa和/或pfa分析,以确定该失效存储单元的失效类别,并总结该失效存储单元的失效类别与地址信息的规律,并将该总结后的信息更新至所述经验失效模型数据库中。

14、进一步的,所述失效类别具体可以包括控制栅短接、字线/控制栅的引出金属线短接、位线的引出金属线短接、源线接触不良以及金属插塞接触不良中的至少一种。

15、进一步的,若获取的所述失效存储单元的地址信息只包含同一扇区的多行行地址失效,则该失效存储单元的失效类别为控制栅短接。

16、进一步的,若获取的所述失效存储单元的地址信息可以包含属于不同扇区的相邻两行行地址失效,则该失效存储单元的失效类别具体为字线/控制栅的引出金属线短接。

17、进一步的,若获取的所述失效存储单元的地址信息具体为成对共源线的地址信息或成对共位线的地址信息,则该失效存储单元的失效类别可以为源线接触不良或金属插塞接触不良。

18、进一步的,所述半导体器件可以为flash产品。

19、第二方面,在基于与上述提供的所述半导体器件的失效分析方法相同的发明构思的情况下,本发明还提供了一种半导体器件的失效分析系统,其特征在于,所述半导体器件包含数据存储阵列,所述数据存储阵列包括多个扇区,每个所述扇区包含多个存储单元,所述失效分析系统包括:

20、配置文件修改模块,用于修改芯片cp测试的配置文件,以使测试仪在对目标晶圆进行芯片cp测试时,其数据日志同时记录所述目标晶圆所包含的失效存储单元的数量和地址信息;

21、测试模块,用于对所述目标晶圆进行芯片cp测试;

22、地址信息获取模块,用于获取所述目标晶圆的芯片cp测试数据;

23、失效类别确定模块,用于根据所述芯片cp测试数据中的失效存储单元的数量和地址信息,自动与预先建立的经验失效模型数据库中的信息进行对比,以在所述经验失效模型数据库中查找是否存在该地址信息所对应的地址规律,若存在,则根据所述经验失效模型数据库中所包含的对应关系,确定出所述目标晶圆上的失效存储单元的失效类别,否则,则对所述失效存储单元进行efa和/或pfa分析,以确定该失效存储单元的失效类别,并总结该失效存储单元的失效类别与地址信息的规律,并将该总结后的信息更新至所述经验失效模型数据库中。

24、第三方面,本发明还提供了一种电子设备,具体包括处理器、通信接口、存储器和通信总线,其中,处理器,通信接口,存储器通过通信总线完成相互间的通信;

25、存储器,用于存放计算机程序;

26、处理器,用于执行存储器上所存放的程序时,实现如上所述的半导体器件的失效分析方法的方法步骤。

27、第四方面,基于相同的发明构思,本发明还提供了一种计算机可读存储介质,所述计算机可读存储介质内存储有计算机程序,所述计算机程序被一处理器执行时实现如上所述的半导体器件的失效分析方法的方法步骤。

28、与现有技术相比,本发明技术方案至少具有如下有益效果之一:

29、在本发明提供的半导体器件的失效分析方法中,其通过在对目标晶圆进行芯片cp测试之前,先修改该芯片cp测试的配置文件,从而在目标晶圆的芯片cp测试的过程中可以同时记录所述目标晶圆所包含的失效存储单元的数量和地址信息,然后,便可根据获取的目标晶圆的芯片cp测试中的地址信息等测试数据,确定出目标晶圆上所包含的失效存储单元所分别对应的失效类别和具体失效位置。

30、显然,在本发明提供的失效分析方法中,其首先实现了优化和完善芯片cp测试测试流程的功能,其次,其在芯片cp测试同时,通过收集失效存储单元的并自动比对经验数据库的方式,可以快速锁定半导体工艺的缺陷所在的工艺层次和工艺步骤,并为工艺改善指明方向,也能节省不必要的晶圆报废,即,实现了在试数据分析,识别特定规律,快速锁定工艺步骤,减少在线影响产品数量的同时,降低了人力负担(可以减少fa工程师或者外协fa切片的工作)以及物力损失(可以节省需要fa分析却不必要的晶圆报废)。

- 还没有人留言评论。精彩留言会获得点赞!