非易失性存储器的制作方法

本发明涉及一种非易失性存储器。

背景技术:

1、存在一种利用热载流子注入到晶体管中的非易失性存储器。这种类型的非易失性存储器包括作为存储元件的第一和第二晶体管,其特性在初始状态下是均匀的,并且热载流子仅注入到晶体管中的一个中以改变其特性。在此之后的读取操作中,基于当相同的栅极电压施加到第一和第二晶体管时漏极电流之间的大/小关系,读出所存储的数据“0”或“1”。例如,第一晶体管的漏极电流较小的状态(第一晶体管的特性被改变的状态)对应于数据“0”被存储的状态,而第二晶体管的漏极电流较小的状态(第二晶体管的特性被改变的状态)对应于数据“1”被存储的状态。

2、然而,在上述非易失性存储器中,所存储的数据(所存储的值)在初始状态下是不稳定的。在这种情况下,其他外围电路需要执行用于响应于所存储的数据的不稳定的过程,这从电路规模等来看可能是不方便的。提出了一种被配置为使得在初始状态下更多的漏极电流在第一和第二晶体管中的第二晶体管中流动以便防止所存储的数据在初始状态下的不稳定的非易失性存储器。在这种类型的非易失性存储器中,可以将所存储的数据被定义为在初始状态下是“0”,并且在热载流子注入到第二晶体管中之后,所存储的数据可以是“1”。

3、现有技术文献

4、专利文献

5、专利文献1:日本特开第2011-103158号公报

技术实现思路

1、发明要解决的课题

2、另一方面,通常需要减小存储元件(第一和第二晶体管)的尺寸以便减小电路的整体尺寸。当存储元件的尺寸减小时,存储元件之间的特性失配增加。实际上,为了追求均匀特性而形成的多个晶体管的特性可能变得彼此极大地偏移,并且该偏移对应于失配。这种失配会造成不便,诸如抑制数据的正确存储和读取(如稍后详细描述的)。期望开发一种几乎不受失配影响的非易失性存储器。

3、本发明的目的是提供一种几乎不受失配影响的非易失性存储器。

4、用于解决课题的手段

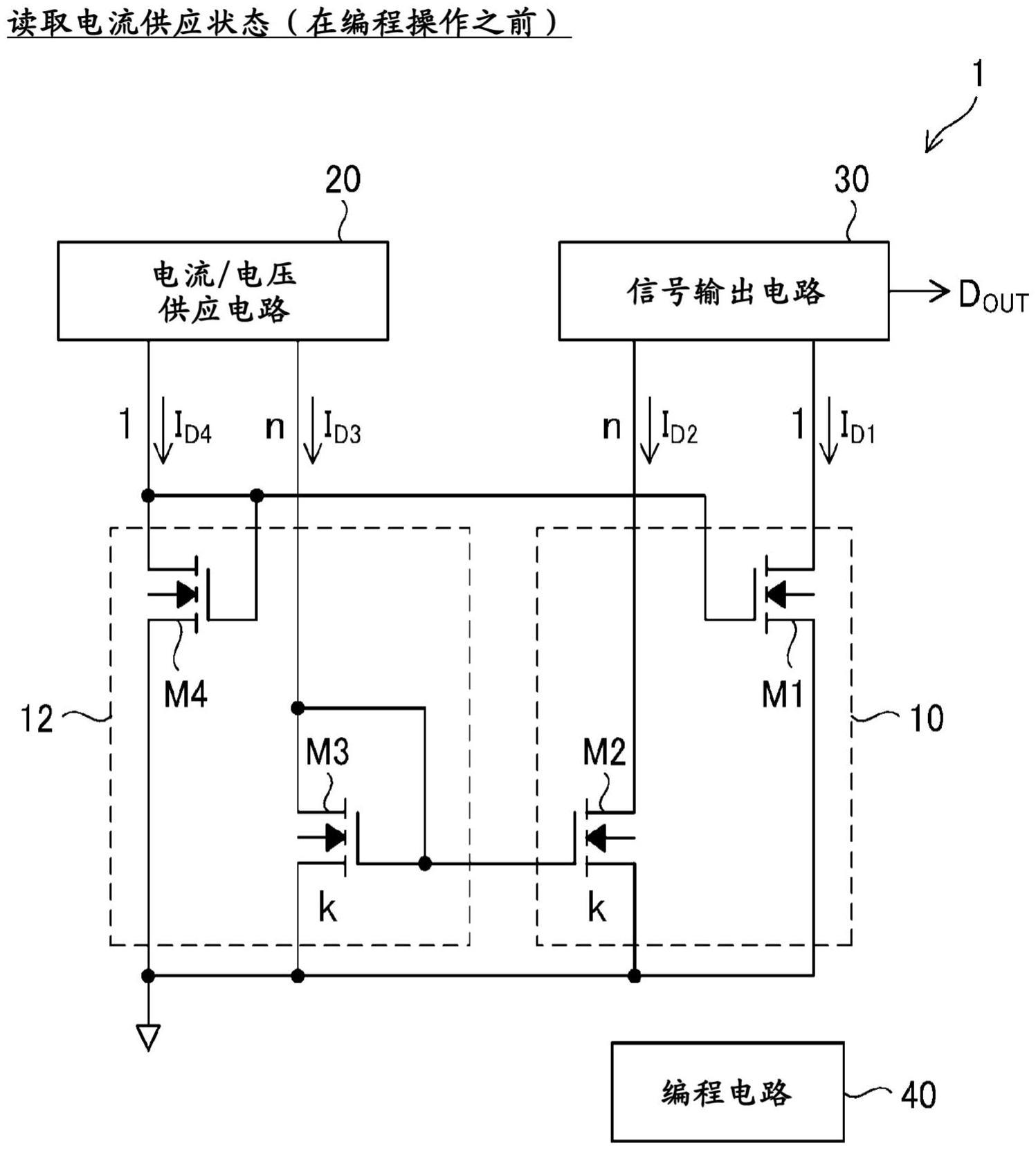

5、根据公开的非易失性存储器包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、线、供应电路和信号输出电路,所述第三晶体管具有共同连接到所述第二晶体管的栅极的栅极,所述第四晶体管具有共同连接到所述第一晶体管的栅极的栅极,所述第一至第四晶体管的源极共同连接到所述线,所述供应电路被配置为能够将漏极电流供应到所述第三晶体管何所述第四晶体管。在读取电流供应状态下执行读取操作,在所述读取电流供应状态下,所述供应电路供应所述第四晶体管的漏极电流,并且将比所述第四晶体管的漏极电流更大的漏极电流供应到所述第三晶体管。所述信号输出电路被配置为在所述读取操作中基于所述第一晶体管和所述第二晶体管的所述漏极电流输出与第一值相关联的信号或与第二值相关联的信号。

6、发明的效果

7、根据本公开,可以提供一种几乎不受失配影响的非易失性存储器。

技术特征:

1.一种非易失性存储器,包括:

2.根据权利要求1所述的非易失性存储器,其中所述信号输出电路被配置为在所述读取操作中,如果所述第二晶体管的所述漏极电流大于所述第一晶体管的所述漏极电流,则输出与所述第一值相关联的所述信号,并且如果所述第一晶体管的所述漏极电流大于所述第二晶体管的所述漏极电流,则输出与所述第二值相关联的所述信号。

3.根据权利要求2所述的非易失性存储器,其中

4.根据权利要求3所述的非易失性存储器,其中在所述编程操作之前执行的读取操作中,所述第三晶体管的所述漏极电流与所述第四晶体管的所述漏极电流的比率,与所述第二晶体管的所述漏极电流与所述第一晶体管的所述漏极电流的比率相同,并且所述第二晶体管的所述漏极电流与所述第一晶体管的所述漏极电流的所述比率在所述编程操作之后的读取操作中变得小于1。

5.根据权利要求3或4所述的非易失性存储器,其中

6.根据权利要求3至5中任一项所述的非易失性存储器,其中

7.根据权利要求3至5中任一项所述的非易失性存储器,其中

8.根据权利要求3至5中任一项所述的非易失性存储器,其中

9.一种非易失性存储器,包括:

技术总结

设置有其栅极彼此连接的第二和第三晶体管以及其栅极彼此连接的第一和第四晶体管。第一至第四晶体管的源极彼此连接。在漏极电流被供应给第四晶体管并且比第四晶体管的漏极电流更大的漏极电流被供应给第三晶体管的状态下执行读取操作。在读取操作中,基于第一和第二晶体管的漏极电流,输出与第一或第二值相关联的信号。

技术研发人员:竹中省治

受保护的技术使用者:罗姆股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!