用于SRAM的位单元的制作方法

本发明涉及用于静态随机存取存储器(sram)的位单元,以及用于形成此类位单元的方法。

背景技术:

1、为了提供更具面积效率的电路设计,正在开发垂直堆叠的半导体器件。一个示例是所谓的互补场效应晶体管(fet)设计,其中两个水平沟道晶体管相互堆叠在彼此上方,使得晶体管中的第一者的水平沟道被布置在晶体管中的另一者的水平沟道上方。

2、然而,垂直堆叠设计的发展给将用于互连器件和结构的电气互连结构形成为不同垂直层级带来了挑战。互连结构可以包括在不同互连层级上的水平导电路径或线以及在诸层级之间垂直延伸的通孔。

3、尽管晶体管小型化的持续进步似乎允许更小的单元设计并从而允许更密集的电路,但尺寸减小的晶体管的开发本身可能不足以实现面积高效的电路系统。的确,还需要考虑向晶体管提供信号和电力的互连结构。

技术实现思路

1、本发明的目的是提供一种用于sram的位单元,该位单元使得能够进行面积高效的电路设计。可从下文中理解其他目的或另外一些目的。

2、根据第一方面,提供了一种用于sram的位单元,该位单元包括:

3、布置在基板上的第一组晶体管和第二组晶体管,每组晶体管包括传输门(pass-gate)晶体管以及上部晶体管与下部晶体管的堆叠式互补晶体管对;

4、其中第一组的每个晶体管包括沿水平第一沟道轨迹在相应源极区和漏极区之间延伸的半导体沟道,并且第二组的每个晶体包括沿水平第二沟道轨迹在相应源极区和漏极区之间延伸的半导体沟道;

5、其中下部晶体管的半导体沟道被布置在基板上方的第一层级处,并且上部晶体管的半导体沟道被布置在第一层级上方的第二层级处;

6、其中传输门晶体管的半导体沟道被布置在第一层级或第二层级处;

7、其中每组晶体管中的下部晶体管的源极/漏极端子连接到在布置在下部晶体管下方的第一供电轨迹中延伸的相应第一电源;以及

8、其中每组晶体管中的上部晶体管的源极/漏极端子连接到在布置在上部晶体管上方的第二供电轨迹中延伸的相应第二电源。

9、根据第二方面,提供了一种用于形成用于sram的位单元的方法,包括在半导体基板上形成:

10、第一组晶体管和第二组晶体管,每组晶体管包括传输门晶体管和上部晶体管与下部晶体管的堆叠式互补晶体管对;

11、其中第一组的每个晶体管包括沿水平第一沟道轨迹在相应源极区和漏极区之间延伸的半导体沟道,并且第二组的每个晶体包括沿水平第二沟道轨迹在相应源极区和漏极区之间延伸的半导体沟道;

12、其中形成第一组晶体管和第二组晶体管包括将下部晶体管的半导体沟道布置在基板上方的第一层级处,将上部晶体管的半导体沟道布置在第一层级上方的第二层级处,并且将传输门晶体管的半导体沟道布置在第一层级或第二层级处;

13、将每组晶体管中的下部晶体管的源极/漏极端子连接到在布置在下部晶体管下方的第一供电轨迹中延伸的相应第一电源;

14、将每组晶体管中的上部晶体管的源极/漏极端子连接到在布置在上部晶体管上方的第二供电轨迹中延伸的相应第二电源。

15、本发明概念基于如下洞察:对于具有减小的单元面积的位单元设计,形成互连结构(诸如用于电源的垂直互连)可能是具有挑战性的。随着位单元的缩放,用于互连结构的可用空间相应地减小。本发明人已经认识到,通过将电源中的第一者布置在位单元上方并且将另一者布置在位单元下方,当位单元面积已经减小时,位单元也可以被高效地供电。与现有技术的设计相比,这是特别有益的,其中两个电源(即vdd和vss两者)布置在位单元的下方或顶部。在非平面位单元设计的情况下,上部晶体管将需要借助于一直延伸到上部晶体管层级的垂直互连结构来连接到电源。相应地,在电源被布置在位单元的顶部上的情况下,下部晶体管将需要借助于一直向下延伸到下部晶体管层级的垂直互连结构来连接到电源。当单元被缩放到更小的尺寸时,此类垂直互连结构被接纳在相邻的半导体沟道轨迹之间可能是具有挑战性的或者甚至是不可能的。当单元高度或相邻半导体沟道之间的水平间距减小时,用于形成垂直互连的可用空间相应地减小,最终冒着在位单元的不同垂直层级之间平衡电阻的捷径和困难的风险。通过改为将电源中的一者布置在位单元上方以使得上部晶体管可以从上方连接而下部晶体管可以从下方连接,可以减少延伸通过一个晶体管层级以达到该堆叠的另一晶体管层级(例如将上部晶体管连接到布置在位单元下方的电力轨)的垂直互连结构的数量,从而节省了空间以供用于其他垂直互连和减小的沟道轨迹间距。

16、当减小沟道轨迹之间的间距时,可以形成垂直互连的精度有可能成为决定沟道轨迹之间的最小可能间距的限制因素。形成垂直互连的精度尤其取决于可用的图案化技术的精度和用于限定其中要形成互连的沟槽的蚀刻工艺的选择性。光刻图案化工艺中的重叠和对准误差需要如下尺寸裕度:该尺寸裕度有阻碍沟道轨迹之间的间距减小到更小的尺寸的风险。此外,通过从上方连接上部晶体管,可以降低用于连接晶体管的垂直互连的长度,从而便于所述互连的加工。

17、互补晶体管对可以包括具有相反沟道类型的一对晶体管,即n型晶体管和p型晶体管。第一和第二互补晶体管对可以被配置成相应的反相器对。双反相器对通过交叉耦合触点一起形成一对交叉耦合的反相器。

18、每个互补晶体管对的晶体管中的一者可以被配置成上拉晶体管,并且该对中的另一晶体管可以被配置成下拉晶体管。晶体管的名称“上拉”、“下拉”或“传输”在本文中应解释为所述晶体管被适配成在(cmos)反相器或sram位单元的传统理解的上下文中作为上拉、下拉或传输晶体管来起作用或工作。

19、晶体管可以是场效应晶体管(fet)。第一互补晶体管对可以相应地包括第一cmos对,即第一nfet(即,n型fet)和第一pfet(即,p型fet)。相应地,第二互补晶体管对可以包括第二cmos对。第一和第二传输晶体管可以各自是nfet或pfet。

20、每个晶体管包括沿着沟道轨迹(或者在晶体管是诸如鳍式fet之类的基于鳍的晶体管的情况下是鳍轨迹)延伸的半导体沟道。取决于位单元的特定布局,晶体管中的两者或更多者可以具有沿着同一轨迹延伸的沟道。因此,轨迹或沟道轨迹可以被定义成水平几何线,晶体管的沟道沿着该水平几何线形成并与其平行。

21、此外,将理解,本发明概念可应用于非平面或堆叠式的位单元设计以及平面位单元设计。

22、相对空间术语,诸如“垂直”、“上部”、“下部”“堆叠在……顶部”,在本文中被理解为表示相对于基板的法线方向的位置或方向,或者等效地相对于器件层堆叠的自下而上的方向。相应地,诸如“横向”和“水平”等术语应理解成平行于基板的位置或方向,即平行于基板的上表面或主延伸平面。

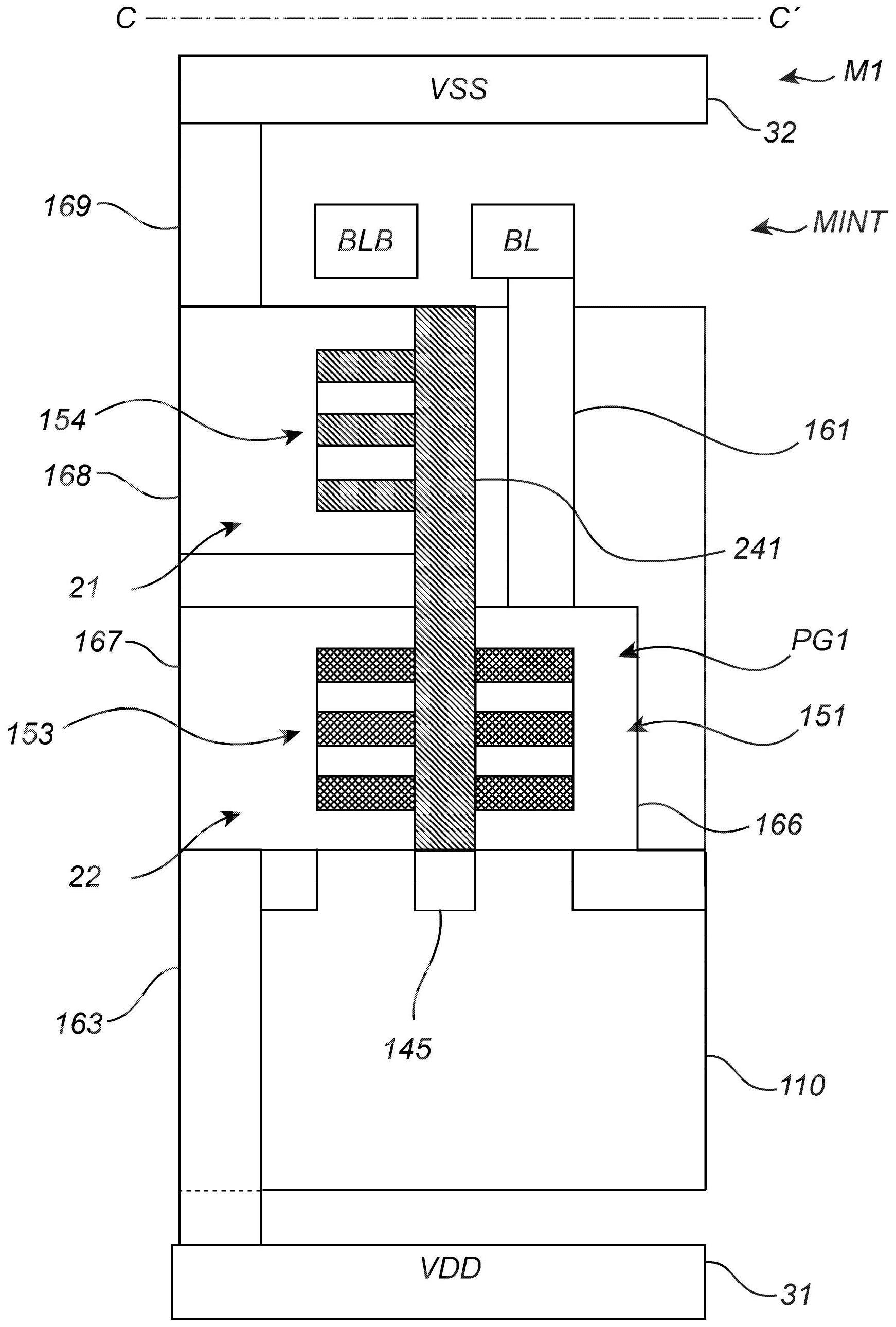

23、第二电源轨迹可以被布置在与字线相同的垂直层级处,字线与位线一起可以被用于从单元读取信息或向单元写入信息。优选地,字线和第二电源可被布置在金属层(m1)中,该金属层布置在容纳位线的局部互连层(mint)上方。换言之,字线和电源可以与位线在垂直上分隔开以节省水平方向上的空间,并允许具有减小的电路面积的更紧凑的单元设计。

24、在一些实施例中,字线可以通过局部互连(诸如通孔连接)来连接到每个传输门晶体管的相应栅极。此外,第一组晶体管中的传输门晶体管的源极/漏极端子可以连接到第一位线(bl),并且第二组晶体管的传输门晶体管的源极-漏极端子可连接到第二位线(blb)。

25、在一些实施例中,第一电源被形成为埋入式电力轨。可以通过在下部晶体管下方的位置处将凹槽或沟槽蚀刻到基板中,并用导电材料填充凹槽或沟槽来形成埋入式电力轨。可以提供诸如硅通孔(tsv)之类的通孔连接以将电源连接到下部晶体管。

26、在一些实施例中,位单元还包括形成第一组晶体管的互补晶体管对的半导体沟道的公共栅极电极的第一反相器栅极电极,以及形成第二组晶体管的互补晶体管对的半导体沟道的公共栅极电极的第二反相器栅极电极。第一和第二反相器栅极电极在横向于沟道轨迹的相应水平栅极轨迹中延伸。此外,位单元包括形成第一传输门晶体管的栅极并与第一反相器栅极电极对准的第一传输栅极电极,以及形成第二传输门晶体管的栅极并与第二反相器栅极电极对准的第二传输栅极电极。为了允许进一步减小相邻沟道轨迹之间的间距并因此减小单元高度,可以提供介电壁以将栅极结构彼此分隔开。与通过栅极切割形成栅极电极的常规技术相比,介电壁的使用是特别有益的,在常规技术中,连续的栅极电极被蚀刻并拆分成彼此分隔开的两个分开的电极。当减小沟道轨迹之间的间距时,可以执行栅极切割的精度有可能成为决定沟道轨迹之间的最小可能间距的限制因素。栅极切割的精度尤其取决于可用图案化技术的精度和所使用的蚀刻工艺的选择性。光刻图案化工艺中的重叠和对准误差需要如下尺寸裕度:该尺寸裕度有阻碍沟道轨迹之间的间距减小到更小的尺寸的风险。发明人已经认识到,通过用可以在栅极电极之前形成的介电壁代替栅极切割,两个对准的栅极电极的端部可以以更紧密的间距分隔开,这本来是可能的。由于分隔壁的厚度可以比栅极切割工艺中涉及的光刻图案化和蚀刻更容易且更精确地控制,因此可以减少提供栅极电极分隔所需的空间和裕量。

27、将明白,栅极电极中的两者或更多者(例如,反相器栅极电极和传输栅极电极)可以沿着同一栅极轨迹延伸。因此,栅极轨迹可被定义成水平几何线,栅极电极沿着该水平几何线延伸并平行于该水平几何线。优选地,栅极轨迹与沟道轨迹正交。

28、由于第一反相器栅极电极形成用于第一对互补晶体管的半导体沟道的公共栅极电极,所以第一反相器栅极电极可以被配置成控制第一对互补晶体管的两个半导体沟道的导电性。第一反相器栅极电极可以部分地或完全地包围第一对互补晶体管的半导体沟道。

29、由于第二反相器栅极电极形成用于第二对互补晶体管的半导体沟道的公共栅极电极,所以第二反相器栅极电极可以被配置成控制第二对互补晶体管的两个半导体沟道的导电性。第二反相器栅极电极可以部分地或完全地包围第二对互补晶体管的半导体沟道。

30、由于第一传输栅极电极形成用于第一传输门晶体管的半导体沟道的栅极,所以第一传输栅极电极可以被配置成控制第一传输门晶体管的半导体沟道的导电性。第一传输栅极电极可以部分地或完全地包围第一传输门晶体管沟道。

31、由于第二传输栅极电极形成用于第二传输门晶体管的半导体沟道的栅极,所以第二传输栅极电极可以被配置成控制第二传输门晶体管的半导体沟道的导电性。第二传输栅极电极可以部分地或完全地包围第二传输门晶体管沟道。

32、在一些实施例中,第一介电壁和第二介电壁可以在第一层级和第二层级之间垂直延伸,并且在互补晶体管的垂直堆叠之间水平延伸。绝缘壁的存在也在垂直布局中提供了传输栅极电极和反相器栅极电极之间的电分离,从而允许相邻沟道轨迹之间的间距进一步减小。归因于位单元的垂直布局,第一和第二介电壁可以形成公共壁,即形成同一壁结构的一部分。

33、位单元的本发明配置允许具有10纳米(nm)或更小,诸如8nm或更小的厚度的介电壁。

34、在一些示例中,每个晶体管的半导体沟道可以由相应的鳍部分形成。此类结构也可以被称为细长层堆叠,其纵向尺寸在沟道轨迹中沿着基板定向并从基板垂直突出。此外,一个或多个晶体管的半导体沟道可以有利地形成在一个或多个水平半导体纳米线中。栅极电极可以相应地被配置成完全包围/包裹相应的一个或多个纳米线的沟道区的全环绕栅极电极。水平半导体纳米线在此可以指沿着基板水平延伸并悬置在基板上方的半导体结构。纳米线可以形成具有闭合的周向延伸的边界表面的半导体主体。各种稍后的纵横比是可能的,诸如接近一的宽高比,或者大于一(诸如水平取向的纳米片半导体结构)或小于一(诸如垂直取向的纳米片)的宽高比。晶体管的源极区和漏极区也可以形成在纳米线的相对端。晶体管的源极和漏极触点可以完全包围/包裹相应的一个或多个纳米线的源极区和漏极区。

35、介电壁可以通过在由布置在相邻鳍部或细长层堆叠上的侧壁间隔物限定的间隙中沉积介电材料来形成,如将参考附图进一步详细讨论的。这允许介电壁的厚度由侧壁间隔物的厚度限定,并且侧壁在鳍之间自对准。

- 还没有人留言评论。精彩留言会获得点赞!