半导体存储装置的制作方法

本发明的实施方式涉及半导体存储装置。

背景技术:

1、作为半导体存储装置,已知有nand型闪存。

技术实现思路

1、在本发明的一实施方式中,能够提供可抑制芯片面积的增加的半导体存储装置。

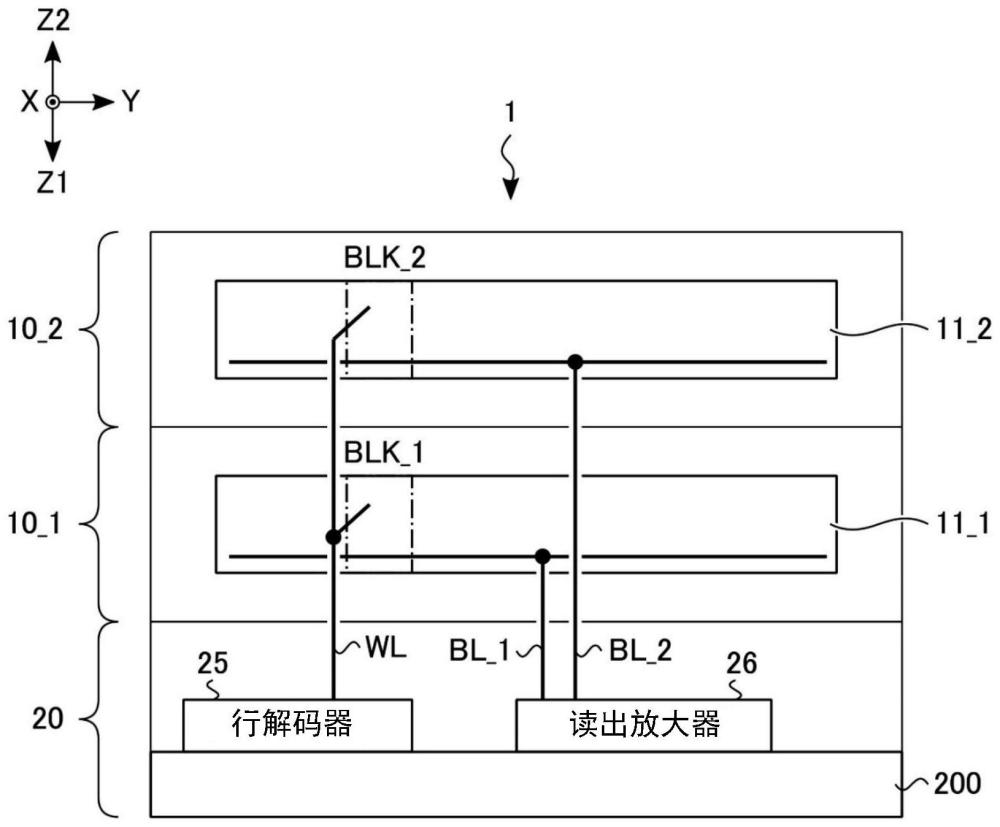

2、实施方式的半导体存储装置具备:第一芯片,具有包含第一存储器单元的第一存储器单元阵列;第二芯片,具有包含第二存储器单元的第二存储器单元阵列;以及第三芯片,包含行解码器以及读出放大器。第一存储器单元以及第二存储器单元经由字线共通地连接到行解码器。第一存储器单元经由第一位线连接于读出放大器。第二存储器单元经由第二位线连接于读出放大器。读出放大器包含能够电连接于第一位线以及第二位线的第一节点,基于第一节点的第一电压,读出第一存储器单元以及第二存储器单元的数据。

技术特征:

1.一种半导体存储装置,具备:

2.根据权利要求1所述的半导体存储装置,

3.根据权利要求2所述的半导体存储装置,

4.根据权利要求3所述的半导体存储装置,

5.根据权利要求2所述的半导体存储装置,

6.根据权利要求5所述的半导体存储装置,

7.根据权利要求1所述的半导体存储装置,

8.根据权利要求7所述的半导体存储装置,

9.根据权利要求1所述的半导体存储装置,

10.根据权利要求9所述的半导体存储装置,

11.根据权利要求1所述的半导体存储装置,

12.根据权利要求1所述的半导体存储装置,

13.根据权利要求1所述的半导体存储装置,

14.根据权利要求1所述的半导体存储装置,

15.根据权利要求14所述的半导体存储装置,

16.根据权利要求1所述的半导体存储装置,

17.根据权利要求1所述的半导体存储装置,

18.一种半导体存储装置,具备:

19.根据权利要求18所述的半导体存储装置,

20.根据权利要求19所述的半导体存储装置,

技术总结

提供能够抑制芯片面积的增加的半导体存储装置。根据实施方式,半导体存储装置具备:第一芯片(10_1),具有包含第一存储器单元(MC)的第一存储器单元阵列(11_1);第二芯片(10_2),具有包含第二存储器单元(MC)的第二存储器单元阵列(11_2);以及包含行解码器(25)以及读出放大器(26)的第三芯片(20)。第一存储器单元及第二存储器单元经由字线(WL)共通地连接到行解码器。第一存储器单元经由第一位线(BL_1)连接于读出放大器。第二存储器单元经由第二位线(BL_2)连接于读出放大器。读出放大器包含能够电连接于第一位线及第二位线的第一节点(SEN),基于第一节点的第一电压读出第一存储器单元及第二存储器单元的数据。

技术研发人员:前岛洋

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!