半导体器件和包括该半导体器件的电子系统的制作方法

本发明构思涉及半导体器件和包括该半导体器件的电子系统,更具体地,涉及包括非易失性垂直存储器件的半导体器件和包括该半导体器件的电子系统。

背景技术:

1、在需要数据存储的电子系统中,可能需要能够存储高容量数据的半导体器件,因此,正在研究增加半导体器件的数据存储容量的技术。例如,作为用于增加半导体器件的数据存储容量的技术之一,已经提出了包括具有三维布置的存储单元而不是二维布置的存储单元的垂直存储器件的半导体器件。

技术实现思路

1、本发明构思提供了一种半导体器件,其具有可以通过有效地利用当堆叠的字线的数量增加时产生的空闲空间而有助于提高半导体器件的集成度的结构。这可以提高具有三维布置的存储单元的半导体器件中的集成度。

2、本发明构思还提供了一种包括半导体器件的电子系统,该半导体器件具有可以通过有效地利用当堆叠的字线的数量增加时产生的空闲空间而有助于提高半导体器件的集成度的结构。这可以提高具有三维布置的存储单元的半导体器件中的集成度。

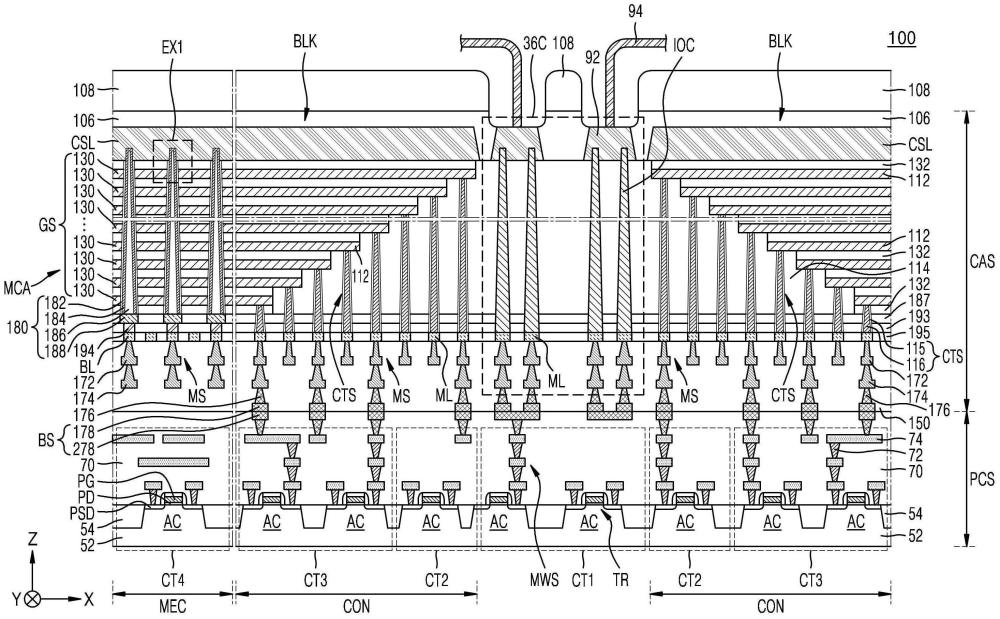

3、根据本发明构思的一方面,提供了一种半导体器件,其包括:外围电路结构,包括多个电路区;单元阵列结构,包括一对存储单元块,所述一对存储单元块在第一方向上与外围电路结构重叠,并且在垂直于第一方向的第二方向上间隔开,外围电路连接区在其间,其中所述多个电路区中的第一电路区在第一方向上与外围电路连接区重叠;以及至少一个接触插塞,从外围电路连接区在第一方向上延伸,并且包括第一端部和第二端部,第一端部配置为连接到包括在第一电路区中的至少一个电路并且面对第一电路区,第二端部配置为连接到外部连接端子。

4、根据本发明构思的另一方面,提供了一种半导体器件,其包括:外围电路结构;以及单元阵列结构,在第一方向上与外围电路结构重叠,其中外围电路结构包括数据输入/输出电路区,数据输入/输出电路区从外围电路结构在第二方向上的中心区域沿与第二方向正交的第三方向延伸,第一方向与第三方向和第二方向正交,其中单元阵列结构包括:外围电路连接区,在第一方向上与数据输入/输出电路区重叠;在第二方向上间隔开的第一存储单元块和第二存储单元块,外围电路连接区在其间;以及多个接触插塞,从外围电路连接区在第一方向上延伸,并且包括第一端部和第二端部,第一端部配置为连接到包括在数据输入/输出电路区中的至少一个电路并且面对数据输入/输出电路区,第二端部配置为连接到外部连接端子。

5、根据本发明构思的另一方面,提供了一种电子系统,其包括主板、在主板上的半导体器件、以及电连接到主板上的半导体器件的控制器,其中半导体器件包括:外围电路结构,包括多个电路区;单元阵列结构,包括一对存储单元块,所述一对存储单元块在第一方向上与外围电路结构重叠,并且在垂直于第一方向的第二方向上间隔开,外围电路连接区在其间;所述多个电路区中的第一电路区,在第一方向上与外围电路连接区重叠;以及至少一个接触插塞,从外围电路连接区在第一方向上延伸,并且包括第一端部和第二端部,第一端部配置为连接到包括在第一电路区中的至少一个电路并且面对第一电路区,第二端部配置为连接到外部连接端子。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中,包括在所述第一电路区中的所述至少一个电路包括数据输入/输出电路。

3.根据权利要求1所述的半导体器件,其中,所述一对存储单元块中的每个包括:存储单元区,包括沿所述第一方向依次堆叠的多条栅极线;以及连接区,包括一体连接到所述多条栅极线的多个导电焊盘区,

4.根据权利要求1所述的半导体器件,其中,所述外围电路结构和所述一对存储单元块被包括在一个芯片中,

5.根据权利要求1所述的半导体器件,其中,所述单元阵列结构进一步包括第一接合金属焊盘,

6.根据权利要求1所述的半导体器件,其中,所述一对存储单元块中的每个包括:存储单元区,包括沿所述第一方向依次堆叠的多条栅极线;以及连接区,包括一体连接到所述多条栅极线的多个导电焊盘区,

7.根据权利要求1所述的半导体器件,进一步包括:

8.根据权利要求1所述的半导体器件,其中,所述一对存储单元块中的每个包括:存储单元区,包括沿所述第一方向依次堆叠的多条栅极线;以及连接区,包括一体连接到所述多条栅极线的多个导电焊盘区,

9.根据权利要求1所述的半导体器件,进一步包括至少一个贯穿电极,所述至少一个贯穿电极从所述外围电路连接区在所述第一方向上延伸,并且在所述第一方向上延伸到所述单元阵列结构和所述外围电路结构中。

10.根据权利要求1所述的半导体器件,其中,所述单元阵列结构进一步包括在所述一对存储单元块和所述外围电路结构之间的单元基板,

11.一种半导体器件,包括:

12.根据权利要求11所述的半导体器件,其中,所述单元阵列结构进一步包括第三存储单元块和第四存储单元块,所述第三存储单元块在所述第三方向上与所述第一存储单元块相邻,所述第四存储单元块在所述第二方向上与所述第三存储单元块间隔开且所述外围电路连接区在其间,

13.根据权利要求11所述的半导体器件,其中,所述第一存储单元块和所述第二存储单元块中的每个包括:存储单元区,包括在所述第一方向上依次堆叠的多条栅极线;以及连接区,包括一体连接到所述多条栅极线的多个导电焊盘区,

14.根据权利要求11所述的半导体器件,其中,所述单元阵列结构进一步包括多个第一接合金属焊盘,

15.根据权利要求11所述的半导体器件,其中,所述第一存储单元块和所述第二存储单元块每个包括:存储单元区,包括沿所述第一方向依次堆叠的多条栅极线;以及连接区,包括一体连接到所述多条栅极线的多个导电焊盘区,

16.根据权利要求11所述的半导体器件,进一步包括:

17.根据权利要求11所述的半导体器件,进一步包括至少一个贯穿电极,所述至少一个贯穿电极从所述外围电路连接区在所述第一方向上延伸,并且在所述第一方向上延伸到所述单元阵列结构和所述外围电路结构中。

18.根据权利要求11所述的半导体器件,其中,所述单元阵列结构进一步包括在所述第一存储单元块和所述第二存储单元块与所述外围电路结构之间的单元基板,

19.一种电子系统,包括:

20.根据权利要求19所述的电子系统,其中,所述主板进一步包括将所述半导体器件和所述控制器彼此电连接的布线图案,

技术总结

本发明提供一种半导体器件和包括该半导体器件的电子系统,该半导体器件包括:外围电路结构,包括多个电路区;单元阵列结构,包括一对存储单元块,所述一对存储单元块在第一方向上与外围电路结构重叠,并且在垂直于第一方向的第二方向上间隔开,外围电路连接区在其间,其中所述多个电路区中的第一电路区在第一方向上与外围电路连接区重叠;以及至少一个接触插塞,从外围电路连接区在第一方向上延伸,并且包括第一端部和第二端部,第一端部配置为连接到包括在第一电路区中的至少一个电路并且面对第一电路区,第二端部配置为连接到外部连接端子。

技术研发人员:权俊瑛,金志荣,金俊亨,成锡江

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!