校验子解码系统的制作方法

本公开的实施例大体上涉及数字逻辑电路,且更具体来说,涉及校验子解码系统。

背景技术:

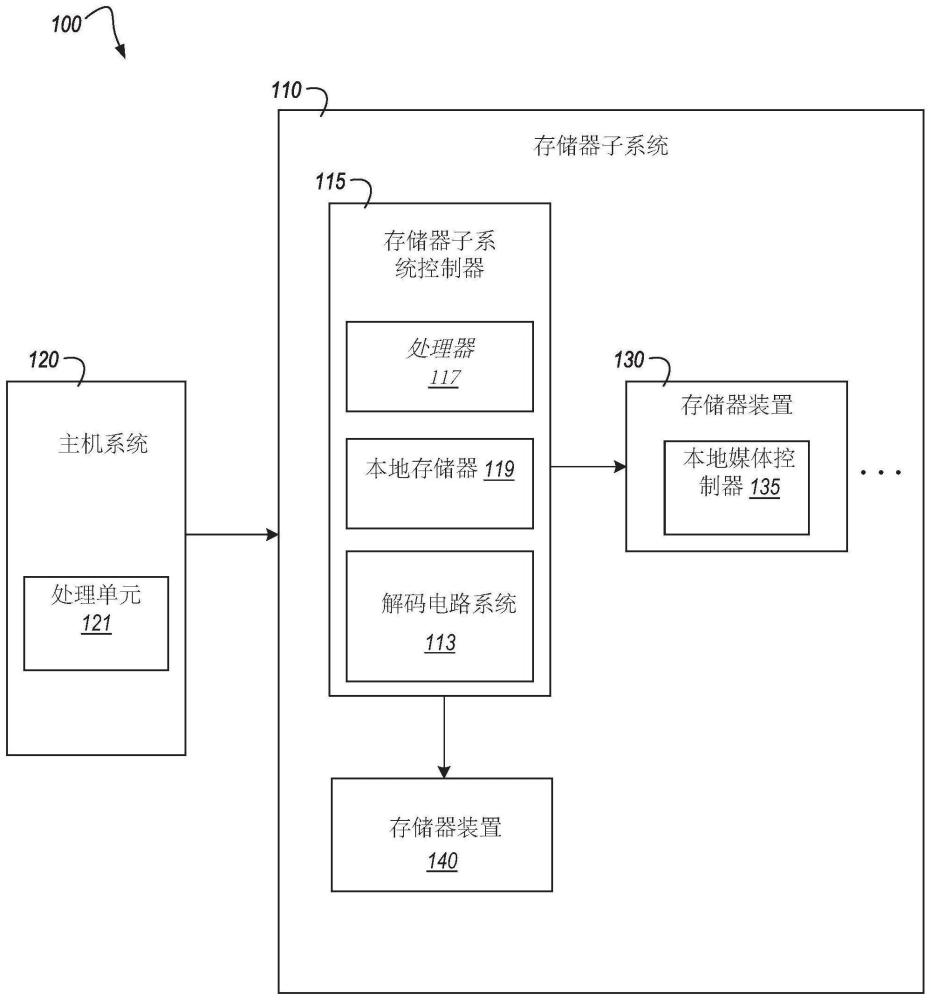

1、存储子系统可包含存储数据的一或多个存储器装置。存储器装置可为例如非易失性存储器装置及易失性存储器装置。存储器子系统可包含用以促进存储器子系统的操作的一或多个模拟及/或数字电路。通常,主机系统可利用存储器子系统来将数据存储在存储器装置处及从存储器装置检索数据。

技术实现思路

1、本公开的实施例提供一种用于校验子解码的方法,其包括:基于位串内具有逻辑值一或逻辑值零或两者的位数量来确定所述位串的错误数量;将对应于所述位串的所述错误数量的指示写入到存储器单元阵列;确定所述位串的所述错误数量已达到阈值错误数量;及响应于确定所述位串的所述错误数量已达到所述阈值错误数量而避免执行用以确定或校正所述位串的所述错误数量或既确定又校正所述位串的所述错误数量的后续操作。

2、本公开的另一实施例提供一种用于校验子解码的设备,其包括:第一存储器单元阵列,其经配置以存储各自包括多个数据位的多个校验子;第一电路系统,其耦合到所述第一阵列且经配置以基于所述校验子中的每一者内具有逻辑值一的位数量来确定所述校验子中的所述每一者内含有的错误数量;第二电路系统,其耦合到所述第一电路系统,其中所述第二电路系统经配置以对于所述校验子中的每一者:将对应于所述校验子中的所述每一者内具有所述逻辑值一的所述位数量的指示写入到第二存储器单元阵列;确定所述校验子中的至少一者的所述错误数量已达到阈值错误数量;及响应于所述确定所述校验子中的所述至少一者内含有的所述错误数量已达到所述错误数量阈而避免执行用以确定所述校验子中的所述至少一者内含有的所述错误数量的后续操作。

3、本公开的又一实施例提供一种用于校验子解码的系统,其包括:第一存储器单元阵列,其经配置以存储各自包括多个数据位的多个校验子;移位电路系统,其经配置以对于所述多个校验子中的每一者,将所述校验子中的每一者的所述多个数据位传送到耦合到所述移位电路系统的决策电路系统,其中所述决策电路系统经配置以基于所述校验子中的每一者内具有逻辑值一的位数量来确定所述校验子中的所述每一者内含有的错误数量;加法器电路系统,其耦合到所述决策电路系统,其中所述加法器电路系统经配置以:对所述校验子中的所述每一者内具有逻辑值一的所述位数量求和以产生所述校验子中的每一者的解码完成指示;且将所述校验子中的每一者的所述解码完成指示写入到第二存储器单元阵列;基于所述解码完成指示,确定所述校验子中的至少一者的所述错误数量已达到阈值错误数量,且其中所述决策电路系统经配置以响应于所述确定所述校验子中的所述至少一者含有的所述错误数量已达到所述阈值错误数量而避免执行用以确定所述校验子中的所述至少一者含有的所述错误数量的后续操作。

技术特征:

1.一种用于校验子解码的方法,其包括:

2.根据权利要求1所述的方法,其进一步包括作为用以校正所述位串内的一或多个位翻转错误的解码操作的部分,通过操作加法器电路系统(223)来确定所述位串的所述错误数量,所述加法器电路系统经配置以对所述位串内具有所述逻辑值一的所述位数量求和。

3.根据权利要求1所述的方法,其中所述位串是并行处理的多个位串中的一者,且其中所述方法进一步包括:

4.根据权利要求1所述的方法,其中在基于所述位串内具有逻辑值一的所述位数量来确定所述位串的所述错误数量之前,所述方法包括使用决策电路系统(218)确定所述位串内具有所述逻辑值一的所述位数量,此外其中,所述位串包括校验子,且所述方法进一步包括作为确定所述位串的所述错误数量的部分而对所述校验子执行解码操作。

5.一种用于校验子解码的设备(100),其包括:

6.根据权利要求5所述的设备,其中所述第二电路系统耦合到所述第一电路系统,且其中所述第二电路系统经配置以能够:

7.根据权利要求5所述的设备,其中所述第一电路系统至少包括决策电路系统(218)且其中所述第二电路系统至少包括加法器电路系统(223),所述加法器电路系统包括逻辑nand门(332)。

8.根据权利要求5所述的设备,其中所述第二电路系统耦合到所述第一电路系统,其中所述第二电路系统经配置以避免执行所述后续操作,以便减少在包括所述第一电路系统、所述第二电路系统、所述第一存储器单元阵列及所述第二存储器单元阵列的计算系统(100、201)的操作中消耗的功率量。

9.根据权利要求5所述的设备,其中:

10.根据权利要求5所述的设备,其中所述第二电路系统经配置以在以下情况下确定所述校验子中的所述至少一者的所述错误数量已达到所述阈值错误数量:

11.一种用于校验子解码的系统(100),其包括:

12.根据权利要求11所述的系统,其中所述加法器电路系统包括逻辑nand门,所述移位电路系统包括多个移位电路系统,

13.根据权利要求11所述的系统,其进一步包括耦合到所述第二存储器单元阵列的解码完成电路系统(226、228、334),其中所述解码完成电路系统经配置以响应于所述确定所述校验子中的所述至少一者内含有的所述错误数量已达到所述阈值错误数量而确定涉及所述校验子中的所述至少一者的解码操作已完成。

14.根据权利要求11所述的系统,其进一步包括耦合到所述第二存储器单元阵列的解码完成电路系统(226、228、334),其中所述解码完成电路系统经配置以响应于所述确定所述校验子中的所述至少一者内含有的所述错误数量已达到所述阈值错误数量而确定涉及所述校验子中的所述至少一者的解码操作已失败。

15.根据权利要求11所述的系统,其中所述决策电路系统经配置以:

技术总结

本公开涉及一种校验子解码系统。方法包含基于位串内具有逻辑值一的位数量来确定所述位串的错误数量,及将对应于所述位串的所述错误数量的指示写入到存储器单元阵列。所述方法可进一步包含确定所述位串的所述错误数量已达到阈值错误数量,及响应于确定所述位串的所述错误数量已达到所述阈值错误数量而避免执行用以确定所述位串的所述错误数量的后续操作。

技术研发人员:L·兹洛特尼科,E·恩·加德,F·周

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!