半导体存储装置的制作方法

本发明涉及半导体存储装置。

背景技术:

1、对于半导体存储装置,存在设置有存储容量(尺寸)不同的两种存储电路和读出放大器的类型。该读出放大器基于将各存储电路的输出信号的电压与基准电压进行比较的结果来判定由输出信号表示的位值(0、1)。

2、对于上述那样的半导体存储装置,如果通过共用的配线读取各存储电路的输出信号,则有时由于存储容量的差异而信号波形在存储电路间不同。因此,如果基于存储容量较大的存储电路设定基准电压,则例如读出放大器有可能误读取存储容量较小的存储电路的位值。

3、另一方面,如果基于存储容量较小的存储电路设定基准电压,则由于读出放大器的动作延迟,所以有可能导致位值的读取速度的下降。

技术实现思路

1、本发明要解决的课题是提供一种即使读取配线与存储容量不同的两种存储电路共同地连接,也能够在减小读取故障的同时改善读取速度的下降的半导体存储装置。

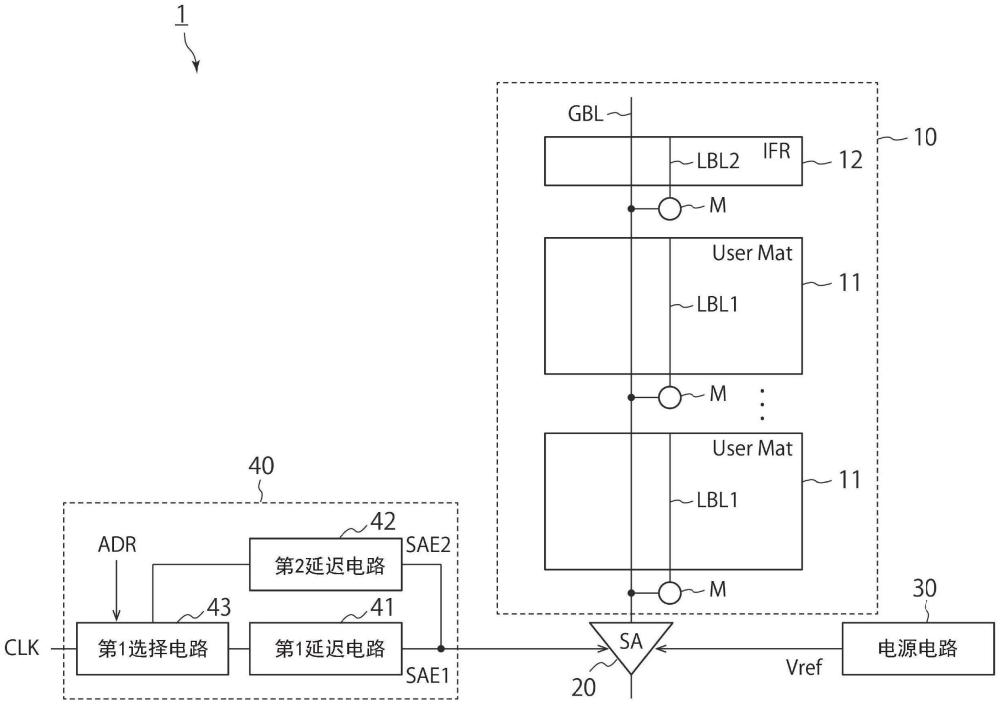

2、有关一个技术方案的半导体存储装置具有:第1存储电路;第2存储电路,存储容量比第1存储电路小;读取配线,与第1存储电路及第2存储电路共同连接;读出放大器,将从第1存储电路经由读取配线输入的第1位信号或从第2存储电路经由读取配线输入的第2位信号的电压与基准电压进行比较;以及读取调整电路,与第1位信号和第2位信号对应地,使读出放大器的动作定时或基准电压中的至少任一个变化。

技术特征:

1.一种半导体存储装置,其具有:

2.如权利要求1所述的半导体存储装置,其中,

3.如权利要求1所述的半导体存储装置,其中,

4.如权利要求1所述的半导体存储装置,其中,

5.如权利要求3所述的半导体存储装置,其中,

6.如权利要求3所述的半导体存储装置,其中,

7.如权利要求3所述的半导体存储装置,其中,

8.如权利要求3所述的半导体存储装置,其中,

9.如权利要求1所述的半导体存储装置,其中,

10.如权利要求9所述的半导体存储装置,其中,

技术总结

实施方式提供一种即使读取配线与存储容量不同的两种存储电路共同地连接,也能够在减小读取故障的同时改善读取速度的下降的半导体存储装置。有关一个实施方式的半导体存储装置具有:第1存储电路;第2存储电路,存储容量比第1存储电路小;读取配线,与第1存储电路及第2存储电路共同连接;读出放大器,将从第1存储电路经由读取配线输入的第1位信号或从第2存储电路经由读取配线输入的第2位信号的电压与基准电压进行比较;以及读取调整电路,与第1位信号和第2位信号对应地,使读出放大器的动作定时或基准电压中的至少任一个变化。

技术研发人员:绿川刚

受保护的技术使用者:株式会社东芝

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!