注错测试系统、注错测试方法及相关装置与流程

本申请涉及存储设备应用领域,特别是涉及一种注错测试系统、注错测试方法及相关装置。

背景技术:

1、掉电非易失性设备,例如:闪存设备,是用于存储数据的掉电非易失性设备。闪存(nand flash)是闪存设备的主要存储介质,由于闪存自身特性或者软件逻辑缺陷,闪存设备在使用过程中容易出现各种错误或异常。

2、闪存设备在使用过程中出现的错误包括读错误,读错误又可细分为多种类型,闪存设备针对每种类型的读错误都有相应的处理流程。由于闪存设备在正常使用过程中,很难触发到一种或多种具体类型的读错误,无法快速验证每种读错误处理流程的有效性和稳定性,因此,需要对读错误处理流程进行主动验证。目前,通常采用注入无法纠正错误模拟部分场景下产生的读错误,从而对读错误处理流程进行主动验证。

3、在实现本申请过程中,发明人发现现有技术中至少存在如下问题:读错误包括多种类型,现有技术只能注入某一特定类型的读错误,不能根据需求灵活注入不同类型的读错误,从而难以在触发读错误的所有错误路径下对各种读错误处理流程进行验证。

技术实现思路

1、本申请实施例提供一种注错测试系统、注错测试方法及相关装置,以根据注错信息灵活注入相应类型的读错误,从而能够在触发各种具体类型的读错误下对相应的读错误处理流程进行验证,提高注错测试效率。

2、本申请实施例提供以下技术方案:

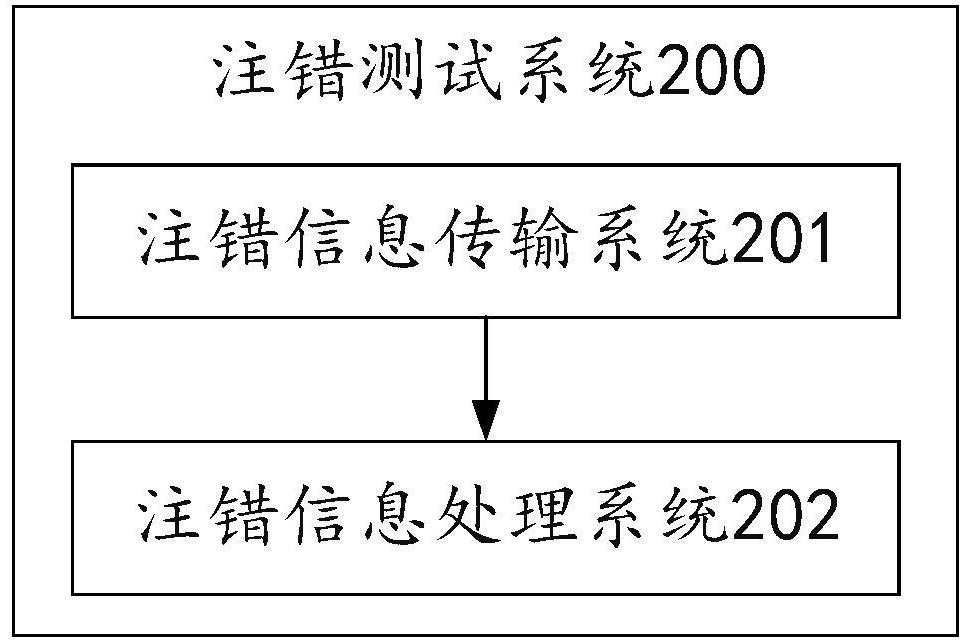

3、第一方面,本申请实施例提供一种注错测试系统,该注错测试系统包括注错信息传输系统与注错信息处理系统,其中,

4、注错信息传输系统,连接注错信息处理系统,用于在第一命令结构体的信息与注错信息匹配时,将注错信息赋予第二命令结构体,其中,注错信息包括命令错误类型,第一命令结构体与第二命令结构体不同,第一命令结构体为注错命令的结构体;

5、注错信息处理系统,连接注错信息传输系统,用于根据第二命令结构体中的注错信息注入相应类型的读错误,其中,命令错误类型与读错误均包括无法纠正错误、数据校验错误、空错误或读超时错误。

6、第二方面,本申请实施例提供一种存储控制芯片,包括:

7、如第一方面的注错测试系统。

8、第三方面,本申请实施例提供一种掉电非易失性设备,包括:

9、如第二方面的存储控制芯片;

10、至少一个掉电非易失性介质,与存储控制芯片通信连接。

11、第四方面,本申请实施例提供一种注错测试方法,应用于第三方面的掉电非易失性设备,该注错测试方法包括:

12、获取注错命令,并在注错命令为合法命令时,将注错命令存储至注错命令池,其中,注错命令包括注错信息;

13、在第一命令结构体的信息与注错命令池中的某一注错命令的注错信息匹配时,将注错信息赋予第二命令结构体,其中,第一命令结构体与第二命令结构体不同,第一命令结构体为注错命令的结构体;

14、根据第二命令结构体中的注错信息注入相应类型的读错误。

15、第五方面,本申请实施例还提供了一种非易失性计算机可读存储介质,非易失性计算机可读存储介质存储有计算机可执行指令,计算机可执行指令用于使掉电非易失性设备能够执行第四方面的注错测试方法。

16、本申请实施例的有益效果是:区别于现有技术的情况下,本申请实施例提供一种注错测试系统,该注错测试系统包括注错信息传输系统与注错信息处理系统。其中,注错信息传输系统,连接注错信息处理系统,用于在第一命令结构体的信息与注错信息匹配时,将注错信息赋予第二命令结构体,其中,注错信息包括命令错误类型,第一命令结构体与第二命令结构体不同,第一命令结构体为注错命令的结构体;注错信息处理系统,连接注错信息传输系统,用于根据第二命令结构体中的注错信息注入相应类型的读错误,其中,命令错误类型与读错误均包括无法纠正错误、数据校验错误、空错误或读超时错误。

17、通过注错信息传输系统在第一命令结构体的信息与注错信息匹配时,将注错信息赋予第二命令结构体,注错信息处理系统用于根据第二命令结构体中的注错信息注入相应类型的读错误,本申请能够在注入读错误时,根据注错信息灵活注入相应类型的读错误,从而能够在触发各种具体类型的读错误下对相应的读错误处理流程进行验证,提高注错测试效率。

技术特征:

1.一种注错测试系统,其特征在于,包括注错信息传输系统与注错信息处理系统,其中,

2.根据权利要求1所述的系统,其特征在于,所述注错测试系统还包括注错信息存储系统,所述注错信息存储系统包括注错命令池;

3.根据权利要求2所述的系统,其特征在于,所述注错测试系统应用于掉电非易失性设备;

4.根据权利要求3所述的系统,其特征在于,所述注错信息传输系统具体用于:

5.根据权利要求3所述的系统,其特征在于,所述掉电非易失性设备包括掉电非易失性介质;

6.根据权利要求5所述的系统,其特征在于,在所述第二命令结构体中的命令错误类型为无法纠正错误或数据校验错误时,所述主处理器用于:

7.根据权利要求6所述的系统,其特征在于,所述注错测试系统包括校验模块,所述校验模块用于确定是否出现读错误,以及确定出现的读错误的类型;

8.根据权利要求6所述的系统,其特征在于,所述注错测试系统包括校验模块,所述校验模块用于确定是否出现读错误,以及确定出现的读错误的类型;

9.根据权利要求5所述的系统,其特征在于,在所述第二命令结构体中的命令错误类型为空错误时,所述主处理器用于:

10.根据权利要求5所述的系统,其特征在于,在所述第二命令结构体中的命令错误类型为读超时错误时,所述主处理器用于:

11.根据权利要求10所述的系统,其特征在于,所述注错测试系统包括校验模块,所述校验模块用于确定是否出现读错误,以及确定出现的读错误的类型;

12.一种存储控制芯片,其特征在于,包括:

13.一种掉电非易失性设备,其特征在于,包括:

14.一种注错测试方法,其特征在于,应用于权利要求13所述的掉电非易失性设备,所述方法包括:

15.根据权利要求14所述的方法,其特征在于,所述注错信息包括命令错误类型,所述命令错误类型与所述读错误均包括无法纠正错误、数据校验错误、空错误和读超时错误;

技术总结

本申请实施例涉及存储设备应用领域,公开了一种注错测试系统、注错测试方法及相关装置,注错测试系统包括:注错信息传输系统,连接注错信息处理系统,用于在第一命令结构体的信息与注错信息匹配时,将注错信息赋予第二命令结构体,注错信息包括命令错误类型;注错信息处理系统,连接注错信息传输系统,用于根据第二命令结构体中的注错信息注入相应类型的读错误,命令错误类型与读错误均包括无法纠正错误、数据校验错误、空错误或读超时错误。本申请能够在注入读错误时,根据注错信息灵活注入相应类型的读错误,从而能够在触发各种具体类型的读错误下对相应的读错误处理流程进行验证,提高注错测试效率。

技术研发人员:林创龙,张文刚

受保护的技术使用者:深圳大普微电子股份有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!