一种电能表掉电数据保存电路的制作方法

本技术涉及电能表领域,具体涉及一种用于在电能表掉电时完成数据保存的电路。

背景技术:

1、大多数电能表产品有掉电后保存数据并维持时钟工作的要求。如中国南方电网单相智能电能表技术规范书中明确要求:“掉电时应将ram中需保存的数据保存到非易失性存储器中”,“电能表在标称电压加载10min后,将电能表时钟与标准时间对时,再取出时钟电池且电能表在断电、环境温度为-25℃的情况下静置2天。将时钟电池放回电能表电池仓,电能表上电后,表计时钟与标准时间比较误差不应超过5s”。

2、目前电能表在没有电池供电的情况下,一般是通过两组法拉电容来临时供电。其中一组法拉电容用于掉电数据存储,另外一组法拉电容维持时钟运行。还可以利用一组大容量的法拉电容同时确保掉电后的数据存储和时钟的运行。但无论采用两组法拉电容,还是采用单组大容量法拉电容,都必须增大电容容量,维持mcu在掉电状态下长时间运行,因此存在成本较高、占用空间大的问题。例如,公布号为cn115220962a的中国发明专利申请公开了一种基于法拉电容mcu掉电数据保存电路和方法,它采用电阻分压配合mcu采样ad值,实时检测电源电压,可程序设定电源阈值,低于阈值的电压即判断为系统异常立即进行数据保存,避免出现电源欠压无法触发系统的掉电判断。该基于法拉电容的mcu掉电数据保存电路和方法,可实现法拉电容续电可控,通过mcu控制法拉电容的续电时间,在完成掉电后的数据保存后,可控制p沟道mos管关闭,从而断开法拉电容给后端的供电,避免法拉电容持续放电后导致后续芯片欠压异常工作。然而,此控制方式需要在掉电后为mcu长时间供电,否则mcu无法维持对mos管的控制,导致mos管状态不确定,将法拉电容的电量快速消耗掉,并使后续芯片在欠压状态下工作。

3、除此之外,现有技术还提出了其它针对掉电进行数据保存的方案。例如公布号为cn105468127a的中国发明专利申请公开了一种实时数据采集系统及其掉电数据保存电路、方法。在没有掉电时,系统控制模块将实时数据采集系统的采集模块采集的实时数据保存在可移动存储装置中;在掉电时,系统控制模块通过电源切换模块将实时数据采集系统的供电切换到内置有储能电容的储能模块供电。系统控制模块读取掉电时实时时钟模块中的实时时间,将该实时时间作为掉电断点时间数据与所述采集模块在掉电时采集的断点数据一并存储到可移动存储装置中,切断所述采集模块的供电;由此,实现了数据的断电保存。但是,该方式在掉电时刻利用交流掉电检测模块与定时器模块对电源切换模块进行控制,进而在储能模块的帮助下完成掉电后的数据储存,方案设计较为复杂,需要各种逻辑芯片进行监测控制,成本较高。

技术实现思路

1、本实用新型提出了一种电能表掉电数据保存电路,其目的是:提供一种简单的掉电后数据保存方式,降低掉电数据保存的成本。

2、本实用新型技术方案如下:

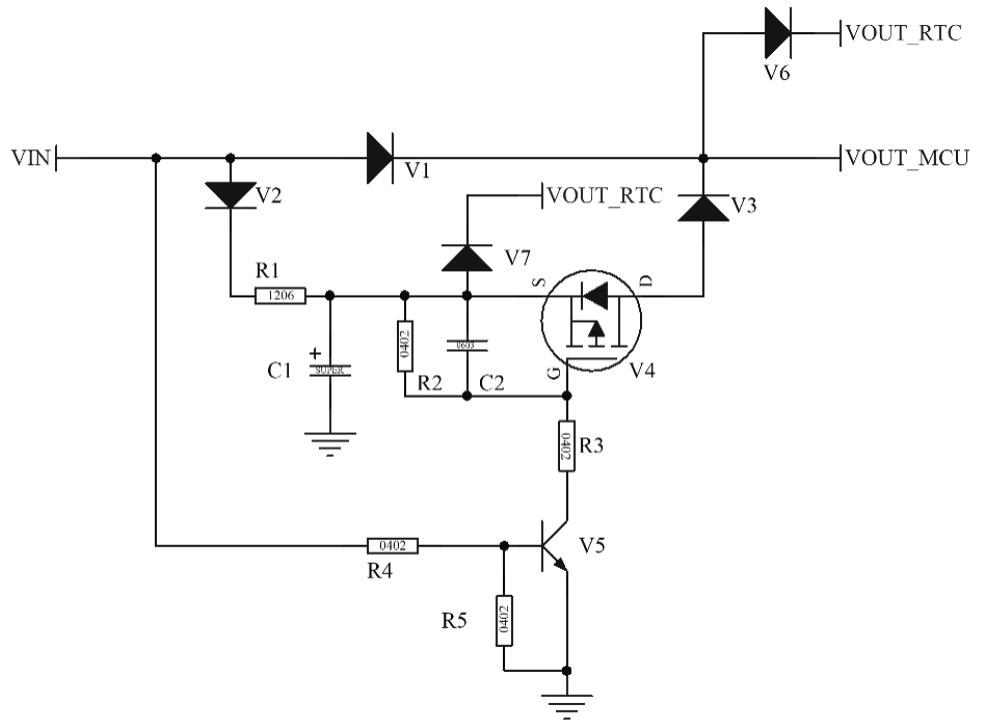

3、一种电能表掉电数据保存电路,包括法拉电容c1,所述法拉电容c1用于在掉电状态下向时钟电源端vout_rtc及数据保存电源端vout_mcu供电,还包括p沟道mos管v4、rc电路和三极管;

4、所述p沟道mos管v4用于控制法拉电容c1向时钟电源端vout_rtc及数据保存电源端vout_mcu供电的电路的通断;

5、所述rc电路包括并联在p沟道mos管v4的栅极与源极之间的电阻r2和电容c2,用于控制p沟道mos管v4延迟断开;

6、所述三极管用于根据电源输入端vin的电压状态控制rc电路的工作状态。

7、作为所述电能表掉电数据保存电路的进一步改进:所述法拉电容c1一端接地、另一端与p沟道mos管v4的源极相连接;法拉电容c1的另一端还通过电阻r1与二极管v2的负极相连接;二极管v2的正极与电源输入端vin相连接;

8、所述电源输入端vin与二极管v1的正极相连接,二极管v1的负极与数据保存电源端vout_mcu相连接、还与二极管v6的正极相连接,所述二极管v6的负极与时钟电源端vout_rtc相连接。

9、作为所述电能表掉电数据保存电路的进一步改进:p沟道mos管v4的漏极与二极管v3的正极相连接,二极管v3的负极与二极管v1的负极相连接。

10、作为所述电能表掉电数据保存电路的进一步改进:p沟道mos管v4的源极还与二极管v7的正极相连接,二极管v7的负极与时钟电源端vout_rtc相连接。

11、作为所述电能表掉电数据保存电路的进一步改进:所述三极管为npn三极管v5,所述npn三极管v5的基极通过电阻r4与电源输入端vin相连接,npn三极管v5的基极与发射极之间连接有电阻r5,npn三极管v5的集电极通过电阻r3与p沟道mos管v4的栅极相连接,npn三极管v5的发射极接地。

12、作为所述电能表掉电数据保存电路的进一步改进:所述电阻r2阻值为2mω,电容c2的容量为2.2uf。

13、作为所述电能表掉电数据保存电路的进一步改进:所述电源输入端vin的电压为6v,法拉电容c1的额定电压为5.5v、容量为1.5f。

14、相对于现有技术,本实用新型具有以下有益效果:(1)本电路在掉电时通过rc电路控制mos管维持导通一段时间后关闭,mcu只需要完成保存工作,不需要通过mcu对mos管进行控制,因此法拉电容无需为mcu长时间供电,小容量电容即可满足短时间的数据保存和后续维持时钟电路运行的需要,同时也无需增加其它芯片和复杂的电路,结构简单,成本低,有效提高能源的有效利用率;(2)通过调整电容r2和c2的参数,可以调整p沟道mos管v4的关闭时间,可以满足不同场景下的临时供电的需求。

技术特征:

1.一种电能表掉电数据保存电路,包括法拉电容c1,所述法拉电容c1用于在掉电状态下向时钟电源端vout_rtc及数据保存电源端vout_mcu供电,其特征在于:还包括p沟道mos管v4、rc电路和三极管;

2.如权利要求1所述的电能表掉电数据保存电路,其特征在于:所述法拉电容c1一端接地、另一端与p沟道mos管v4的源极相连接;法拉电容c1的另一端还通过电阻r1与二极管v2的负极相连接;二极管v2的正极与电源输入端vin相连接;

3.如权利要求2所述的电能表掉电数据保存电路,其特征在于:p沟道mos管v4的漏极与二极管v3的正极相连接,二极管v3的负极与二极管v1的负极相连接。

4.如权利要求3所述的电能表掉电数据保存电路,其特征在于:p沟道mos管v4的源极还与二极管v7的正极相连接,二极管v7的负极与时钟电源端vout_rtc相连接。

5.如权利要求4所述的电能表掉电数据保存电路,其特征在于:所述三极管为npn三极管v5,所述npn三极管v5的基极通过电阻r4与电源输入端vin相连接,npn三极管v5的基极与发射极之间连接有电阻r5,npn三极管v5的集电极通过电阻r3与p沟道mos管v4的栅极相连接,npn三极管v5的发射极接地。

6.如权利要求1至5任一所述的电能表掉电数据保存电路,其特征在于:所述电阻r2阻值为2mω,电容c2的容量为2.2uf。

7.如权利要求1至5任一所述的电能表掉电数据保存电路,其特征在于:所述电源输入端vin的电压为6v,法拉电容c1的额定电压为5.5v、容量为1.5f。

技术总结

本技术公开了一种电能表掉电数据保存电路,包括法拉电容C1,所述法拉电容C1用于在掉电状态下向时钟电源端VOUT_RTC及数据保存电源端VOUT_MCU供电;还包括P沟道MOS管V4、RC电路和三极管;所述P沟道MOS管V4用于控制法拉电容C1向时钟电源端VOUT_RTC及数据保存电源端VOUT_MCU供电的电路的通断;所述RC电路包括并联在P沟道MOS管V4的栅极与源极之间的电阻R2和电容C2,用于控制P沟道MOS管V4延迟断开;所述三极管用于根据电源输入端VIN的电压状态控制RC电路的工作状态。本技术提供了一种简单的掉电后数据保存方式,降低了掉电数据保存的成本。

技术研发人员:杨业旺,郝世凯,袁阔,陈斐,张福强,司加祯,卢志强,李静伟,胡光发,闫芦,田振,苑永正

受保护的技术使用者:烟台东方威思顿电气有限公司

技术研发日:20230406

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!