半导体封装结构的制作方法

[0001]

本发明是有关于一种半导体封装结构。

背景技术:

[0002]

当动态随机存取存储器(dynamic random access memory,dram)在运作时,因电磁效应而产生的电磁波会对周围其他的电子产品产生干扰,进而导致产品故障。这种现象称为电磁干扰(electromagnetic interference,emi)。另一方面,由周围其他的电子产品所发射出的电磁波亦会对动态随机存取存储器产生干扰。

[0003]

因此,期望开发出具有改善的抗干扰能力(亦称作电磁灵敏度(electromagnetic sensibility,ems))的动态随机存取存储器装置,以防止电磁干扰。

技术实现要素:

[0004]

本发明的一个目的在于提供一种半导体封装结构,其可以阻挡由半导体晶粒所产生的电磁波对周围其他电子装置的干扰,从而进一步改善半导体封装结构的电磁灵敏度。

[0005]

根据本发明一实施方式,半导体封装结构包含基板、半导体晶粒、虚设晶粒、导电层、至少一个第一导线以及至少一个第二导线。半导体晶粒设置在基板上。虚设晶粒设置在半导体晶粒上。导电层设置在虚设晶粒上。第一导线将半导体晶粒电性连接至信号源。第二导线将导电层电性连接至接地源。

[0006]

在本发明一实施方式中,导电层于基板的垂直投影面积覆盖半导体晶粒于基板的垂直投影面积。

[0007]

在本发明一实施方式中,半导体封装结构还包含第一模压复合材,包覆半导体晶粒及虚设晶粒。

[0008]

在本发明一实施方式中,第一模压复合材还包覆第一导线及第二导线。

[0009]

在本发明一实施方式中,半导体封装结构还包含第一粘胶层以及第二粘胶层。第一粘胶层将半导体晶粒贴附至基板。第二粘胶层将虚设晶粒贴附至半导体晶粒。

[0010]

在本发明一实施方式中,基板包含介电层以及多个导电垫。介电层具有第一表面及第二表面。多个导电垫设置在介电层的第一表面及第二表面。

[0011]

在本发明一实施方式中,基板还包含多个走线,连接介电层的第一表面的导电垫或介电层的第二表面的导电垫。

[0012]

在本发明一实施方式中,基板还包含多个导电结构,延伸穿过介电层。导电结构分别将介电层的第一表面的导电垫电性连接至介电层的第二表面的导电垫。

[0013]

在本发明一实施方式中,半导体封装结构还包含多个焊球,电性连接至介电层的第二表面的导电垫。

[0014]

在本发明一实施方式中,基板还包含两防焊遮罩,分别设置在介电层的第一表面及第二表面。

[0015]

在本发明一实施方式中,半导体封装结构还包含第二模压复合材,具有第一部分

及第二部分。第一部分穿过基板,且第二部分设置在基板的底面。

[0016]

在本发明一实施方式中,第二模压复合材的第一部分接触半导体晶粒的底面。

[0017]

在本发明一实施方式中,第二模压复合材包覆第一导线。

[0018]

在本发明一实施方式中,第二模压复合材的第一部分的宽度小于第二模压复合材的第二部分的宽度。

[0019]

在本发明一实施方式中,半导体封装结构还包含第一粘胶层以及第二粘胶层。第一粘胶层将半导体晶粒贴附至基板。第二粘胶层将虚设晶粒贴附至半导体晶粒。

[0020]

在本发明一实施方式中,第一粘胶层围绕第二模压复合材的第一部分的一部分。

[0021]

在本发明一实施方式中,第一粘胶层接触第二模压复合材的第一部分的一部分。

[0022]

在本发明一实施方式中,基板包含介电层以及多个导电垫。介电层具有第一表面及第二表面。多个导电垫设置在介电层的第一表面及第二表面。

[0023]

在本发明一实施方式中,半导体封装结构还包含多个焊球,电性连接至介电层的第二表面的导电垫。

[0024]

在本发明一实施方式中,第二模压复合材覆盖介电层的第二表面的部分的导电垫。

[0025]

根据本发明上述实施方式,由于虚设晶粒设置在半导体晶粒上,且导电层设置在虚设晶粒上并通过第二导线电性连接至接地源,因此阻挡了由半导体晶粒所产生的电磁波对周围其他电子装置的干扰,进而防止半导体封装结构与周围其他电子装置之间的电磁干扰。此外,亦进一步改善半导体封装结构的电磁灵敏度。

附图说明

[0026]

为让本发明的上述和其他目的、特征、优点与实施例能更明显易懂,结合附图详细说明如下:

[0027]

图1绘示根据本发明一实施方式的半导体封装结构的制造方法在各步骤的剖面图。

[0028]

图2绘示根据本发明一实施方式的半导体封装结构的制造方法在各步骤的俯视图。

[0029]

图3至图5绘示根据本发明一实施方式的半导体封装结构的制造方法在各步骤的剖面图。

[0030]

图6绘示图5的半导体封装结构的俯视图,其中省略第一模压复合材。

[0031]

图7绘示根据本发明另一实施方式的半导体封装结构的制造方法在各步骤的剖面图。

[0032]

图8绘示根据本发明另一实施方式的半导体封装结构的制造方法在各步骤的俯视图。

[0033]

图9至图11绘示根据本发明一实施方式的半导体封装结构的制造方法在各步骤的剖面图。

[0034]

图12绘示图11的半导体封装结构的俯视图,其中省略第一模压复合材。

[0035]

图13绘示图11的半导体封装结构的仰视图,其中省略焊球。

[0036]

主要附图标记说明:

[0037]

100、100a-半导体封装结构,109-底面,110、110a-基板,111-第一表面,112-介电层,113-第二表面,114-第一导电垫,114a-第一导电垫,114b-第一导电垫,115-走线,116-第二导电垫,116a-第二导电垫,116b-第二导电垫,117-通孔,118-导电结构,119-防焊遮罩,120-半导体晶粒,121-顶面,122-第三导电垫,123-底面,130-虚设晶粒,140-导电层,150-第一导线,160-第二导线,170-第一粘胶层,180-第二粘胶层,190-焊球,200-第一模压复合材,210-第二模压复合材,212-第一部分,214-第二部分,w1、w2-宽度,s10、s12、s14、s16、s20、s22、s24、s26-步骤,a-a、b-b-线段。

具体实施方式

[0038]

以下将以附图公开本发明的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,在本发明部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些公知惯用的结构与元件在附图中将以简单示意的方式绘示的。

[0039]

应当理解,诸如“下”或“底部”和“上”或“顶部”的相对术语可在本文中用于描述一个元件与另一元件的关系,如图所示。应当理解,相对术语旨在包括除了图中所示的方位之外的装置的不同方位。例如,如果一个附图中的装置翻转,则被描述为在其他元件的“下”侧的元件将被定向在其他元件的“上”侧。因此,示例性术语“下”可以包括“下”和“上”的取向,取决于附图的特定取向。类似地,如果一个附图中的装置翻转,则被描述为在其它元件“下方”或“下方”的元件将被定向为在其它元件“上方”。因此,示例性术语“下面”或“下面”可以包括上方和下方的取向。

[0040]

应当理解,当诸如层、膜、区域或基板的元件被称为在另一元件“上”或“连接到”另一元件时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反,当元件被称为“直接在另一元件上”或“直接连接到”另一元件时,不存在中间元件。如本文所使用的,“连接”可以指物理及/或电性连接。再者,“电性连接”或“耦合”是可为二元件间存在其它元件。

[0041]

在本发明一实施方式中,提供了一种半导体封装结构及其制造方法。为了方便说明及清楚起见,将首先在本文中讨论半导体封装结构的制造方法。此外,在依附以下实施方式的附图中,一些次要元件可被省略。

[0042]

图1及图2分别绘示根据本发明一实施方式的图5的半导体封装结构100的制造方法在步骤s10的剖面图及俯视图。在步骤s10中,提供具有第一表面111及第二表面113的介电层112。设置多个第一导电垫114、多个走线115以及多个第二导电垫116于介电层112上。形成多个导电结构118穿过介电层112。通过走线115及导电结构118在第一导电垫114之间以及第二导电垫116之间形成电性连接。分别设置两防焊遮罩119于介电层112的第一表面111及第二表面113。随后,便可形成具有介电层112、第一导电垫114、走线115、第二导电垫116、导电结构118以及防焊遮罩119的基板110。

[0043]

在一些实施方式中,第一导电垫114电性连接至接地源,而第二导电垫116电性连接至信号源或电源。详细来说,一些第二导电垫116电性连接至信号源,而另一些第二导电垫116电性连接至电源。为了清楚起见及方便说明,在以下叙述中,位于介电层112的第一表面111及第二表面113的第一导电垫114分别称作第一导电垫114a及第一导电垫114b,而位

于介电层112的第一表面111及第二表面113的第二导电垫116分别称作第二导电垫116a及第二导电垫116b。

[0044]

图3绘示根据本发明一实施方式的图5的半导体封装结构100的制造方法在步骤s12的剖面图。在步骤s12中,形成第一粘胶层170于设置在介电层112的第一表面111的防焊遮罩119上。接着,通过第一粘胶层170将设置有多个第三导电垫122的半导体晶粒120贴附至基板110,其中,第三导电垫122位于半导体晶粒120的顶面121。随后,将多个第一导线150分别由第三导电垫122连接至位于介电层112的第一表面111的导电垫。详细来说,一些第一导线150由第三导电垫122连接至第一导电垫114a,而另一些第一导线150由第三导电垫122连接至第二导电垫116a。如此一来,半导体晶粒120电性连接至信号源、电源以及接地源。

[0045]

图4绘示根据本发明一实施方式的图5的半导体封装结构100的制造方法在步骤s14的剖面图。在步骤s14中,形成第二粘胶层180于半导体晶粒120上,并通过第二粘胶层180将设置有导电层140的虚设晶粒130贴附至半导体晶粒120。随后,将至少一个第二导线160的两端分别接合至导电层140及第一导电垫114a的其中一个。虽然图4所绘示的第二导线160的其中一端接合至靠近导电层140边缘的位置,但第二导线160的其中一端可接合至导电层140的任意位置,依设计者的需求而定。

[0046]

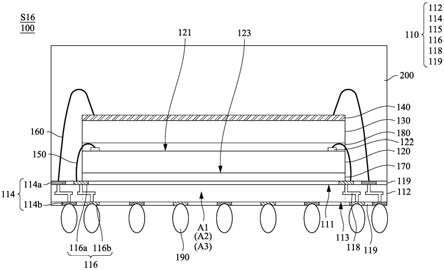

图5绘示根据本发明一实施方式的半导体封装结构100的制造方法在步骤s16的剖面图。在步骤s16中,形成第一模压复合材200包覆半导体晶粒120、虚设晶粒130、第一导线150以及第二导线160。安装多个焊球190至第一导电垫114b及第二导电垫116b以将半导体封装结构100电性连接至外部电子装置。在步骤s16之后,便形成半导体封装结构100。上述方法是细间距球栅阵列(fine-pitch ball grid array,fbga)方法与双晶片封装(dual die package,dpp)方法的组合。

[0047]

图6绘示图5的半导体封装结构100的俯视图。应了解到,图1及图3至图5的剖面位置为图6的线段a-a。此外,图6省略第一模压复合材200。同时参阅图5及图6,半导体封装结构100包含基板110、半导体晶粒120、虚设晶粒130、导电层140、第一导线150以及第二导线160。半导体晶粒120设置在基板110上。设置有导电层140的虚设晶粒130设置在半导体晶粒120上。第一导线150将半导体晶粒120电性连接至信号源、电源以及接地源。第二导线160将导电层140电性连接至接地源。

[0048]

由于虚设晶粒130设置在半导体晶粒120上,且导电层140设置在虚设晶粒130上并通过第二导线160电性连接至接地源,因此阻挡了由半导体晶粒120所产生的电磁波对周围其他电子装置的干扰,进而防止半导体封装结构100与周围其他电子装置之间的电磁干扰。此外,亦进一步改善半导体封装结构100的电磁灵敏度。

[0049]

在一些实施方式中,半导体晶粒120可为存储集成电路(memory integrated circuit),且虚设晶粒130可为不具有任何功能的硅晶粒。半导体晶粒120通过第一粘胶层170贴附至基板110,且虚设晶粒130通过第二粘胶层180贴附至半导体晶粒120。第一粘胶层170可包含与第二粘胶层180相同的材料。此外,导电层140可由包含铝的材料所制成,但并不用以限制本发明。在其他实施方式中,导电层140可由包含其他合适的金属材料所制成。

[0050]

由于虚设晶粒130配置以支撑导电层140,因此虚设晶粒130于基板110的垂直投影面积a1应完全覆盖导电层140于基板110的垂直投影面积a2。此外,导电层140于基板110的垂直投影面积a2应完全覆盖半导体晶粒120于基板110的垂直投影面积a3,以确保由半导体

晶粒120所产生的电磁波完全被阻挡。

[0051]

在一些实施方式中,第一导电垫114设置于介电层112的第一表面111及第二表面113,且第二导线160将导电层140电性连接至第一导电垫114a的其中一个。第一导电垫114a可由包含铜的材料所制成,但并不用以限制本发明。此外,第二导线160的数量可为多个,且每一个第二导线160将导电层140电性连接至对应的第一导电垫114a。第二导线160可由包含金的材料所制成,但并不用以限制本发明。

[0052]

在一些实施方式中,走线115设置在介电层112的第一表面111及第二表面113。走线115连接第一导电垫114a并连接第一导电垫114b。此外,导电结构118穿过介电层112并分别将第一导电垫114a电性连接至对应的第一导电垫114b。此外,焊球190将第一导电垫114b电性连接至印刷电路板(printed circuit board,pcb)以进一步连接至接地源。根据上述,导电层140通过第一导电垫114、走线115、导电结构118以及焊球190之间的各种连接以电性连接至接地源。

[0053]

在一些实施方式中,第二导电垫116设置于介电层112的第一表面111及第二表面113,且第一导线150将半导体晶粒120电性连接至第一导电垫114a及第二导电垫116a。第二导电垫116可由包含铜的材料所制成,但并不用以限制本发明。第一导线150可由包含金的材料所制成,但并不用以限制本发明。

[0054]

在一些实施方式中,走线115连接第二导电垫116a并连接第二导电垫116b。详细来说,一些走线115将连接至信号源的第二导电垫116连接起来,而另一些走线115将连接至电源的第二导电垫116连接起来。此外,第二导电垫116a通过导电结构118分别电性连接至对应的第二导电垫116b。焊球190将第二导电垫116b电性连接至印刷电路板、控制器、监视器或任何电子装置。根据上述,半导体晶粒120通过第二导电垫116、走线115、导电结构118以及焊球190之间的各种连接以电性连接至信号源及电源。此外,半导体晶粒120通过第一导电垫114、走线115、导电结构118以及焊球190之间的各种连接以电性连接至接地源。

[0055]

防焊遮罩119保护位于介电层112的第一表面111及第二表面113的走线115,并进一步防止走线115短路。防焊遮罩119可由包含介电质(例如树脂)的材料所制成,但并不用以限制本发明。

[0056]

第一模压复合材200包覆半导体晶粒120以及虚设晶粒130。在一些实施方式中,第一模压复合材200进一步包覆第一导线150及第二导线160。第一模压复合材200可由包含树脂的材料所制成,但并不用以限制本发明。

[0057]

在以下叙述中,将说明半导体封装结构100a的制造方法。由于图7至图11中的一些步骤类似于图1至图5中的对应步骤,因此类似的步骤将不再赘述,合先叙明。

[0058]

图7及图8分别绘示根据本发明一实施方式的图11的半导体封装结构100的制造方法在步骤s20的剖面图及俯视图。在步骤s20中,提供具有第一表面111及第二表面113的介电层112。形成通孔117穿过介电层112。形成多个第一导电垫114、多个走线115、多个第二导电垫116、多个导电结构118以及两防焊遮罩119以形成基板110a。

[0059]

图9绘示根据本发明一实施方式的图11的半导体封装结构100a的制造方法在步骤s22的剖面图。在步骤s22中,形成第一粘胶层170于设置在介电层112的第一表面111的防焊遮罩119上。接着,通过第一粘胶层170将设置有多个第三导电垫122的半导体晶粒120贴附至基板110a,且半导体晶粒120的底面123的第三导电垫122由通孔117裸露。随后,将多个第

一导线150分别由第三导电垫122连接至位于介电层112的第二表面113的导电垫。详细来说,一些第一导线150由第三导电垫122连接至第一导电垫114b,而另一些第一导线150由第三导电垫122连接至第二导电垫116b。如此一来,半导体晶粒120电性连接至信号源、电源以及接地源。

[0060]

图10绘示根据本发明一实施方式的半导体封装结构100a的制造方法在步骤s24的剖面图。在步骤s24中,形成第二粘胶层180于半导体晶粒120上,并通过第二粘胶层180将虚设晶粒130贴附至半导体晶粒120。接着,设置导电层140于虚设晶粒130上。随后,将至少一个第二导线160的两端分别接合至导电层140及第一导电垫114a的其中一个。虽然图10所绘示的第二导线160的其中一端接合至靠近导电层140边缘的位置,但第二导线160的其中一端可接合至导电层140的任意位置,依设计者的需求而定。

[0061]

图11绘示根据本发明一实施方式的半导体封装结构100a的制造方法在步骤s26的剖面图。在步骤s26中,形成第一模压复合材200包覆半导体晶粒120、虚设晶粒130以及第二导线160。形成第二模压复合材210以填充通孔117并覆盖基板110a的部分的底面109,以包覆第一导线150。第二模压复合材210进一步覆盖部分的接合至第一导线150的第二导电垫116b。安装多个焊球190至未与第一导线150接合的第一导电垫114b及第二导电垫116b,使得半导体封装结构100电性连接至外部电子装置。在步骤s26之后,便形成半导体封装结构100a。上述方法是窗型球栅阵列(window ball grid array,fbga)方法与双晶片封装(dual die package,dpp)方法的组合。

[0062]

图12绘示图11的半导体封装结构100a的俯视图。图13绘示图11的半导体封装结构100a的仰视图。应了解到,图7及图9至图11的剖面位置为图12的线段b-b。此外,图12省略第一模压复合材200,且图13省略焊球190。同时参阅图11至图13,半导体封装结构100a与半导体封装结构100的差异在于:半导体晶粒120通过位于半导体晶粒120的底面123的第三导电垫122电性连接至信号源、电源以及接地源。此外,半导体封装结构100a还包含包覆第一导线150的第二模压复合材210。

[0063]

在一些实施方式中,半导体封装结构100a中的第二导电垫116可仅设置在介电层112的第二表面113。换句话说,半导体封装结构100a可仅包含第二导电垫116b,但并不用以限制本发明。在其他实施方式中,半导体封装结构100a可包含第二导电垫116a选择性地设置在介电层112的第一表面111,依设计者的需求而定。

[0064]

在一些实施方式中,半导体封装结构100a中的第一模压复合材200包覆半导体晶粒120、虚设晶粒130以及第二导线160,而第二模压复合材210包覆第一导线150。第二模压复合材210具有第一部分212及第二部分214。第一部分212穿过基板110a(包含介电层112及防焊遮罩119),并接触半导体晶粒120的底面123,而第二部分214设置于基板110a的部分的底面109。

[0065]

在一些实施方式中,半导体封装结构100a中的第一粘胶层170围绕第二模压复合材210的第一部分212。此外,第一粘胶层170接触第二模压复合材210的第一部分212。

[0066]

在一些实施方式中,第二模压复合材210的第一部分212的宽度w1小于第二模压复合材210的第二部分214的宽度w2。第二模压复合材210的第二部分214的剖面形状可为三角形、矩形、梯形或其他合适的几何形状,但并不用以限制本发明。此外,第二模压复合材210的第二部分214覆盖部分的与第一导线150接合的第二导电垫116b。此外,半导体封装结构

100a中的焊球190可仅连接至未与第一导线150接合的第二导电垫116b。

[0067]

虽然本发明已以实施方式公开如上,然其并非用以限定本发明,任何所属领域的技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1