半导体结构及其制造方法与流程

1.本发明属于半导体技术领域,涉及一种半导体结构及其制造方法。

背景技术:

2.近年来,半导体装置的尺寸已逐渐缩小。在半导体技术中,特征尺寸的缩小、速度、效能、密度与每单位集成电路的成本的改良皆为相当重要的目标。在实际应用上,装置尺寸缩小的同时,仍须保持装置的电性以符合商业需求。

技术实现要素:

3.本发明有关于一种半导体结构及其制造方法。

4.根据本发明的一方面,提出一种半导体结构,其包括一第一阶梯状结构、一第二阶梯状结构、一导电柱与一接触柱。第一阶梯状结构包括多个导电阶梯层。导电柱穿过第二阶梯状结构。导电柱具有相对的一上导电柱端部与一下导电柱端部。接触柱电性连接在导电阶梯层的一导电阶梯层上。接触柱具有相对的一上接触端部与一下接触端部。上接触端部与下接触端部分别电性连接至导电柱的上导电柱端部与该一导电阶梯层。

5.根据本发明的另一方面,提出一种半导体结构,其包括一第一阶梯状结构、一接触柱、一半导体装置、一导电柱与一导电元件。第一阶梯状结构包括多个阶梯层。阶梯层各包括一导电阶梯层。接触柱电性连接在导电阶梯层的一导电阶梯层上。半导体装置包括一有源装置和/或一无源装置,并在第一阶梯状结构下方。导电元件在第一阶梯状结构上方沿一横方向延伸跨过阶梯层的共平面的一第一侧壁表面,并电性连接在导电柱与接触柱之间。导电柱电性连接在半导体装置与导电元件之间。

6.根据本发明的再一方面,提出一种半导体结构的制造方法,包括以下步骤。形成一绝缘叠层结构。绝缘叠层结构包括交错堆迭的多个第一绝缘层与多个第二绝缘层。第一绝缘层的材质不同于第二绝缘层的材质。绝缘叠层结构包括相邻的一阶梯状区与一块体状区。移除阶梯状区的一部分与块体状区的第二绝缘层,从而形成多个狭缝在第一绝缘层之间,而保留阶梯状区的另一部分的第二绝缘层。以一导电材料填充狭缝。

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

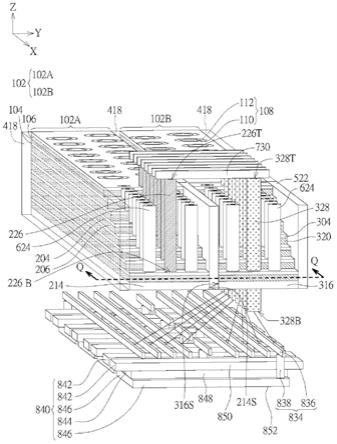

8.图1a绘示根据一实施例的半导体结构的立体示意图。

9.图1b绘示半导体结构的横向剖面图。

10.图1c绘示半导体装置与导电组件的俯视图。

11.图2绘示根据另一实施例的存储材料层、导电层与柱元件的横向剖面图。

12.图3绘示根据另一实施例的叠层结构的存储材料层、导电层与柱元件的立体示意图。

13.图4至图11绘示根据一实施例的半导体结构的制造方法。

14.【符号说明】

15.102,102

′

:叠层结构

16.102a:叠层结构

17.102b:叠层结构

18.104:绝缘层

19.106:导电层

20.108,108a,108b:柱元件

21.110,110a,110b:通道元件

22.112:存储材料层

23.113:源/漏极柱

24.115:源/漏极柱

25.117:绝缘柱

26.119:介电材料层

27.204:第一绝缘阶梯层

28.206:导电阶梯层

29.214:第一阶梯状结构

30.214s:第一侧壁表面

31.226:接触柱

32.226b:下接触端部

33.226t:上接触端部

34.316:第二阶梯状结构

35.316s:第二侧壁表面

36.316k:侧壁表面

37.320:第二绝缘阶梯层

38.328:导电柱

39.328b:下导电柱端部

40.328t:上导电柱端部

41.418:绝缘条

42.522:绝缘墙元件

43.624:柱元件

44.730:导电元件

45.832:半导体装置

46.834:导电组件

47.836:第一金属层

48.838:导电通孔

49.840:晶体管

50.842:栅结构

51.844:源/漏极

52.846:源/漏极

53.848:栅介电层

54.850:栅电极

55.852:基底

56.854:控制电路

57.856:电平移位器

58.902:块体状区

59.902a:部分

60.902b:部分

61.904:第一绝缘层

62.914:部分

63.915:阶梯状区

64.916:部分

65.920:第二绝缘层

66.958:绝缘叠层结构

67.960:凹槽

68.962:沟道

69.964:狭缝

具体实施方式

70.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

71.以下以一些实施例进行说明。须注意的是,本公开并非显示出所有可能的实施例,未于本公开提出的其他实施方式也可能可以应用。再者,附图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和附图内容仅作叙述实施例之用,而非作为限缩本公开保护范围之用。另外,实施例中的叙述,例如细节结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本公开欲保护的范围进行限缩。实施例的步骤和结构各自细节可在不脱离本公开的精神和范围内根据实际应用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件进行说明。

72.请参照图1a,其绘示根据一实施例的半导体结构的立体示意图。叠层结构102可包括交错堆叠的绝缘层104与导电层106。导电层106通过绝缘层104互相分开。存储装置可为3d存储阵列,其存储单元在叠层结构102中。柱元件108穿过叠层结构102。一实施例中,柱元件108包括通道元件110,亦可称为有源(active)柱元件。通道元件110穿过叠层结构102。存储单元定义在通道元件110与导电层106之间的存储材料层112中。叠层结构102的导电层106可用作字线(wl)。一实施例中,柱元件108可包括存储材料层112围绕在通道元件110的侧壁表面上。存储装置可包括例如异或栅闪存存储(nor flash memory)、与非栅闪存存储(nand flash memory)等闪存存储,或其它种类存储。

73.第一阶梯状结构214、第二阶梯状结构316与叠层结构102在纵方向(例如垂直方向或z方向)上可互不重叠。第一阶梯状结构214与第二阶梯状结构316可在叠层结构102的相

同侧,并在y方向上排列。例如,第一阶梯状结构214与第二阶梯状结构316分别在叠层结构102a与叠层结构102b的相同侧。绝缘条418可在例如x方向上延伸在叠层结构102a与叠层结构102b的侧壁表面之间。绝缘条418将叠层结构102a的导电层106隔离于叠层结构102b的导电层106。在图1a中,绝缘条418是以透视方法呈现。第一阶梯状结构214与第二阶梯状结构316各包括多个阶梯层。阶梯层的一下阶梯层的面积是大于一上阶梯层的面积。

74.第一阶梯状结构214的阶梯层各包括导电阶梯层206与第一绝缘阶梯层204。导电阶梯层206与第一绝缘阶梯层204交错堆叠。一实施例中,一阶梯层的导电阶梯层206在第一绝缘阶梯层204的下方。另一实施例中,导电阶梯层206可在第一绝缘阶梯层204的上方。第一阶梯状结构214的导电阶梯层206可连续连接叠层结构102的导电层106。第一阶梯状结构214的第一绝缘阶梯层204可连续连接叠层结构102的绝缘层104。

75.第二阶梯状结构316可为绝缘体。第二阶梯状结构316的阶梯层可包括绝缘层,亦可称为绝缘阶梯层。一实施例中,第二阶梯状结构316的阶梯层各可包括第一绝缘阶梯层304与第二绝缘阶梯层320。第一绝缘阶梯层304与第二绝缘阶梯层320可交错堆叠。一实施例中,阶梯层的第二绝缘阶梯层320是在第一绝缘阶梯层304下方。另一实施例中,第二绝缘阶梯层320可在第一绝缘阶梯层304上。第一绝缘阶梯层304的材质不同于第二绝缘阶梯层320的材质。实施例中,第二绝缘阶梯层320、第一阶梯状结构214的导电阶梯层206与叠层结构102的导电层106在相同的阶层中。第一阶梯状结构214的导电阶梯层206电性绝缘第二阶梯状结构316。绝缘墙元件522环绕第二阶梯状结构316的侧壁表面。

76.柱元件624可在第一阶梯状结构214及第二阶梯状结构316上。柱元件624亦可在纵方向上穿过第一阶梯状结构214或第二阶梯状结构316至最底阶梯层。柱元件624的材料组合可相同于柱元件108的材料组合。一实施例中,柱元件624可包括通道元件与存储材料层围绕在通道元件的侧壁表面上。实施例中,柱元件624可为虚置柱元件。柱元件624可为电性浮接。但本公开不限于此,柱元件624的材料组合亦可不同于柱元件108的材料组合。柱元件624可使用任意的绝缘材料。

77.可同时参照图1a与图1b。其中图1b绘示图1a的qq剖面线延伸画出的半导体结构的横向剖面图。图1a所示的结构可对应图1b的虚线方框垂直方向延伸区域中的结构。接触柱226垂直延伸在第一阶梯状结构214的导电阶梯层206上。接触柱226电性连接导电阶梯层206。接触柱226具有相对的上接触端部226t与下接触端部226b。接触柱226的下接触端部226b是电性且物性接触在导电阶梯层206上。电性连接较上方导电阶梯层206的接触柱226其纵向尺寸是小于电性连接较下方导电阶梯层206的接触柱226的纵向尺寸。第一阶梯状结构214的导电阶梯层206电性连接在叠层结构102中的存储单元与接触柱226之间。导电柱328穿过第二阶梯状结构316。导电柱328分别穿过第二阶梯状结构316的不同阶梯层数目。较靠近叠层结构102的导电柱328穿过的阶梯层数目大于较远离叠层结构102的导电柱328穿过的阶梯层数目。导电柱328具有相对的上导电柱端部328t与下导电柱端部328b。下导电柱端部328b的位置可位在第二阶梯状结构316的底表面下方。穿过第二阶梯状结构316的导电柱328可具有相同的纵向尺寸(例如上导电柱端部328t与下导电柱端部328b之间的垂直方向距离)。

78.第一阶梯状结构214的阶梯层具有共平面的第一侧壁表面214s。第二阶梯状结构316的阶梯层具有共平面的第二侧壁表面316s。第二阶梯状结构316的第二侧壁表面316s面

朝向第一阶梯状结构214的第一侧壁表面214s。实施例中,导电元件730在第一阶梯状结构214与第二阶梯状结构316上方沿一横方向(其垂直于垂直方向)延伸跨过第一侧壁表面214s与第二侧壁表面316s。导电元件730电性连接在导电柱328的上导电柱端部328t与接触柱226的上接触端部226t之间。

79.可同时参照图1a与图1c。其中图1c绘示位在叠层结构102、第一阶梯状结构214与第二阶梯状结构316下方的半导体装置832与导电组件834的俯视图。导电柱328可从其下导电柱端部328b可经由配置在下方的导电组件834(例如第一金属层(m1)836或导电通孔(via)838等)电性连接至半导体装置832。半导体装置832可在垂直方向上重叠第一阶梯状结构214、第二阶梯状结构316和/或叠层结构102。半导体装置832包括有源装置和/或无源装置。有源装置可例如包括晶体管840、二极管(diode)等。晶体管840包括栅结构842、源/漏极844与源/漏极846。源/漏极844与源/漏极846其中之一为源极,源/漏极844与源/漏极846其中另一为漏极。栅结构842包括栅介电层848与栅电极850。栅介电层848在基底852上。栅电极850在栅介电层848上。源/漏极844与源/漏极846在栅结构842的相对侧的基底852中。基底852可包括半导体基底,例如硅基底或绝缘体上硅(soi)等。晶体管840可包括诸如nmos、pmos、cmos、双极性晶体管(bjt)等。无源装置可包括电阻、电容和/或电感。例如导电柱328的下导电柱端部328b可电性连接至晶体管840的源/漏极846(例如漏极)。半导体装置832可包括cmos反相器。图1a所示的半导体装置832与导电组件834可对应图1c的虚线方框中的部位。

80.一实施例中,半导体装置832的控制电路854处理行地址信号以选择或非选择方框或字线。控制电路854的信号可提供至电平移位器(level shifter)856加宽电压范围,例如从适用于地址信号的窄输入电压范围,至适用于通道(pass)字线电压的宽输出电压范围,字线电压可以是高电平的正电压或高电平的负电压。电平移位器856的信号可施加至区域驱动器(local driver)(例如(通道)晶体管840),以选择或非选择方框或字线,(通道)晶体管840用来通过字线电压、或阻挡字线电压到达存储阵列的字线。存储阵列储存数据,且可以是易失性或非易失性存储。

81.实施例中,电路线路包括延伸跨过第一阶梯状结构214的第一侧壁表面214s与第二阶梯状结构316的第二侧壁表面316s的导电元件730与穿过第二阶梯状结构316的导电柱328。此电路线路其并未占据到第一阶梯状结构214与第二阶梯状结构316的外侧区域(亦即第一阶梯状结构214与第二阶梯状结构316相对于叠层结构102侧的区域)的面积,因此能缩减单元装置的占据面积,进而能够提升芯片上能配置的装置密度。此外,此电路线路亦提供短的信号路径(如电流路径)。穿过第二阶梯状结构316的导电柱328距离第一阶梯状结构214、第二阶梯状结构316与叠层结构102下方的半导体装置832与导电组件834更近,此亦能造成更短的信号路径。因此能提升装置的操作效率。

82.图2绘示根据另一实施例的存储材料层112、导电层106与柱元件108a的横向剖面图。柱元件108a与图1a及图1b所示的柱元件108的差异说明如下。柱元件108a包括通道元件110a、源/漏极柱113、源/漏极柱115、绝缘柱117与介电材料层119。绝缘柱117在源/漏极柱113与源/漏极柱115之间。源/漏极柱113与源/漏极柱115通过绝缘柱117互相分开。源/漏极柱113与源/漏极柱115其中之一为源极,且源/漏极柱113与源/漏极柱115其中另一为漏极。介电材料层119在通道元件110a与源/漏极柱113、源/漏极柱115及绝缘柱117之间。图2的通

道元件110a与图1a及图1b所示的通道元件110之间的差异在于,通道元件110a呈封闭环形状。通道元件110a环绕在源/漏极柱113、源/漏极柱115、绝缘柱117与介电材料层119的外侧。

83.图3绘示根据另一实施例的叠层结构102

′

的存储材料层112

′

、导电层106与柱元件108b的立体示意图。柱元件108b与图2所示的柱元件108a的差异说明如下。柱元件108b包括通道元件110b、源/漏极柱113、源/漏极柱115与介电材料层119。源/漏极柱113与源/漏极柱115通过介电材料层119互相分开。图3的通道元件110b与图2所示的通道元件110a之间的差异在于,通道元件110b呈开环形状,且其相对两末端分别电性连接源/漏极柱113与源/漏极柱115。存储材料层112

′

与图1a及图1b所述的存储材料层112的差异在于,存储材料层112

′

在导电层106的上表面及下表面上,并可延伸在柱元件108b的外侧表面与导电层106之间。

84.一实施例中,在叠层结构的立体示意图中,参照图2所述的存储材料层112可类似图3所述的存储材料层112

′

的配置,位在导电层106的上表面及下表面上,并可延伸在柱元件108a的外侧表面与导电层106之间。

85.图4至图11绘示根据一实施例的半导体结构的制造方法。

86.请参照图4。提供基底852。基底852可包括半导体基底。在基底852上形成半导体装置。一实施例中,半导体装置可包括晶体管840。晶体管840的栅结构842形成在基底852上。栅结构842包括栅介电层848与栅电极850。栅介电层848形成在基底852上。栅电极850形成在栅介电层848上。栅电极850可包括例如多晶硅等合适的导电材料,诸如单晶硅、金属(例如用作金属栅)、金属硅化物等。晶体管840的源/漏极844与源/漏极846形成在栅结构842相反侧的基底852中。源/漏极844与源/漏极846可利用掺杂工艺形成。

87.可在半导体装置上方形成导电组件834。例如,导电组件834可包括导电通孔(via)838电性连接并形成在晶体管840的栅电极850、源/漏极844与源/漏极846上。导电组件834可包括导电层例如第一金属层(m1)836电性连接并形成在导电通孔838上。导电通孔838及导电层可形成在层间介电层(未显示)中或层间介电层上。但本公开不限于此,导电组件834可包括其它可能的导电电路形成在层间介电层中或层间介电层上。

88.绝缘叠层结构958形成在半导体装置(包括晶体管840)、导电组件834及层间介电层(未显示)上。绝缘叠层结构958可例如包括交错堆叠的第一绝缘层904与第二绝缘层920。实施例中,第一绝缘层904的材质不同于第二绝缘层920的材质。举例来说,第一绝缘层904可包括氧化物例如氧化硅。第二绝缘层920可包括氮化物例如氮化硅。但本公开不限于此,第一绝缘层904与第二绝缘层920亦可使用其它绝缘材质。可利用黄光光刻和刻蚀方式从绝缘叠层结构958的上表面削减邻近块体状区902的阶梯状区915的厚度。一实施例中,可形成绝缘膜(例如氧化物如氧化硅等,未显示)在绝缘叠层结构958的块体状区902与阶梯状区915上。可进行例如化学机械研磨步骤将绝缘叠层结构958上的绝缘膜(未显示)平坦化。

89.请参照图5。形成柱元件108与柱元件624分别穿过绝缘叠层结构958的块体状区902与阶梯状区915。柱元件108与柱元件624亦可穿过绝缘叠层结构958上的绝缘膜(未显示)。一实施例中,柱元件108与柱元件624的形成方法可包括利用黄光光刻和刻蚀步骤形成开孔于绝缘叠层结构958与绝缘膜(未显示)中,然而以合适的柱材料填充开孔。一实施例中,柱元件108与柱元件624可同时形成,并可包括通道元件110与存储材料层112。存储材料层112形成在开孔的侧壁表面上。存储材料层112可包括任意的电荷俘获结构,例如一氧化

物-氮化物-氧化物(ono)结构、onono结构、ononono结构、或一氧化物-氮化物-氧化物-氮化物-氧化物(be-sonos)结构等。举例来说,电荷俘获层可使用氮化物例如氮化硅,或是其他类似的高介电常数物质包括金属氧化物,例如三氧化二铝(al2o3)、氧化锆(hfo2)等。通道元件110形成在开孔中。另一实施例中,柱元件108与柱元件624可使用不同的工艺步骤分开形成。柱元件108与柱元件624可使用不同的材料组合。

90.请参照图6。可利用黄光光刻和刻蚀步骤形成凹槽960在绝缘叠层结构958的阶梯状区915与其上的绝缘膜(未显示)中。凹槽960将绝缘叠层结构958的阶梯状区915分割为部分914与部分916。阶梯状区915的部分916通过凹槽960隔开阶梯状区915的部分914与块体状区902。凹槽960可具有矩形封闭环形状。绝缘叠层结构958的阶梯状区915的部分916可即为如图1a所述的第二阶梯状结构316。

91.请参照图7。可利用绝缘材料填充凹槽960以形成绝缘墙元件522。绝缘墙元件522可环绕第二阶梯状结构316的侧壁表面,包括如图7所指示的侧壁表面316k。一实施例中,绝缘墙元件522可包括氧化物例如氧化硅。

92.请参照图8。可利用黄光光刻刻蚀步骤形成沟道962在绝缘叠层结构958中。沟道962可将绝缘叠层结构958的块体状区902分割为部分902a与部分902b。

93.请参照图9。可进行选择性刻蚀步骤移除沟道962露出的绝缘叠层结构958的阶梯状区的部分914与块体状区902的第二绝缘层920(包括氮化物例如氮化硅),从而形成狭缝964在第一绝缘层904(包括氧化物例如氧化硅)之间。此刻蚀步骤实质上不会刻蚀掉绝缘墙元件522(包括氧化物例如氧化硅)与第二阶梯状结构316上方的绝缘膜(包括氧化物例如氧化硅,未显示)。绝缘墙元件522能用作保护元件避免第二阶梯状结构316的第二绝缘层920被刻蚀掉,而可保留第二阶梯状结构316的第二绝缘层920。第二阶梯状结构316上方的绝缘膜(未显示)亦可提供避免刻蚀的保护作用。一实施例中,刻蚀步骤可包含湿法刻蚀方式,例如使用热磷酸腐蚀等合适的方法。实施例中,第一绝缘层904、第二绝缘层920、绝缘墙元件522与第二阶梯状结构316上方的绝缘膜可基于选择性刻蚀的目的任意变化并采用其它适当的材质。狭缝964露出柱元件108与柱元件624的侧壁表面与绝缘墙元件522的侧壁表面。露出狭缝964的柱元件108与柱元件624可支撑稳固露出的第一绝缘层904。

94.请参照图10。以导电材料填充狭缝964。形成在块体状区902中的导电材料是形成导电层106。形成在阶梯状区915的部分914中的导电材料是形成导电阶梯层206。如此,形成了叠层结构102与第一阶梯状结构214。

95.请参照图11。使用绝缘材料填充沟道962以形成绝缘条418。

96.请参照图1a。形成接触柱226着陆在导电阶梯层206上。接触柱226可穿过第一阶梯状结构214上方的绝缘膜(未显示)与所着陆的导电阶梯层206上方的第一绝缘阶梯层204。形成导电柱328穿过第二阶梯状结构316。导电柱328亦穿过第二阶梯状结构316上方的绝缘膜(未显示)。接触柱226与导电柱328可利用包含以黄光光刻和刻蚀工艺形成孔洞,然后以导电材料填充孔洞的方法形成。然后,可形成导电元件730在接触柱226与导电柱328上。

97.一实施例中,在参照图5所述的工艺中,柱元件108可以如图2所述的柱元件108a取代,由此可形成如图2所示的半导体结构。

98.一实施例中,在参照图5所述的工艺中,可省略形成存储材料层112的步骤,而在参照图9所述的步骤之后,形成存储材料层112在狭缝964中,然后进行图10至图1a的相关工艺

步骤,由此亦可形成参照图2所述的半导体结构。

99.另一实施例中,在参照图5所述的工艺中,柱元件108可以如图3所述的柱元件108b取代。并且,在参照图5所述的工艺中,可省略形成存储材料层112的步骤,而在参照图9所述的步骤之后,形成存储材料层112

′

在狭缝964中,然后进行图10至图1a的相关工艺步骤。如此,可形成如图3所示的半导体结构。

100.综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中具有公知常识的技术人员,在不脱离本发明的精神和范围内,当可作各种的改动与润饰。因此,本发明的保护范围当以权利要求所界定的范围为准。

101.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1