半导体封装件的制作方法

半导体封装件

[0001]

本申请要求于2019年8月16日在韩国知识产权局提交的第10-2019-0100400号韩国专利申请的优先权,该韩国专利申请的公开内容通过引用全部包含于此。

技术领域

[0002]

本发明构思涉及半导体封装件,更具体地,涉及堆叠的半导体封装件。

背景技术:

[0003]

半导体封装件实现了适用于电子产品中的集成电路芯片。通常,在半导体封装件中,半导体芯片安装在印刷电路板(pcb)上,并且键合引线或凸块被用于将半导体芯片电连接到印刷电路板。随着电子工业的发展,对电子产品的紧凑性、轻量性和多功能性的需求引起了对堆叠的半导体封装件的许多研究,在堆叠的半导体封装件中,多个半导体芯片堆叠在单个半导体封装件上。

技术实现要素:

[0004]

本发明构思的一些示例实施例提供了能够容易地堆叠多个半导体芯片并且具有优异的可靠性的半导体封装件。

[0005]

根据本发明构思的一些示例实施例,一种半导体封装件可以包括:第一半导体芯片;第二半导体芯片,位于第一半导体芯片的第一表面上;以及多个导电柱,位于第一半导体芯片的第一表面上,并且与第二半导体芯片的至少一侧相邻。第一半导体芯片可以包括与第一半导体芯片的第一表面相邻的第一电路层。第二半导体芯片和所述多个导电柱可以连接到第一半导体芯片的第一表面。

[0006]

根据本发明构思的一些示例实施例,一种半导体封装件可以包括:第一半导体芯片;多个第二半导体芯片,位于第一半导体芯片的第一表面上,并且彼此水平地间隔开;以及多个导电柱,位于第一半导体芯片的第一表面上,并且位于所述多个第二半导体芯片之间。所述多个第二半导体芯片和所述多个导电柱可以连接到第一半导体芯片的第一表面。

[0007]

根据本发明构思的一些示例实施例,一种半导体封装件可以包括:下结构;第一半导体芯片,位于下结构上;第二半导体芯片,位于下结构与第一半导体芯片之间;以及多个导电柱,位于下结构与第一半导体芯片之间。所述多个导电柱可以与第二半导体芯片的至少一侧相邻。第二半导体芯片和所述多个导电柱可以连接到第一半导体芯片的第一表面。第一半导体芯片的第一表面面对下结构。

附图说明

[0008]

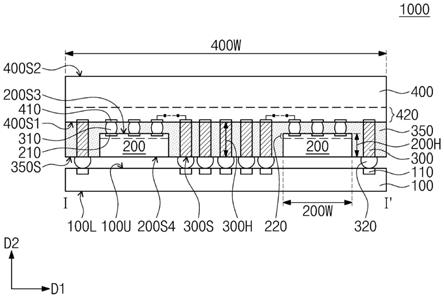

图1示出了示出根据本发明构思的一些示例实施例的半导体封装件的平面图。

[0009]

图2示出了沿图1的线i-i'截取的剖视图。

[0010]

图3至图7示出了沿图1的线i-i'截取的剖视图,所述剖视图示出了根据本发明构思的一些示例实施例的半导体封装件。

[0011]

图8至图10示出了示出制造根据本发明构思的一些示例实施例的半导体封装件的方法的剖视图。

[0012]

图11和图12示出了示出制造根据本发明构思的一些示例实施例的半导体封装件的方法的剖视图。

[0013]

图13至图16示出了沿图1的线i-i'截取的剖视图,所述剖视图示出了根据本发明构思的一些示例实施例的半导体封装件。

[0014]

图17示出了示出制造根据本发明构思的一些示例实施例的半导体封装件的方法的剖视图。

[0015]

图18示出了示出制造根据发明构思的一些示例实施例的半导体封装件的方法的剖视图。

[0016]

图19示出了示出根据本发明构思的一些示例实施例的半导体封装件的剖视图。

[0017]

图20示出了示出根据本发明构思的一些示例实施例的半导体封装件的剖视图。

[0018]

图21示出了示出根据本发明构思的一些示例实施例的半导体封装件的剖视图。

具体实施方式

[0019]

现在将在下面参照附图详细地描述本发明构思的一些示例实施例。

[0020]

图1示出了示出根据本发明构思的一些示例实施例的半导体封装件1000的平面图。图2示出了沿图1的线i-i'截取的剖视图。

[0021]

参照图1和图2,第一半导体芯片400可以设置在基底100上。第一半导体芯片400可以具有彼此背对的第一表面400s1和第二表面400s2,并且可以包括与第一表面400s1相邻的第一电路层420。第一电路层420可以包括集成电路。第一半导体芯片400可以设置为使第一表面400s1面对基底100的顶表面100u。第一半导体芯片400可以包括设置在第一表面400s1上的第一芯片垫(pad,或称为“焊盘”)410。第一芯片垫410可以包括导电材料。第一半导体芯片400可以是逻辑芯片或存储器芯片。

[0022]

基底100可以是例如印刷电路板(pcb)。基底100可以包括基底垫110,并且基底垫110可以设置在基底100的顶表面100u上。基底垫110可以包括导电材料。外部端子(未示出)可以设置在基底100的底表面100l上,并且基底垫110可以通过基底100中的内部布线线路电连接到外部端子。

[0023]

第二半导体芯片200可以设置在基底100与第一半导体芯片400之间。第二半导体芯片200可以设置在第一半导体芯片400的第一表面400s1上并且连接到第一半导体芯片400的第一表面400s1。在一些示例实施例中,多个第二半导体芯片200可以放置在基底100与第一半导体芯片400之间。多个第二半导体芯片200可以设置在第一半导体芯片400的第一表面400s1上并且可以沿着第一方向d1彼此水平地间隔开。多个第二半导体芯片200中的每个可以连接到第一半导体芯片400的第一表面400s1。

[0024]

第二半导体芯片200可以具有彼此背对的第三表面200s3和第四表面200s4,并且可以包括与第三表面200s3相邻的第二电路层220。第二电路层220可以包括集成电路。第二半导体芯片200可以设置为使第三表面200s3面对第一半导体芯片400的第一表面400s1。第二半导体芯片200可以包括设置在第三表面200s3上的第二芯片垫210。第二芯片垫210可以包括导电材料。

[0025]

连接件310可以设置在第一半导体芯片400与第二半导体芯片200之间,并且可以连接到对应的第二芯片垫210。连接件310可以结合到第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410。连接件310可以包括导电材料,并且可以具有焊球形状、凸块形状和柱形形状中的一种或更多种形状。第二半导体芯片200可以通过第二芯片垫210、连接件310和对应的第一芯片垫410电连接到第一半导体芯片400。第二半导体芯片200的第四表面200s4可以面对基底100的顶表面100u,并且可以与基底100的顶表面100u间隔开。

[0026]

第二半导体芯片200可以是逻辑芯片或存储器芯片。例如,第一半导体芯片400可以是逻辑芯片,并且第二半导体芯片200可以是存储器芯片。在一些示例实施例中,多个第二半导体芯片200中的至少一个可以被无源器件(例如,电容器)代替。

[0027]

第一半导体芯片400和第二半导体芯片200中的每个可以具有沿着第一方向d1的宽度。第一半导体芯片400可以具有比第二半导体芯片200的宽度200w大的宽度400w。在一些示例实施例中,第一半导体芯片400的宽度400w可以比多个第二半导体芯片200的宽度200w的总和大。

[0028]

多个导电柱300可以设置在基底100与第一半导体芯片400之间。在第一半导体芯片400的第一表面400s1上,导电柱300可以与第二半导体芯片200的至少一侧相邻放置。在一些示例实施例中,导电柱300可以设置在多个第二半导体芯片200之间。导电柱300可以在第一半导体芯片400的第一表面400s1上沿着第一方向d1彼此水平地间隔开。导电柱300中的每个可以连接到第一半导体芯片400的第一表面400s1。例如,导电柱300可以连接到第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410。导电柱300可以包括金属(例如,铜)。

[0029]

第二半导体芯片200和每个导电柱300可以具有它们的沿着与第一半导体芯片400的第一表面400s1垂直的第二方向d2的高度。在一些示例实施例中,导电柱300中的每个可以具有比第二半导体芯片200的高度200h大的高度300h。导电柱300中的每个可以具有面对基底100的顶表面100u且与基底100的顶表面100u间隔开的表面300s。导电柱300中的每个的表面300s可以定位在自第一半导体芯片400的第一表面400s1与第二半导体芯片200的第四表面200s4的水平基本上相同的水平处。

[0030]

模制层350可以设置在基底100与第一半导体芯片400之间,并且可以覆盖第二半导体芯片200的横向表面和导电柱300的横向表面,从而使第二半导体芯片200和导电柱300分离。模制层350可以在第一半导体芯片400与第二半导体芯片200之间延伸,从而覆盖连接件310。在一些示例实施例中,模制层350可以与基底100的顶表面100u间隔开,并且可以具有与第二半导体芯片200的第四表面200s4以及与导电柱300中的每个的表面300s基本上共面的表面350s。模制层350可以不覆盖而是暴露第二半导体芯片200的第四表面200s4和导电柱300中的每个的表面300s。模制层350可以包括介电材料(例如,环氧类模制化合物)。

[0031]

多个凸块320可以设置在基底100与导电柱300之间,并且可以连接到导电柱300。导电柱300中的每个可以穿透模制层350,并且可以具有与凸块320中的对应的一个凸块320的连接。凸块320可以连接到基底垫110。导电柱300中的每个可以通过对应的凸块320连接到基底100。凸块320可以包括导电材料。

[0032]

第一半导体芯片400可以通过导电柱300电连接到基底100。在一些示例实施例中,第二半导体芯片200可以与基底100间隔开。在这种情况下,第二半导体芯片200可以通过第

一半导体芯片400中的内部布线线路连接到对应的导电柱300,并且可以通过对应的导电柱300电连接到基底100。

[0033]

根据一些示例实施例,半导体封装件1000可以包括堆叠在基底100上的第一半导体芯片400和第二半导体芯片200。半导体封装件1000可以在其上部中设置有第一半导体芯片400,第一半导体芯片400的宽度400w比第二半导体芯片200的宽度200w大。因此,热量可以容易地从第一半导体芯片400向外排放。此外,半导体封装件1000可以包括用于第一半导体芯片400与基底100之间的电连接的导电柱300。因为第一半导体芯片400通过导电柱300电连接到基底100,所以第一半导体芯片400可以在其中不需要贯穿电极。结果,可以提供一种半导体封装件,所述半导体封装件能够容易地使多个半导体芯片堆叠并且具有优异的可靠性。

[0034]

图3示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。为了描述的简洁,以下将集中于与上面参照图1和图2讨论的半导体封装件1000的不同。

[0035]

参照图1和图3,底部填充层370可以设置在第一半导体芯片400与第二半导体芯片200之间,并且可以覆盖连接件310。底部填充层370可以覆盖第二半导体芯片200的第三表面200s3,并且可以填充连接件310之间的间隙。底部填充层370可以局部地设置在第二半导体芯片200的第三表面200s3上,并且可以与模制层350接触。底部填充层370可以包括诸如环氧树脂的介电聚合物材料。

[0036]

图4示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。为了描述的简洁,以下将集中于与以上参照图1和图2讨论的半导体封装件1000的不同。

[0037]

参照图1和图4,第二半导体芯片200可以设置为使第三表面200s3面对第一半导体芯片400的第一表面400s1,并且可以连接到第一半导体芯片400的第一表面400s1。第二半导体芯片200的第四表面200s4可以面对基底100的顶表面100u,并且与基底100的顶表面100u间隔开。导电柱300中的每个的表面300s可以面对基底100的顶表面100u,并且可以与基底100的顶表面100u间隔开。在一些示例实施例中,导电柱300中的每个的表面300s可以被定位为距离第一半导体芯片400的第一表面400s1比距离第二半导体芯片200的第四表面200s4更远。

[0038]

在一些示例实施例中,模制层350可以覆盖第二半导体芯片200的横向表面和导电柱300的横向表面,并且也可以覆盖第二半导体芯片200的第四表面200s4。模制层350可以包封第二半导体芯片200。模制层350可以与基底100的顶表面100u间隔开,并且模制层350的表面350s可以与导电柱300中的每个的表面300s基本上共面。

[0039]

图5示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。为了描述的简洁,以下将集中于与上面参照图1和图2讨论的半导体封装件1000的不同。

[0040]

参照图1和图5,第二半导体芯片200可以被设置为连接到第一半导体芯片400的第一表面400s1。第二半导体芯片200的第三表面200s3可以面对第一半导体芯片400的第一表面400s1,第二半导体芯片200的第四表面200s4可以面对基底10的顶表面100u。在一些示例实施例中,第二半导体芯片200的第二电路层(见图2的220)可以与第二半导体芯片200的第

三表面200s3或第四表面200s4相邻。

[0041]

贯穿电极230可以设置在第二半导体芯片200中,并且导电垫240可以设置在第二半导体芯片200的第四表面200s4上。贯穿电极230中的每个可以穿透第二半导体芯片200,并且可以具有与第二芯片垫210中的对应的一个第二芯片垫210和导电垫240中的对应的一个导电垫240的连接。贯穿电极230和导电垫240可以包括导电材料。

[0042]

导电垫240中的每个可以具有面对基底100的顶表面100u且与基底100的顶表面100u间隔开的表面240s。导电柱300中的每个的表面300s可以面对基底100的顶表面100u,并且可以与基底100的顶表面100u间隔开。导电垫240中的每个的表面240s可以定位在自第一半导体芯片400的第一表面400s1与导电柱300中的每个的表面300s的水平基本上相同的水平处。

[0043]

模制层350可以覆盖第二半导体芯片200的横向表面和导电柱300的横向表面,并且可以延伸到第二半导体芯片200的第四表面200s4上从而覆盖导电垫240。模制层350可以与基底100的顶表面100u间隔开,并且模制层350的表面350s可以与导电垫240的表面240s以及与导电柱300的表面300s基本上上共面。模制层350可以不覆盖而是暴露导电垫240的表面240s和导电柱300的表面300s。

[0044]

多个凸块320可以设置在基底100与导电柱300之间以及基底100与导电垫240之间,并且可以连接到导电柱300和导电垫240。凸块320可以结合到基底垫110。导电柱300和导电垫240中的每个可以通过凸块320中的对应的一个凸块320连接到基底100。

[0045]

第一半导体芯片400可以通过导电柱300电连接到基底100。此外,贯穿电极230中的至少一个可以用于第一半导体芯片400与基底100之间的电连接。在这种情况下,第一半导体芯片400可以通过第二半导体芯片200中的贯穿电极230中的对应的贯穿电极230电连接到基底100。第二半导体芯片200可以通过贯穿电极230中的对应的贯穿电极230电连接到基底100。

[0046]

图6示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。为了描述的简洁,以下将集中于与上面参照图1和图2讨论的半导体封装件1000的不同。

[0047]

参照图1和图6,多个第二半导体芯片200可以设置在基底100与第一半导体芯片400之间。多个第二半导体芯片200可以放置在第一半导体芯片400的第一表面400s1上,并且可以沿着第一方向d1彼此水平地间隔开。多个第二半导体芯片200中的每个可以连接到第一半导体芯片400的第一表面400s1。多个第二半导体芯片200中的每个可以包括彼此背对的第三表面200s3和第四表面200s4。多个第二半导体芯片200中的每个的第三表面200s3可以面对第一半导体芯片400的第一表面400s1,并且多个第二半导体芯片200中的每个的第四表面200s4可以面对基底100的顶表面100u。多个第二半导体芯片200中的每个可以包括第二电路层220。包括在多个第二半导体芯片200中的一个第二半导体芯片200a中的第二电路层220可以与第三表面200s3或第四表面200s4相邻。包括在多个第二半导体芯片200中的另一第二半导体芯片200b中的第二电路层220可以与第三表面200s3相邻。

[0048]

贯穿电极230可以设置在多个第二半导体芯片200中的一个第二半导体芯片200a中,并且导电垫240可以设置在多个第二半导体芯片200中的一个第二半导体芯片200a的第四表面200s4上。贯穿电极230中的每个可以穿透多个第二半导体芯片200中的一个第二半

导体芯片200a,并且可以具有与第二芯片垫210中的对应的一个第二芯片垫210以及与导电垫240中的对应的一个导电垫240的连接。可以在多个第二半导体芯片200的第二半导体芯片200b上既不设置贯穿电极230也不设置导电垫240。

[0049]

导电垫240中的每个可以具有面对基底100的顶表面100u并且与基底100的顶表面100u间隔开的表面240s。导电柱300中的每个的表面300s可以面对基底100的顶表面100u,并且可以与基底100的顶表面100u间隔开。导电垫240中的每个的表面240s可以定位在自第一半导体芯片400的第一表面400s1与导电柱300中的每个的表面300s的水平基本上相同的水平处。多个第二半导体芯片200中的第二半导体芯片200b的第四表面200s4可以面对基底100的顶表面100u,并且可以与基底100的顶表面100u间隔开。多个第二半导体芯片200中的第二半导体芯片200b的第四表面200s4可以定位在自第一半导体芯片400的第一表面400s1与导电柱300中的每个的表面300s的水平基本上相同的水平处,但是本发明构思不限于此。

[0050]

模制层350可以覆盖多个第二半导体芯片200和导电柱300。模制层350可以延伸到多个第二半导体芯片200中的一个第二半导体芯片200a的第四表面200s4上,从而覆盖导电垫240。模制层350可以与基底100的顶表面100u间隔开,并且模制层350的表面350s可以与导电垫240的表面240s以及与导电柱300的表面300s基本上共面。模制层350可以不覆盖而是暴露导电垫240的表面240s和导电柱300的表面300s。在一些示例实施例中,模制层350的表面350s可以与多个第二半导体芯片200的第二半导体芯片200b的第四表面200s4基本上共面。在这种情况下,模制层350可以不覆盖而是暴露多个第二半导体芯片200中的第二半导体芯片200b的第四表面200s4。

[0051]

多个凸块320可以设置在基底100与导电柱300之间以及基底100与导电垫240之间,并且可以连接到导电柱300和导电垫240。凸块320可以结合到基底垫110。导电柱300和导电垫240中的每个可以通过凸块320中的对应的一个凸块320连接到基底100。

[0052]

第一半导体芯片400可以通过导电柱300电连接到基底100。此外,贯穿电极230中的至少一个可以用于第一半导体芯片400与基底100之间的电连接。在这种情况下,第一半导体芯片400可以通过多个第二半导体芯片200中的一个第二半导体芯片200a中的贯穿电极230中的对应的贯穿电极230电连接到基底100。

[0053]

多个第二半导体芯片200中的一个第二半导体芯片200a可以通过贯穿电极230中的对应的贯穿电极230电连接到基底100。多个第二半导体芯片200中的第二半导体芯片200b可以不包括贯穿电极230。在这种情况下,多个第二半导体芯片200中的第二半导体芯片200b可以通过第一半导体芯片400中的内部布线线路连接到导电柱300中的对应的导电柱300,并且可以通过对应的导电柱300电连接到基底100。

[0054]

图7示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。为了描述的简洁,以下将集中于与上面参照图1和图2讨论的半导体封装件1000的不同。

[0055]

参照图1和图7,多个第二半导体芯片200可以设置在基底100与第一半导体芯片400之间。多个第二半导体芯片200可以设置在第一半导体芯片400的第一表面400s1上,并且可以沿着第一方向d1彼此水平地间隔开。多个第二半导体芯片200中的每个可以连接到第一半导体芯片400的第一表面400s1。

[0056]

多个第二半导体芯片200中的一个第二半导体芯片200a可以包括沿着与第一半导

体芯片400的第一表面400s1垂直的第二方向d2堆叠的多个子半导体芯片202、204和206。子半导体芯片202、204和206中的每个可以是逻辑芯片或存储器芯片。贯穿电极230可以设置在多个第二半导体芯片200中的一个第二半导体芯片200a中,并且导电垫240可以设置在多个第二半导体芯片200中的一个第二半导体芯片200a的第四表面200s4上。贯穿电极230中的每个可以穿透子半导体芯片202、204和206,并且可以具有与第二芯片垫210中的对应的一个第二芯片垫210和导电垫240中的对应的一个导电垫240的连接。除了先前所提及的之外,根据一些示例实施例的半导体封装件1000可以与上面参照图1和图6讨论的半导体封装件1000基本上相同。此外,本领域普通技术人员可以认识到的是,多个子半导体芯片202、204和206可以存在于第二半导体芯片200a中的任何一个中,并且子半导体芯片的数量不限于所示出的数量。

[0057]

图8至图10示出了示出制造根据本发明构思的一些示例实施例的半导体封装件的方法的剖视图。为了避免对上面参照图1和图2讨论的半导体封装件的重复解释,将进行省略。

[0058]

参照图8,可以提供包括多个第一半导体芯片400的晶圆400wf。多个第一半导体芯片400可以对应地包括第一电路层420,并且第一电路层420可以与晶圆400wf的顶表面400u相邻设置。第一电路层420可以包括集成电路。多个第一半导体芯片400可以包括第一芯片垫410,并且第一芯片垫410可以与晶圆400wf的顶表面400u相邻设置。第一芯片垫410可以电连接到第一电路层420。

[0059]

可以在晶圆400wf的顶表面400u上形成多个导电柱300。可以预先在晶圆400wf的顶表面400u上限定芯片安装区域400r,并且可以在除了晶圆400wf的芯片安装区域400r之外的顶表面400u上形成导电柱300。可以将导电柱300连接到第一芯片垫410中的对应的第一芯片垫410。可以通过采用例如电镀工艺来形成导电柱300。例如,导电柱300的形成可以包括以下步骤:在晶圆400wf的顶表面400u上形成具有开口的光致抗蚀剂图案,该开口暴露形成有导电柱300的区域;在光致抗蚀剂图案上形成种子层;以及对种子层执行电镀工艺以形成导电柱300。在形成导电柱300之后,可以去除光致抗蚀剂图案。

[0060]

参照图9,在芯片安装区域400r上,可以在晶圆400wf的顶表面400u上形成连接件310。可以在第一芯片垫410中的对应的第一芯片垫410上形成连接件310,并且可以使连接件310连接到对应的第一芯片垫410。

[0061]

可以在对应的芯片安装区域400r上设置多个第二半导体芯片200。多个第二半导体芯片200中的每个可以包括第二芯片垫210,并且第二芯片垫210可以与第二半导体芯片200中的每个的一个表面相邻设置。可以在晶圆400wf的顶表面400u上设置第二半导体芯片200中的每个,使得第二芯片垫210可以与连接件310中的对应的连接件310接触。

[0062]

可以在晶圆400wf的顶表面400u上形成模制层350,并且可以使模制层350覆盖第二半导体芯片200和导电柱300。在一些示例实施例中,模制层350可以在晶圆400wf与第二半导体芯片200中的每个之间延伸,从而覆盖连接件310。可以使模制层350填充连接件310之间的空间。在一些示例实施例中,在形成模制层350之前,可以形成图3中讨论的底部填充层370,以填充晶圆400wf与第二半导体芯片200中的每个之间的空间并且覆盖连接件310。

[0063]

参照图10,可以使模制层350经历研磨工艺以去除模制层350的上部。研磨工艺可以暴露导电柱300中的每个的一个表面。在一些示例实施例中,研磨工艺可以暴露第二半导

体芯片200中的每个的一个表面。在一些示例实施例中,如图4中所讨论的,可以不通过研磨工艺暴露第二半导体芯片200,而是可以用模制层350覆盖第二半导体芯片200。

[0064]

可以在模制层350上形成多个凸块320。可以在对应的导电柱300上形成凸块320,并且可以使凸块320连接到对应的导电柱300。通过上面提及的工艺,可以形成堆叠结构ss。切割工艺sp可以将堆叠结构ss划分为多个芯片堆叠件cs。切割工艺sp可以将晶圆400wf分离为多个第一半导体芯片400,并且芯片堆叠件cs可以包括对应的第一半导体芯片400。芯片堆叠件cs中的每个可以包括堆叠在第一半导体芯片400上的一个或更多个第二半导体芯片200,并且也可以包括形成在第一半导体芯片400上的导电柱300。

[0065]

返回参照图1和图2,可以将芯片堆叠件cs中的一个芯片堆叠件cs设置在基底100上。基底100可以是例如印刷电路板(pcb)。基底100可以包括设置在基底100的顶表面100u上的基底垫110。可以将芯片堆叠件cs堆叠在基底100的顶表面100u上,使得凸块320可以与基底垫110中的对应的基底垫110接触。基底100和芯片堆叠件cs可以构成半导体封装件1000。

[0066]

图11和图12示出了示出制造根据本发明构思的一些示例实施例的半导体封装件的方法的剖视图。以下将集中于与上面参照图8至图10讨论的半导体封装件制造方法的不同。

[0067]

首先,如上面参照图8所讨论的,可以提供包括多个第一半导体芯片400的晶圆400wf,并且可以在晶圆400wf的顶表面400u上形成多个导电柱300。可以在除了晶圆400wf的芯片安装区域400r之外的顶表面400u上形成导电柱300。

[0068]

参照图11,在芯片安装区域400r上,可以在晶圆400wf的顶表面400u上形成连接件310。可以在第一芯片垫410中的对应的第一芯片垫410上形成连接件310,并且可以将连接件310连接到对应的第一芯片垫410。

[0069]

可以在对应的芯片安装区域400r上设置多个第二半导体芯片200。多个第二半导体芯片200中的每个可以包括第二芯片垫210,并且第二芯片垫210可以与第二半导体芯片200中的每个的一个表面相邻设置。在一些示例实施例中,第二半导体芯片200中的每个可以包括穿透其的贯穿电极230,并且也可以包括设置在第二半导体芯片200中的每个的另一表面上的导电垫240。贯穿电极230可以穿透第二半导体芯片200中的每个,并且可以具有与第二芯片垫210和导电垫240的连接。可以在晶圆400wf的顶表面400u上设置第二半导体芯片200中的每个,使得第二芯片垫210可以与连接件310中的对应的连接件310接触。可以在晶圆400wf的顶表面400u上形成模制层350,并且可以使模制层350覆盖第二半导体芯片200和导电柱300。

[0070]

参照图12,可以使模制层350经历研磨工艺以去除模制层350的上部。研磨工艺可以暴露导电柱300中的每个的一个表面和导电垫240中的每个的一个表面。可以在模制层350上形成多个凸块320。可以在对应的导电柱300和对应的导电垫240上形成凸块320,并且可以使凸块320连接到对应的导电柱300和对应的导电垫240。通过上面提及的工艺,可以形成堆叠结构ss。切割工艺sp可以将堆叠结构ss划分为多个芯片堆叠件cs。其他工艺与上面参照图1、图2和图8至图10讨论的半导体封装件制造方法基本上相同。

[0071]

图13示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。

[0072]

参照图1和图13,第二半导体芯片200的第二芯片垫210可以与第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410直接接触。在一些示例实施例中,可以不存在上面参照图1和图2讨论的连接件310。第二半导体芯片200的导电柱300中的每个可以具有沿着与第一半导体芯片400的第一表面400s1垂直的第二方向d2的高度。在一些示例实施例中,导电柱300中的每个可以具有与第二半导体芯片200的高度200h基本上相同的高度300h。除了前面提及的之外,根据一些示例实施例的半导体封装件1000可以与上面参照图1和图2讨论的半导体封装件1000基本相同。

[0073]

图14示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。

[0074]

参照图1和图14,第二半导体芯片200的第二芯片垫210可以与第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410直接接触。在一些示例实施例中,可以不存在上面参照图1和图2讨论的连接件310。

[0075]

第二半导体芯片200的导电柱300中的每个可以具有沿着与第一半导体芯片400的第一表面400s1垂直的第二方向d2的高度。在一些示例实施例中,导电柱300中的每个可以具有比第二半导体芯片200的高度200h大的高度300h。导电柱300中的每个的表面300s可以面对基底100的顶表面100u,并且可以与基底100的顶表面100u间隔开。导电柱300中的每个的表面300s可以定位为距离第一半导体芯片400的第一表面400s1比距离第二半导体芯片200的第四表面200s4更远。除了前面提及的之外,根据一些示例实施例的半导体封装件1000可以与上面参照图1和图4讨论的半导体封装件1000基本上相同。

[0076]

图15示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。

[0077]

参照图1和图15,第二半导体芯片200的第二芯片垫210可以与第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410直接接触。在一些示例实施例中,可以不存在上面参照图1和图2讨论的连接件310。除了前面提及的之外,根据一些示例实施例的半导体封装件1000可以与上面参照图1和图5讨论的半导体封装件1000基本上相同。

[0078]

图16示出了沿图1的线i-i'截取的剖视图,该剖视图示出了根据本发明构思的一些示例实施例的半导体封装件1000的示例。

[0079]

参照图1和图16,多个第二半导体芯片200可以设置在基底100与第一半导体芯片400之间。多个第二半导体芯片200中的每个可以连接到第一半导体芯片400的第一表面400s1。多个第二半导体芯片200中的每个的第二芯片垫210可以与第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410直接接触。除了前面提及的之外,根据一些示例实施例的半导体封装件1000可以与上面参照图1和图6讨论的半导体封装件1000基本上相同。

[0080]

图17示出了示出制造根据本发明构思的一些示例实施例的半导体封装件的方法的剖视图。以下将集中于与上面参照图8至图10讨论的半导体封装件制造方法的不同。

[0081]

首先,如上面参照图8所讨论的,可以提供包括多个第一半导体芯片400的晶圆400wf,并且可以在晶圆400wf的顶表面400u上形成多个导电柱300。可以在除了晶圆400wf的芯片安装区域400r之外的顶表面400u上形成导电柱300。

[0082]

参照图17,可以在对应的芯片安装区域400r上设置多个第二半导体芯片200。多个第二半导体芯片200中的每个可以包括第二芯片垫210,并且第二芯片垫210可以与第二半

导体芯片200中的每个的一个表面相邻设置。可以在晶圆400wf的顶表面400u上堆叠第二半导体芯片200中的每个,使得第二芯片垫210可以与第一芯片垫410中的对应的第一芯片垫410直接接触。由于热处理,可以将第二半导体芯片200中的每个的第二芯片垫210结合(或键合)到对应的第一芯片垫410。可以在晶圆400wf的顶表面400u上形成模制层350,并且可以使模制层350覆盖第二半导体芯片200和导电柱300。其它工艺与上面参照图1、图2和图8至图10讨论的半导体封装件制造方法基本上相同。

[0083]

图18示出了示出根据本发明构思的一些示例实施例的制造半导体封装件的方法的剖视图。以下将集中于与上面参照图8至图10讨论的半导体封装件制造方法的不同。

[0084]

首先,如上面参照图8所讨论的,可以提供包括多个第一半导体芯片400的晶圆400wf,并且可以在晶圆400wf的顶表面400u上形成多个导电柱300。可以在除了晶圆400wf的芯片安装区域400r之外的顶表面400u上形成导电柱300。

[0085]

参照图18,可以在对应的芯片安装区域400r上设置多个第二半导体芯片200。多个第二半导体芯片200中的每个可以包括第二芯片垫210,并且第二芯片垫210可以与第二半导体芯片200中的每个的一个表面相邻设置。在一些示例实施例中,第二半导体芯片200中的每个可以包括穿透其的贯穿电极230,并且也可以包括设置在第二半导体芯片200中的每个的另一表面上的导电垫240。贯穿电极230可以穿透第二半导体芯片200中的每个,并且可以具有与第二芯片垫210和导电垫240的连接。可以在晶圆400wf的顶表面400u上堆叠第二半导体芯片200中的每个,使得第二芯片垫210可以与第一芯片垫410中的对应的第一芯片垫410直接接触。由于热处理,第二半导体芯片200中的每个的第二芯片垫210可以结合(或键合)到对应的第一芯片垫410。可以在晶圆400wf的顶表面400u上形成模制层350,并且可以使模制层350覆盖第二半导体芯片200和导电柱300。其它工艺与上面参照图1、图2和图8至图10讨论的半导体封装件制造方法基本上相同。

[0086]

图19示出了示出根据本发明构思的一些示例实施例的半导体封装件1100的剖视图。为了描述的简洁,以下将集中于与上面参照图1和图2讨论的半导体封装件1000的不同。

[0087]

参照图19,第一半导体芯片400可以设置在再分布层100r上。第一半导体芯片400可以设置为使第一表面400s1面对再分布层100r的顶表面100ru。再分布层100r可以包括再分布图案150。再分布图案150可以包括导电材料。为了说明的简洁,再分布图案150的部分由虚线指示。再分布层100r和第一半导体芯片400均可以具有在第一方向d1上的宽度。再分布层100r可以具有比第一半导体芯片400的宽度400w大的宽度100rw。在本说明书中,再分布层100r可以被称为基底。

[0088]

第二半导体芯片200可以设置在再分布层100r与第一半导体芯片400之间。第二半导体芯片200可以设置在第一半导体芯片400的第一表面400s1上并且连接到第一半导体芯片400的第一表面400s1。在一些示例实施例中,多个第二半导体芯片200可以设置在再分布层100r与第一半导体芯片400之间。多个第二半导体芯片200可以设置在第一半导体芯片400的第一表面400s1上,并且可以沿着与第一表面400s1平行的第一方向d1彼此水平地间隔开。多个第二半导体芯片200中的每个可以连接到第一半导体芯片400的第一表面400s1。

[0089]

在一些示例实施例中,贯穿电极230可以设置在多个第二半导体芯片200中的至少一个中,并且导电垫240可以设置在多个第二半导体芯片200中的至少一个的第四表面200s4上。贯穿电极230中的每个可以穿透多个第二半导体芯片200中的至少一个,并且可以

具有与第二芯片垫210中的对应的一个第二芯片垫210和导电垫240中的对应的一个导电垫240的连接。在一些示例实施例中,贯穿电极230和导电垫240都可以不设置在多个第二半导体芯片200中的另一个上,但是本发明构思不限于此。

[0090]

多个导电柱300可以设置在再分布层100r与第一半导体芯片400之间。导电柱300中的每个可以连接到第一半导体芯片400的第一表面400s1。例如,导电柱300可以连接到第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410。

[0091]

模制层350可以设置在再分布层100r与第一半导体芯片400之间,并且可以覆盖第二半导体芯片200的横向表面和导电柱300的横向表面。模制层350可以延伸到多个第二半导体芯片200中的每个的第四表面200s4上,从而覆盖第四表面200s4。模制层350可以延伸到多个第二半导体芯片200中的至少一个的第四表面200s4上,从而覆盖导电垫240。模制层350可以与再分布层100r的顶表面100ru接触。导电柱300和导电垫240可以均穿透模制层350的至少一部分并且具有与再分布图案150中的对应的再分布图案150的连接。

[0092]

多个凸块320可以设置在再分布层100r的底表面100rl上。多个凸块320中的每个可以连接到再分布图案150中的对应的一个再分布图案150。导电柱300和导电垫240可以均通过对应的再分布图案150电连接到多个凸块320中的对应的凸块320。

[0093]

第一半导体芯片400可以通过导电柱300电连接到再分布层100r。此外,贯穿电极230中的至少一个可以用于第一半导体芯片400与再分布层100r之间的电连接。在这种情况下,第一半导体芯片400可以通过多个第二半导体芯片200中的至少一个第二半导体芯片200中的贯穿电极230中的对应的贯穿电极230电连接到再分布层100r。

[0094]

多个第二半导体芯片200中的至少一个可以通过贯穿电极230中的对应的贯穿电极230电连接到再分布层100r。多个第二半导体芯片200中的另一个可以通过第一半导体芯片400中的内部布线线路连接到导电柱300中的对应的导电柱300,并且可以通过对应的导电柱300电连接到再分布层100r。

[0095]

再分布层100r上可以设置有覆盖第一半导体芯片400和模制层350的附加模制层500。附加模制层500可以沿着第一半导体芯片400和模制层350的侧壁延伸,并且可以与再分布层100r的顶表面100ru接触。附加模制层500可以包括介电材料(例如,环氧类模制化合物)。在一些示例实施例中,可以省略附加模制层500。根据一些示例实施例的半导体封装件1100可以包括扇出晶圆级封装件。

[0096]

图20示出了示出根据本发明构思的一些示例实施例的半导体封装件1200的剖视图。为了描述的简洁,以下将集中于与上面参照图1和图2讨论的半导体封装件1000的不同。

[0097]

参照图20,下半导体芯片600可以设置在基底100上。基底100可以是例如印刷电路板(pcb)。基底100可以包括基底垫110,并且基底垫110可以设置在基底100的顶表面100u上。

[0098]

下半导体芯片600可以具有第五表面600s5和第六表面600s6,并且可以包括设置在第五表面600s5上的下芯片垫610。下芯片垫610可以包括导电材料。下半导体芯片600可以设置为使第六表面600s6面对基底100的顶表面100u。下半导体芯片600可以是逻辑芯片或存储器芯片。

[0099]

下贯穿电极650可以设置在下半导体芯片600中,并且下凸块620可以设置在下半导体芯片600的第六表面600s6上。下贯穿电极650中的每个可以穿透下半导体芯片600,并

且可以具有与下芯片垫610中的对应的一个下芯片垫610和下凸块620中的对应的一个下凸块620的连接。下凸块620中的每个可以连接到基底垫110中的对应的一个基底垫110。下贯穿电极650和下凸块620可以包括导电材料。

[0100]

第一半导体芯片400可以设置在下半导体芯片600上。第一半导体芯片400可以设置为使第一表面400s1面对下半导体芯片600的第五表面600s5。第二半导体芯片200可以设置在下半导体芯片600与第一半导体芯片400之间。第二半导体芯片200可以设置在第一半导体芯片400的第一表面400s1上,并且可以连接到第一半导体芯片400的第一表面400s1。在一些示例实施例中,多个第二半导体芯片200可以设置在下半导体芯片600与第一半导体芯片400之间。多个第二半导体芯片200可以设置在第一半导体芯片400的第一表面400s1上,并且可以沿着与第一表面400s1平行的第一方向d1彼此水平地间隔开。多个第二半导体芯片200中的每个可以连接到第一半导体芯片400的第一表面400s1。

[0101]

在一些示例实施例中,贯穿电极230可以设置在多个第二半导体芯片200中的至少一个中,并且导电垫240可以设置在多个第二半导体芯片200中的至少一个的第四表面200s4上。贯穿电极230中的每个可以穿透多个第二半导体芯片200中的至少一个,并且可以具有与第二芯片垫210中的对应的一个第二芯片垫210和导电垫240中的对应的一个导电垫240的连接。在一些示例实施例中,贯穿电极230和导电垫240都可以不设置在多个第二半导体芯片200中的另一个上,但是本发明构思不限于此。

[0102]

多个导电柱300可以设置在下半导体芯片600与第一半导体芯片400之间。导电柱300中的每个可以连接到第一半导体芯片400的第一表面400s1。例如,导电柱300可以连接到第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410。

[0103]

模制层350可以设置在下半导体芯片600与第一半导体芯片400之间,并且可以覆盖第二半导体芯片200和导电柱300。模制层350可以延伸到多个第二半导体芯片200中的至少一个的第四表面200s4上,从而覆盖导电垫240。模制层350可以与下半导体芯片600的第五表面600s5间隔开。

[0104]

多个凸块320可以设置在下半导体芯片600与导电柱300之间以及下半导体芯片600与导电垫240之间,并且可以连接到导电柱300和导电垫240。凸块320可以连接到下半导体芯片600的下芯片垫610。导电柱300和导电垫240可以均通过凸块320中的对应的一个凸块320连接到下半导体芯片600。

[0105]

第一半导体芯片400可以通过导电柱300电连接到下半导体芯片600。贯穿电极230中的至少一个可以用于第一半导体芯片400与下半导体芯片600之间的电连接。在这种情况下,第一半导体芯片400可以通过位于多个第二半导体芯片200中的至少一个第二半导体芯片200中的贯穿电极230中的对应的贯穿电极230电连接到下半导体芯片600。此外,下贯穿电极650中的至少一个可以用于第一半导体芯片400与基底100之间的电连接。在这种情况下,第一半导体芯片400可以通过下半导体芯片600中的下贯穿电极650中的对应的下贯穿电极650电连接到基底100。

[0106]

多个第二半导体芯片200中的至少一个可以通过贯穿电极230中的对应的贯穿电极230电连接到下半导体芯片600。多个第二半导体芯片200中的另一个可以通过第一半导体芯片400中的内部布线线路连接到导电柱300中的对应的导电柱300,并且可以通过对应的导电柱300电连接到下半导体芯片600。下贯穿电极650中的一个或更多个可以用于基底

100与多个第二半导体芯片200之间的电连接。在这种情况下,多个第二半导体芯片200可以通过下半导体芯片600中的下贯穿电极650中的对应的下贯穿电极650电连接到基底100。下半导体芯片600可以通过下贯穿电极650中的对应的下贯穿电极650电连接到基底100。

[0107]

图21示出了示出根据本发明构思的一些示例实施例的半导体封装件1300的剖视图。为了描述的简洁,以下将集中于与上面参照图1和图2讨论的半导体封装件1000的不同。

[0108]

参照图21,可以提供下半导体封装件pkg。下半导体封装件pkg可以包括第一基底700和位于第一基底700上的半导体芯片800。第一基底700可以使再分布层或具有电路图案的印刷电路基底。第一基底700可以包括第一基底垫710。第一基底垫710可以包括导电材料。半导体芯片800可以包括设置在其底表面上的芯片垫810。第一基底700和半导体芯片800可以具有位于其间的对应地连接到芯片垫810的下连接件820。下连接件820可以连接到第一基底垫710中的对应的第一基底垫710。芯片垫810和下连接件820可以包括导电材料。下连接件820可以具有焊球形状、凸块形状和柱形形状中的一种或更多种形状。半导体芯片800可以包括集成电路(未示出),并且集成电路可以与半导体芯片800的底表面相邻。半导体芯片800可以是逻辑芯片或存储器芯片。

[0109]

下半导体封装件pkg可以包括第一基底700上的焊料结构850。焊料结构850可以与半导体芯片800水平地间隔开。焊料结构850可以连接到第一基底垫710中的对应的第一基底垫710。焊料结构850可以包括诸如锡、铅、银和/或其合金的导电材料。焊料结构850中的每个可以通过第一基底700中的内部布线线路电连接到外部端子或半导体芯片800。

[0110]

下半导体封装件pkg可以包括设置在半导体芯片800上的第二基底900。第二基底900可以是例如中介基底。第二基底900可以包括设置在第二基底900的底表面上的第一垫910,并且也可以包括设置在第二基底900的顶表面上的第二垫920。第二基底900可以在其中设置有将第一垫910电连接到第二垫920的布线线路。第一垫910和第二垫920可以包括诸如金属(例如,铜和/或铝)的导电材料。焊料结构850可以连接到第一垫910。第二基底900可以通过焊料结构850电连接到第一基底700和半导体芯片800。

[0111]

下半导体封装件pkg可以包括位于第一基底700与第二基底900之间的下模制层860。下模制层860可以覆盖半导体芯片800和焊料结构850。下模制层860可以在第一基底700与半导体芯片800之间延伸,从而包封下连接件820。下模制层860可以包括介电材料(例如,环氧类模制化合物)。

[0112]

第一半导体芯片400可以设置在下半导体封装件pkg的第二基底900上。第一半导体芯片400可以设置为使第一表面400s1面对第二基底900。第二半导体芯片200可以设置在第二基底900与第一半导体芯片400之间。在一些示例实施例中,多个第二半导体芯片200可以设置在第二基底900与第一半导体芯片400之间。

[0113]

在一些示例实施例中,贯穿电极230可以设置在多个第二半导体芯片200中的至少一个中,并且导电垫240可以设置在多个第二半导体芯片200中的至少一个的第四表面200s4上。贯穿电极230中的每个可以穿透多个第二半导体芯片200中的至少一个,并且可以具有与第二芯片垫210中的对应的一个第二芯片垫210和导电垫240中的对应的一个导电垫240的连接。在一些示例实施例中,贯穿电极230和导电垫240都可以不设置在多个第二半导体芯片200中的另一个上,但是本发明构思不限于此。

[0114]

多个导电柱300可以设置在第二基底900与第一半导体芯片400之间。导电柱300中

的每个可以连接到第一半导体芯片400的第一表面400s1。例如,导电柱300可以连接到第一半导体芯片400的第一芯片垫410中的对应的第一芯片垫410。

[0115]

模制层350可以设置在第二基底900与第一半导体芯片400之间,并且可以覆盖第二半导体芯片200和导电柱300。模制层350可以延伸到多个第二半导体芯片200中的至少一个的第四表面200s4上,从而覆盖导电垫240。模制层350可以与第二基底900间隔开。

[0116]

多个凸块320可以设置在第二基底900与导电柱300之间以及第二基底900与导电垫240之间,并且可以连接到导电柱300和导电垫240。凸块320可以连接到第二基底900的第二垫920。导电柱300和导电垫240可以均通过凸块320中的对应的一个凸块320与第二基底900连接。

[0117]

第一半导体芯片400可以通过导电柱300电连接到下半导体封装件pkg。贯穿电极230中的至少一个可以用于第一半导体芯片400与下半导体封装件pkg之间的电连接。在这种情况下,第一半导体芯片400可以通过多个第二半导体芯片200中的至少一个中的贯穿电极230中的对应的贯穿电极230电连接到下半导体封装件pkg。

[0118]

多个第二半导体芯片200中的至少一个可以通过贯穿电极230中的对应的贯穿电极230电连接到下半导体封装件pkg。多个第二半导体芯片200中的另一个可以通过第一半导体芯片400中的内部布线线路连接到导电柱300中的对应的导电柱300,并且可以通过对应的导电柱300电连接到下半导体封装件pkg。

[0119]

根据一些示例实施例,其的宽度相对大的第一半导体芯片400可以设置在半导体封装件1000/1100/1200/1300的上区域中。因此,热量可以容易地从第一半导体芯片400向外排放。此外,半导体封装件1000/1100/1200/1300可以包括使第一半导体芯片400电连接到下结构(例如,基底100、再分布层100r、下半导体芯片600或下半导体封装件pkg)的导电柱300。因为第一半导体芯片400通过导电柱300电连接到下结构,所以第一半导体芯片400可以在其中不需要贯穿电极。结果,半导体封装件可以能够以优异的可靠性容易地堆叠多个半导体芯片。

[0120]

上述描述提供了用于解释本发明构思的一些示例实施例。因此,本发明构思不限于上面描述的实施例,并且本领域普通技术人员将理解的是,在不脱离本发明构思的精神和必要特征的情况下,可以在其中进行形式和细节上的变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1