半导体结构及其形成方法与流程

1.本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

2.随着半导体集成电路(integrated circuit,ic)产业的快速成长,半导体技术在摩尔定律的驱动下持续地朝更小的工艺节点迈进,使得集成电路朝着体积更小、电路精密度更高、电路复杂度更高的方向发展。

3.在集成电路发展过程中,通常功能密度(即每一芯片的内连线结构的数量)逐渐增加的同时,几何尺寸(即利用工艺步骤可以产生的最小元件尺寸)逐渐减小,这相应增加了集成电路制造的难度和复杂度。

4.目前,在技术节点不断缩小的情况下,如何提高形成于晶圆上的图形与目标图形的匹配度成为了一种挑战。

技术实现要素:

5.本发明实施例解决的问题是提供一种半导体结构及其形成方法,提高图形传递的精度。

6.为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供基底,所述基底上形成有图形传递材料层;进行第一离子注入,向部分区域的所述图形传递材料层中掺杂第一离子,掺杂有所述第一离子的所述图形传递材料层作为第一掺杂掩膜层,所述第一掺杂掩膜层的排布方向为第一方向,与所述第一方向相垂直的方向为第二方向,所述第一离子注入适于增大所述图形传递材料层与所述第一掺杂掩膜层之间的刻蚀选择比;在所述第二方向上,在所述第一掺杂掩膜层两侧的所述图形传递材料层中形成第一沟槽,所述第一沟槽暴露出所述第一掺杂掩膜层在所述第二方向的侧壁;在所述第一沟槽的侧壁形成掩膜侧墙;形成所述掩膜侧墙后,进行第二离子注入,向所述第一掺杂掩膜层和第一沟槽露出的部分区域的所述图形传递材料层中掺杂第二离子,掺杂有所述第二离子的所述图形传递材料层作为第二掺杂掩膜层,所述第二离子注入适于增大所述图形传递材料层与所述第二掺杂掩膜层之间的刻蚀选择比;形成所述第二掺杂掩膜层后,去除剩余的所述图形传递材料层,形成多个分立的第二沟槽;以所述第一掺杂掩膜层、第二掺杂掩膜层和掩膜侧墙为掩膜,沿所述第一沟槽和第二沟槽刻蚀所述基底,形成目标图形。

7.相应的,本发明实施例提供一种半导体结构,包括:基底;图形传递材料,位于所述基底上;第一离子,位于部分区域的所述图形传递材料层中,掺杂有所述第一离子的所述图形传递材料层作为第一掺杂掩膜层,所述第一掺杂掩膜层的排布方向为第一方向,与所述第一方向相垂直的方向为第二方向,所述第一离子适于增大所述图形传递材料层与所述第一掺杂掩膜层之间的刻蚀选择比;第一沟槽,位于所述第一掺杂掩膜层在所述第二方向的两侧的所述图形传递材料层中,所述第一沟槽暴露出所述第一掺杂掩膜层在所述第二方向的侧壁;掩膜侧墙,位于所述第一沟槽的侧壁;第二离子,位于所述第一掺杂掩膜层和第一

沟槽露出的部分区域的所述图形传递材料层中,掺杂有所述第二离子的所述图形传递材料层作为第二掺杂掩膜层,所述第二离子适于增大所述图形传递材料层与所述第二掺杂掩膜层之间的刻蚀选择比;其中,未掺杂有所述第一离子和第二离子的剩余所述图形传递材料层用于占据第二沟槽的位置。

8.与现有技术相比,本发明实施例的技术方案具有以下优点:

9.本发明实施例利用第一离子注入形成第一掺杂掩膜层,在第二方向上使第一沟槽之间相隔离,利用第二离子注入形成第二掺杂掩膜层,且图形传递材料层与第一掺杂掩膜层、第二掺杂掩膜层之间的刻蚀选择比均较高,因此,能够通过去除剩余图形传递材料层的方式,在第二方向上使第二沟槽之间相隔离、在第一方向上使第二沟槽和第一沟槽之间相隔离;与通过直接刻蚀图形传递材料层以形成第一沟槽和第二沟槽的方案相比,离子注入的工艺灵活性、位置精度和尺寸精度均较高,且易于使第一掺杂掩膜层或第二掺杂掩膜层获得较小的尺寸,有利于精确控制所述第一掺杂掩膜层和第二掺杂掩膜层的尺寸和位置,从而能够精确控制所述第一沟槽和第二沟槽的尺寸和位置,且所形成的第一沟槽和第二沟槽即为满足图形设计需求的图形,进而提高了目标图形的图形精度,相应提高了图形传递的精度。

附图说明

10.图1至图15是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

具体实施方式

11.由背景技术可知,在技术节点不断缩小的情况下,如何提高形成于晶圆上的目标图形与设计图形的匹配度成为了一种挑战。

12.经研究发现,随着技术节点的不断缩小,光刻胶图形的间距也不断减小。然而,在光刻工艺的影响下,当相邻光刻图形的间距小于光刻工艺的临界距离(threshold distance)时,光刻胶图形容易出现变形、失真等问题。当所述光刻胶图形转移至待刻蚀层中以形成目标图形(例如:沟槽)时,相应会降低所述目标图形的图形精度,从而导致图形传递的精度下降。

13.为了解决所述技术问题,本发明实施例对部分区域的图形传递材料层进行第一离子注入形成第一掺杂掩膜层,第一掺杂掩膜层在第二方向上使第一沟槽之间相隔离,对第一掺杂掩膜层和第一沟槽露出的部分区域的图形传递材料层进行第二离子注入形成第二掺杂掩膜层,且图形传递材料层与第一掺杂掩膜层、第二掺杂掩膜层之间的刻蚀选择比均较高,因此,在形成第二掺杂掩膜层后,能够通过去除剩余图形传递材料层的方式,在第二方向上使第二沟槽之间相隔离、在第一方向上使第二沟槽和第一沟槽之间相隔离;与通过直接刻蚀图形传递材料层以形成第一沟槽和第二沟槽的方案相比,离子注入的工艺灵活性、位置精度和尺寸精度均较高,且易于使第一掺杂掩膜层或第二掺杂掩膜层获得较小的尺寸,有利于精确控制所述第一掺杂掩膜层和第二掺杂掩膜层的尺寸和位置,从而能够精确控制所述第一沟槽和第二沟槽的尺寸和位置,且所形成的第一沟槽和第二沟槽即为满足图形设计需求的图形,进而提高了目标图形的图形精度,相应提高了图形传递的精度。

14.为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

15.图1至图15是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

16.参考图1,提供基底10,所述基底10上形成有图形传递材料层130。

17.所述基底10用于为后续制程提供工艺平台。

18.本实施例中,基底10包括基底结构层100,基底结构层100包括衬底。以所形成的半导体结构为平面晶体管为例,所述衬底为平面衬底。

19.具体地,所述衬底为硅衬底。在另一些实施例中,衬底的材料还可以为锗、锗化硅、碳化硅、砷化镓或镓化铟等其他材料,衬底还可以为绝缘体上的硅衬底或者绝缘体上的锗衬底等其他类型的衬底。在其他实施例中,当所形成的半导体结构为鳍式场效应晶体管时,衬底还可以为具有鳍部的衬底。

20.所述基底结构层100还可以包括其他结构,例如,栅极结构、掺杂区、浅沟槽隔离结构(shallow trench isolation,sti)和介电层等。其中,所述栅极结构可以为金属栅结构或多晶硅栅结构。具体地,所述基底结构层100还包括形成于所述衬底上的层间介质层(图未示)以及形成于所述层间介质层中的接触孔插塞(contact,ct)(图未示)。

21.本实施例中,基底10还包括位于基底结构层100上的硬掩膜材料层120。后续在图形传递材料层130中形成图形,并将该图形传递至硬掩膜材料层120中,再经由图形化后的硬掩膜材料层120向下传递,通过所述硬掩膜材料层120,有利于提高图形传递的精度。

22.本实施例中,所述硬掩膜(hard mask,hm)材料层120的材料可以包括氧化硅、氮化硅、氮氧化硅、碳化硅、钛、氧化钛、氮化钛、钽、氧化钽、氮化钽、氮化硼、氮化铜、氮化铝和氮化钨中的一种或多种。作为一种示例,所述硬掩膜材料层120为金属硬掩膜(metal hard mask,mhm)材料层,所述硬掩膜材料层120的材料为氮化钛。

23.本实施例中,所述基底结构层100上还形成有保护层140,所述保护层140位于所述硬掩膜材料层120和图形传递材料层130之间。所述保护层140用于对所述硬掩膜材料层120起到保护作用,在图形化所述图形传递材料层130时,降低所述硬掩膜材料层120受损的概率,从而有利于提高后续形成于硬掩膜材料层120中的图形的精度。

24.本实施例中,所述基底100还包括:介电层110,位于所述基底结构层100和硬掩膜材料层120之间。本实施例中,所述介电层110为金属层间介质(inter metal dielectric,imd)层,所述介电层110用于实现后段(back end of line,beol)制程中金属互连结构之间的电隔离。

25.作为一种示例,所述介电层110为第一金属层间介质,用于实现第一金属互连线(即m1 layer)之间的电隔离。其中,所述第一金属互连线指的是最靠近接触孔插塞的金属互连结构。在另一些实施例中,所述介电层还可以为位于第一金属互连线上的其他金属层间介质,用于实现其他互连结构之间的电隔离。例如,所述介电层为第二金属层间介质,用于实现第二金属互连线、以及位于第二金属互连线和第一金属互连线之间的通孔(via)互连结构之间的电隔离。

26.为此,所述介电层110的材料为低k介质材料(低k介质材料指相对介电常数大于或等于2.6且小于等于3.9的介质材料)、超低k介质材料(超低k介质材料指相对介电常数小于

2.6的介质材料)、氧化硅、氮化硅或氮氧化硅等。本实施例中,所述介电层110的材料为超低k介质材料,从而降低后段金属互连结构之间的寄生电容,进而减小后段rc延迟。具体地,所述超低k介质材料可以为sioch。

27.后续对所述图形传递材料层130进行图形化,从而利用所述图形传递材料层130,将图形传递至所述基底10中。因此,所述硬掩膜材料层120与图形传递材料层130之间具有较高的刻蚀选择比。具体地,所述硬掩膜材料层120与图形传递材料层130的材料不同。

28.本实施例中,所述图形传递材料层130为无定形硅(a-si)。无定形硅的工艺兼容性较高,通过选用无定形硅,便于通过离子掺杂的方式改变所述图形传递材料层130中部分区域的耐刻蚀度。在其他实施例中,所述图形传递材料层的材料还可以为多晶硅。

29.需要说明的是,在其他实施例中,基底也可以包括衬底以及位于衬底上的硬掩膜材料层。后续在图形传递材料层中形成图形,并将该图形传递至硬掩膜材料层中,再经由图形化后的硬掩膜材料层向下传递,从而在衬底中形成沟槽。

30.结合参考图2至图3,图2是俯视图,图3是图2沿a1a2割线的剖视图,进行第一离子注入,向部分区域的图形传递材料层130中掺杂第一离子,形成多个分立的第一掺杂掩膜层150,所述第一掺杂掩膜层150的排布方向为第一方向(如图2中y方向所示),与所述第一方向相垂直的方向为第二方向(如图2中x方向所示),所述第一离子注入适于增大所述图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比。

31.后续在第二方向上,在所述第一掺杂掩膜层150两侧的图形传递材料层130中形成第一沟槽,所述第一掺杂掩膜层150用于在第二方向上使第一沟槽之间相隔离。离子注入的工艺灵活性、位置精度和尺寸精度均较高,且易于使第一掺杂掩膜层150获得较小的尺寸,从而能够在所述第二方向上,使第一沟槽在头对头(head to head)的位置处实现更小的间距,且相邻第一沟槽的头部不容易连接,相邻第一沟槽在头对头的位置处的形貌质量也更好。其中,所述第一沟槽用于定义后续部分目标图形的形状、尺寸和位置,从而有利于提高后续图形转移的精度。

32.所述第一离子注入适于增大所述图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比。其中,所述图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比指的是:刻蚀所述图形传递材料层130时,所述图形传递材料层130和第一掺杂掩膜层150的被刻蚀速率的比值。也就是说,后续刻蚀所述图形传递材料层130时,经所述第一离子注入的图形传递材料层130(即第一掺杂掩膜层150)的被刻蚀速率更低。

33.本实施例中,通过所述第一离子注入,向部分区域的图形传递材料层130内掺杂第一离子,使第一掺杂掩膜层150的材料中的微观结构产生差别。具体地,所述第一离子使得所述第一掺杂掩膜层150材料中硅的晶界间隙减小,从而提高所述第一掺杂掩膜层150的热稳定性和化学稳定性,稳定性的提高相应有利于提高所述第一掺杂掩膜层150的抗腐蚀能力,进而增大所述图形传递材料层130和第一掺杂掩膜层150之间的刻蚀选择比,使得后续刻蚀所述图形传递材料层130的工艺对第一掺杂掩膜层150的影响小。

34.本实施例中,在所述第一离子注入后,使得所述图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比大于30。因此,第一离子注入的掺杂离子包括b离子、c离子、p离子和as离子中的一种或多种。

35.本实施例中,第一离子注入的掺杂离子为b离子,通过向部分区域的无定形硅中掺

杂b离子,使第一掺杂掩膜层150的材料变为硼掺杂的硅,从而显著提高第一掺杂掩膜层150的耐刻蚀度,进而提图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比。而且,b原子的稳定性较高,有利于提高第一掺杂掩膜层150的热稳定性和化学稳定性,此外,b离子是半导体领域中常用的掺杂离子,工艺兼容性较高。

36.本实施例中,所述第一离子注入的工艺为离子注入工艺。通过调整离子注入工艺的注入剂量,易于对所述图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比进行调整。

37.所述第一离子注入的注入剂量不宜过低,也不宜过高。注入剂量越低,所述第一掺杂掩膜层150中的第一离子的掺杂浓度相应越低,所述图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比难以满足工艺需求;如果注入剂量过高,所述第一掺杂掩膜层150中的第一离子的掺杂浓度相应过高,所述第一掺杂掩膜层150中的第一离子容易扩散至剩余的图形传递材料层130中,从而影响后续第一沟槽的形貌、位置和尺寸。为此,本实施例中,所述第一离子注入的注入剂量为1e14原子每平方厘米至1e16原子每平方厘米。

38.所述第一离子注入的注入能量不宜过小,也不宜过大。如果注入能量过小,则难以保证整个厚度范围内的图形传递材料层130中均掺杂有该掺杂离子,从而导致后续去除剩余的图形传递材料层130时,第一掺杂掩膜层150下方剩余的图形传递材料层130也被去除,进而导致第一掺杂掩膜层150发生坍塌;如果注入能量过大,第一离子容易被注入至图形传递材料层130下方的其他膜层中,从而影响后续制程的正常进行。为此,本实施例中,所述第一离子注入的注入能量为1.5kev至13kev。例如,所述第一离子注入的注入能量为2kev、5kev、7kev、9kev或11kev。

39.第一离子注入的注入方向与基底100表面法线的夹角不宜过大。如果夹角过大,第一离子容易被误掺杂至其他区域位置处的图形传递材料层130中,从而影响后续第一沟槽和第二沟槽的形貌、位置和尺寸,而且还会受到遮蔽效应(shadow effect)的影响,从而影响第一掺杂掩膜层150的形貌、位置和尺寸。为此,本实施例中,第一离子注入的注入方向与基底100表面法线的夹角为0度至2度。具体地,所述夹角可以为0度,即注入方向垂直于基底100表面。

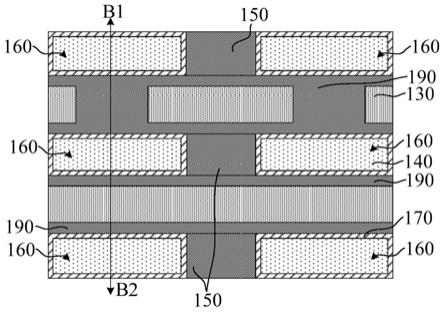

40.结合参考图4和图5,图4是俯视图,图5是图4沿b1b2割线的剖视图,在所述第二方向(如图2中x方向所示)上,在第一掺杂掩膜层150两侧的图形传递材料层130中形成第一沟槽160,所述第一沟槽160暴露出第一掺杂掩膜层150在所述第二方向的侧壁。

41.所述第一沟槽160用于定义形成于基底10中的部分目标图形的形状、尺寸和位置。所述第一沟槽160还用于为后续掩膜侧墙的形成提供空间位置。作为一种示例,在所述第一方向(如图2中y方向所示)上,所述第一沟槽160的侧壁和第一掺杂掩膜层150的侧壁相齐平。

42.本实施例中,采用干法刻蚀工艺刻蚀所述第一掺杂掩膜层150两侧的所述图形传递材料层130,形成第一沟槽160,例如采用各向异性干法刻蚀工艺。各向异性干法刻蚀工艺具有各向异性的刻蚀特性,有利于提高第一沟槽160的形貌质量,使得第一沟槽160的形貌、尺寸和位置能够满足工艺需求。而且,通过选用干法刻蚀工艺,易于控制刻蚀停止位置,以降低对位于所述图形传递材料层130下方的膜层的损伤。

43.本实施例中,所述第一沟槽160底部露出所述保护层140。

44.继续参考图4和图5,在所述第一沟槽160的侧壁形成掩膜侧墙170。

45.后续对所述第一掺杂掩膜层150和第一沟槽160露出的部分区域的图形传递材料层170进行第二离子注入,形成第二掺杂掩膜层,随后去除剩余的图形传递材料层170,形成第二沟槽。所述掩膜侧墙170用于实现第二沟槽与第一沟槽160的隔离,防止第二沟槽与第一沟槽160出现贯通的问题,且使得相邻第二沟槽与第一沟槽160的间距满足设计最小间隔(designed minimum space)。而且,后续将第二沟槽与第一沟槽160的图形传递至基底10中时,所述掩膜侧墙170还用于作为刻蚀所述基底10的掩膜。此外,掩膜侧墙170用于调节第二沟槽与第一沟槽160在第一方向上的间距。

46.为此,掩膜侧墙170与保护层140、硬掩膜材料层120、图形传递材料层130以及第一掺杂掩膜层150的材料均不同。掩膜侧墙170的材料可以为氧化钛、氮化钛、氧化硅、氮化硅、氮氧化硅或碳化硅。本实施例中,掩膜侧墙170的材料为氮化硅。

47.具体地,形成掩膜侧墙170的步骤包括:形成侧墙膜(图未示),所述侧墙膜保形覆盖所述第一沟槽160的底部和侧壁、以及所述图形传递材料层130和第一掺杂掩膜层150的顶部;去除位于所述第一沟槽160的底部、以及所述图形传递材料层130和第一掺杂掩膜层150的顶部的侧墙膜,保留位于所述第一沟槽160侧壁的剩余侧墙膜作为掩膜侧墙170。

48.本实施例中,采用原子层沉积工艺形成侧墙膜。采用原子层沉积工艺形成的侧墙膜的厚度均匀性好,且侧墙膜具有良好的台阶覆盖能力,使得侧墙膜能够很好的覆盖第一沟槽160的底部拐角处。

49.本实施例中,采用无掩膜刻蚀工艺去除位于所述第一沟槽160的底部、以及所述图形传递材料层130和第一掺杂掩膜层150的顶部的侧墙膜。具体地,无掩膜刻蚀工艺为各向异性干法刻蚀,从而能够沿垂直于基底10表面的方向,去除位于所述第一沟槽160的底部、以及所述图形传递材料层130和第一掺杂掩膜层150的顶部的侧墙膜,并使得第一沟槽160侧壁上的侧墙膜被保留。

50.由于掩膜侧墙170采用无掩膜刻蚀工艺形成,使得掩膜侧墙170的宽度范围不受光刻工艺的影响,掩膜侧墙170的宽度能够做的很小,从而使相邻第二沟槽与第一沟槽160的间距能够满足设计最小间隔,且掩膜侧墙170仍具有良好的位置精确度和形貌精确度,以避免现有的光刻工艺带来的对准误差问题。

51.其中,根据相邻第二沟槽与第一沟槽160的间距目标值,合理设定掩膜侧墙170的宽度。在一些实施例中,掩膜侧墙170的宽度为至例如为

52.结合参考图6至图9,形成所述掩膜侧墙170后,进行第二离子注入,向所述第一掺杂掩膜层150和第一沟槽160露出的部分区域的图形传递材料层130中掺杂第二离子,掺杂有所述第二离子的所述图形传递材料层130作为第二掺杂掩膜层190,所述第二离子注入适于增大图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比。

53.所述第二掺杂掩膜层190用于定义第二沟槽的位置、形貌和尺寸。图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比较高,且图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比也较高,因此,后续能够通过去除剩余图形传递材料层130的方式,即可形成多个分立的第二沟槽,且在第二方向上使第二沟槽之间相隔离、在第一方向上使

第二沟槽和第一沟槽160之间相隔离。

54.离子注入的工艺灵活性、位置精度和尺寸精度均较高,且易于使第二掺杂掩膜层190获得较小的尺寸,有利于精确控制所述第二掺杂掩膜层190的尺寸和位置,从而能够在所述第二方向上,使第二沟槽在头对头的位置处实现更小的间距,且相邻第二沟槽的头部不容易连接,相邻第二沟槽在头对头的位置处的形貌质量也更好,进而能够精确控制所述第二沟槽的形貌、尺寸和位置。

55.具体地,形成所述第二掺杂掩膜层190的步骤包括:

56.结合参考图6和图7,图6是俯视图,图7是图6沿b1b2割线的剖视图,在所述图形传递材料层130和第一掺杂掩膜层150上形成掺杂掩膜层180,所述掺杂掩膜层180露出部分区域的图形传递材料层130。

57.所述掺杂掩膜层180用于作为后续第一离子注入的掩膜,从而定义第二掺杂掩膜层的形成区域。

58.本实施例中,所述掺杂掩膜层180的材料为光刻胶。形成所述掺杂掩膜层180的工艺包括依次进行的涂布工艺、曝光工艺和显影工艺。

59.本实施例中,位于第一沟槽160(如图5所示)中的掺杂掩膜层180可以覆盖掩膜侧墙170的顶部,也可以露出掩膜侧墙170,从而增大了对准工艺的工艺窗口。作为一种示例,掺杂掩膜层180还覆盖掩膜侧墙170的顶部。

60.结合参考图8和图9,图8是俯视图,图9是图8沿b1b2割线的剖视图,对所述掺杂掩膜层180(如图7所示)露出的图形传递材料层130进行第二离子注入,形成第二掺杂掩膜层190。

61.所述第二离子注入适于增大所述图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比。其中,所述图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比指的是:刻蚀所述图形传递材料层130时,所述图形传递材料层130和第二掺杂掩膜层190的被刻蚀速率的比值。也就是说,后续刻蚀所述图形传递材料层130时,经所述第二离子注入的图形传递材料层130(即第二掺杂掩膜层190)的被刻蚀速率更低。

62.所述第二离子注入的掺杂离子包括b离子、c离子、p离子和as离子中的一种或多种。本实施例中,第二离子注入的掺杂离子为b离子。本实施例中,所述第二离子注入的工艺为离子注入工艺。通过调整离子注入工艺的注入剂量,易于对图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比进行调整。

63.所述第二离子注入的注入剂量不宜过低,也不宜过高。注入剂量越低,所述第二掺杂掩膜层190中的第二离子的掺杂浓度相应越低,所述图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比难以满足工艺需求;如果注入剂量过高,所述第二掺杂掩膜层190中的第二离子的掺杂浓度相应过高,所述第二掺杂掩膜层190中的第二离子容易扩散至剩余的图形传递材料层130中,从而影响后续第二沟槽的形貌、位置和尺寸。为此,本实施例中,所述第二离子注入的注入剂量为1e14原子每平方厘米至1e16原子每平方厘米。

64.所述第二离子注入的注入能量不宜过小,也不宜过大。如果注入能量过小,则难以保证整个厚度范围内的图形传递材料层130中均掺杂有该掺杂离子,从而导致后续去除剩余的图形传递材料层130时,第二掺杂掩膜层190下方剩余的图形传递材料层130也被去除,进而导致第二掺杂掩膜层190发生坍塌;如果注入能量过大,所述第二离子容易被注入至图

形传递材料层130下方的其他膜层中,从而影响后续制程的正常进行。为此,本实施例中,所述第二离子注入的注入能量为1.5kev至13kev。例如,所述第二离子注入的注入能量为2kev、5kev、7kev、9kev或11kev。

65.第二离子注入的注入方向与基底100表面法线的夹角不宜过大。如果夹角过大,则该掺杂离子容易被误掺杂至其他区域位置处的图形传递材料层130中,而且,还会受到遮蔽效应的影响,从而影响后续第二沟槽的形貌、位置和尺寸。为此,本实施例中,第二离子注入的注入方向与基底100表面法线的夹角为0度至2度。具体地,所述夹角可以为0度,即注入方向垂直于基底100表面。

66.对所述第二掺杂掩膜层190和第二离子注入的具体描述,可分别参考前述对第一掺杂掩膜层150和第一离子注入的相应描述,在此不再赘述。

67.本实施例中,所述第二离子注入和第一离子注入的工艺参数相同。即所述第二离子注入和第一离子注入的注入离子相同,所述第二离子注入和第一离子注入的注入剂量相同,所述第二离子注入和第一离子注入的注入能量相同,从而使第一掺杂掩膜层150和第二掺杂掩膜层190中离子的掺杂浓度、以及离子分布相同,这使得所述第一掺杂掩膜层150和第二掺杂掩膜层190的耐刻蚀度相同,相应的,后续刻蚀去除剩余的图形传递材料层130,以形成第二沟槽时,便于刻蚀工艺的工艺参数的设置。而且,后续还需去除所述第一掺杂掩膜层150和第二掺杂掩膜层190,因此,通过使所述第一掺杂掩膜层150和第二掺杂掩膜层190中离子的掺杂浓度相同,以便于后续在同一步骤中去除所述第一掺杂掩膜层150和第二掺杂掩膜层190,以简化工艺步骤。

68.本实施例中,根据集成电路的设计要求,即根据后续第二沟槽和第一沟槽160在第一方向上的间距设置,形成第二掺杂掩膜层190后,在所述第二方向上,剩余的图形传递材料层130和掩膜侧墙170通过第二掺杂掩膜层190相隔离,或者,在所述第二方向上,剩余的图形传递材料层130和掩膜侧墙170相接触,从而满足集成电路的设计复杂度要求。而且,通过调节所述第一沟槽160与剩余的图形传递材料层130在第一方向上的间距,从而调节后续第二沟槽和第一沟槽160在第一方向上的间距。其中,当剩余的图形传递材料层130和掩膜侧墙170通过第二掺杂掩膜层190相隔离时,第二沟槽和第一沟槽160在第一方向上的间距较大,当剩余的图形传递材料层130和掩膜侧墙170相接触时,第二沟槽和第一沟槽160在第一方向上的间距较小。作为一种示例,形成第二掺杂掩膜层190后,在所述第二方向上,剩余的图形传递材料层130和掩膜侧墙170通过第二掺杂掩膜层190相隔离。

69.本实施例中,形成第二掺杂掩膜层190后,所述形成方法还包括:去除掺杂掩膜层180(如图7所示)。具体地,采用灰化工艺,去除掺杂掩膜层180。

70.结合参考图10和图11,图10是俯视图,图11是图10沿b1b2割线的剖视图,形成所述第二掺杂掩膜层190后,去除剩余的图形传递材料层130(如图6所示),形成第二沟槽161。

71.第二沟槽161用于定义形成于基底10中的剩余目标图形的形状、尺寸和位置。后续沿所述第一沟槽160和第二沟槽161刻蚀基底10,形成目标图形,所述第一掺杂掩膜层150和第二掺杂掩膜层190的尺寸精度和位置精度较高,从而能够精确控制所述第一沟槽160和第二沟槽161的尺寸和位置,而且,第一沟槽160和第二沟槽161即为满足图形设计需求的图形,无需再在第一沟槽160或第二沟槽161中形成用于作为剪切部件(cut feature)的刻蚀阻挡层,进而有利于提高后续目标图形的图形精度,相应提高了图形传递的精度。

72.此外,本实施例分别形成第一沟槽160和第二沟槽161,有利于提高形成第一沟槽160和第二沟槽161的工艺窗口(例如:改善光学邻近效应或缓解光刻工艺解析度的限制),使所述第一沟槽160和第二沟槽161的图形精度得到保障,从而提高图形传递的精度。作为一种示例,在所述第一方向上,所述第一沟槽160和第二沟槽161之间被所述掩膜侧墙170和第二掺杂掩膜层190隔离。在其他实施例中,所述第一沟槽和第二沟槽之间仅被所述掩膜侧墙隔离。

73.本实施例中,所述第一沟槽160底部露出所述保护层140。

74.本实施例中,采用无掩膜刻蚀工艺,去除剩余图形传递材料层130。图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比较高,图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比也较高,因此,在去除剩余的图形传递材料层130的过程中,所述第一掺杂掩膜层150和第二掺杂掩膜层190的被刻蚀速率较低,相应能够采用无掩膜刻蚀工艺去除剩余的图形传递材料层130,从而简化工艺步骤、降低成本,而且,通过选用无掩膜刻蚀工艺,还显著增大了形成第二沟槽161的工艺窗口,避免对准偏差(overlay shift)的问题。

75.具体地,采用湿法刻蚀工艺去除剩余图形传递材料层130,以形成第二沟槽161。湿法刻蚀工艺易于实现较高的刻蚀选择比,且湿法刻蚀工艺是通过化学反应的方式去除剩余图形传递材料层130,有利于减小第一沟槽160露出的保护层140受到的损伤,而且,有利于将剩余的图形传递材料层130去除干净。

76.本实施例中,所述图形传递材料层130的材料为无定形硅,湿法刻蚀工艺所采用的刻蚀溶液为cl2和hbr的混合溶液或tmah溶液

77.结合参考图12和图13,图12是俯视图,图13是图12沿b1b2割线的剖视图,以所述第一掺杂掩膜层150(如图10所示)、第二掺杂掩膜层190(如图10所示)和掩膜侧墙170(如图10所示)为掩膜,沿所述第一沟槽160(如图10所示)和第二沟槽161(如图10所示)刻蚀所述基底10,形成目标图形125。

78.所述第一沟槽160和第二沟槽161的形貌质量、尺寸精度和位置精度较高,且第一沟槽160和第二沟槽161即为满足图形设计需求的图形,因此,从而提高了所述目标图形125的图形精度,相应提高了图形传递的精度。

79.本实施例中,沿第一沟槽160和第二沟槽161刻蚀硬掩膜材料层120,在硬掩膜材料层120中形成掩膜开口,掩膜开口用于作为目标图形125,且剩余的硬掩膜材料层120作为硬掩膜层200。所述硬掩膜层200用于作为后续图形化所述介电层110的掩膜。所述第一沟槽160和第二沟槽161的图形传递至硬掩膜层200中,所述掩膜开口的图形精度相应较高。

80.本实施例中,所述第一沟槽160的侧壁上形成有掩膜侧墙170,因此,形成所述目标图形125的步骤中,还以所述掩膜侧墙170作为刻蚀掩膜。

81.本实施例中,硬掩膜材料层120上形成有保护层140(如图11所示),因此,刻蚀硬掩膜材料层120之前,还包括:刻蚀保护层140,以露出硬掩膜材料层120。

82.本实施例中,形成目标图形125后,形成方法还包括:去除第一掺杂掩膜层150、第二掺杂掩膜层190、掩膜侧墙170和保护层140。具体地,采用干法刻蚀工艺,去除第一掺杂掩膜层150、第二掺杂掩膜层190、掩膜侧墙170和保护层140。其中,通过调整干法刻蚀工艺的参数(例如,刻蚀气体),从而能够在同一刻蚀机台中去除第一掺杂掩膜层150、第二掺杂掩膜层190、掩膜侧墙170和保护层140。

83.结合参考图14和图15,图14是俯视图,图15是图14沿b1b2割线的剖视图,形成目标图形125后,形成方法还包括:以硬掩膜层200为掩膜,沿掩膜开口(即目标图形125)刻蚀介电层110,在介电层110中形成互连开口115。

84.互连开口115用于为金属互连结构的形成提供空间位置。掩膜开口的图形精度较高,从而提高了互连开口115的图形精度,使得所述互连结构的形貌和布局满足设计需求,相应提高了所述互连结构的性能。

85.需要说明的是,随着电路集成度的增加,后段金属布线的设计复杂度越来越高,相邻金属互连线的间距也越来越小,通过前述形成所述第一沟槽160(如图10所示)和第二沟槽161(如图10所示)的方式,显著提高了所述金属互连线的位置精度、形貌质量和尺寸精度,从而提高半导体结构的性能和可靠性。

86.相应的,本发明还提供一种半导体结构。继续参考图10和图11,图10是俯视图,图11是图10沿b1b2割线的剖视图。

87.所述半导体结构包括:基底10;图形传递材料130,位于基底10上;第一离子,位于部分区域的图形传递材料层130中,掺杂有第一离子的图形传递材料层130作为第一掺杂掩膜层150,第一掺杂掩膜层150的排布方向为第一方向(如图2中y方向所示),与第一方向相垂直的方向为第二方向(如图2中x方向所示),第一离子适于增大图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比;第一沟槽160,位于第一掺杂掩膜层150在第二方向的两侧的图形传递材料层130中,第一沟槽160暴露出第一掺杂掩膜层150在第二方向的侧壁;掩膜侧墙170,位于第一沟槽160的侧壁;第二离子,位于第一掺杂掩膜层150和第一沟槽160露出的部分区域的图形传递材料层130中,掺杂有第二离子的图形传递材料层130作为第二掺杂掩膜层190,第二离子适于增大图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比;其中,未掺杂有第一离子和第二离子的剩余图形传递材料层130用于占据第二沟槽的位置。

88.后续去除未掺杂有所述第一离子和第二离子的剩余图形传递材料层130,以形成第二沟槽,并将第一沟槽160和第二沟槽的图形传递至基底10中,从而在基底10中形成目标图形。本实施例利用第一掺杂掩膜层150,在第二方向上使第一沟槽160之间相隔离,且图形传递材料层130与第一掺杂掩膜层150、第二掺杂掩膜层160之间的刻蚀选择比均较高,因此,后续能够通过去除未掺杂有所述第一离子和第二离子的剩余图形传递材料层130的方式,在第二方向上使第二沟槽之间相隔离、在第一方向上使第二沟槽和第一沟槽160之间相隔离;与通过直接刻蚀图形传递材料层以形成第一沟槽和第二沟槽的方案相比,所述第一掺杂掩膜层150和第二掺杂掩膜层190通过离子注入工艺形成,离子注入的工艺灵活性、位置精度和尺寸精度均较高,且易于使第一掺杂掩膜层150或第二掺杂掩膜层190获得较小的尺寸,有利于精确控制所述第一掺杂掩膜层150和第二掺杂掩膜层190的尺寸和位置,从而能够精确控制所述第一沟槽160和第二沟槽的尺寸和位置,且第一沟槽160和第二沟槽即为满足图形设计需求的图形,进而提高了目标图形的图形精度,相应提高了图形传递的精度。

89.本实施例中,基底10包括基底结构层100,基底结构层100包括衬底。以所述半导体结构为平面晶体管为例,衬底为平面衬底。作为一种示例,衬底为硅衬底。在其他实施例中,当半导体结构为鳍式场效应晶体管时,衬底还可以为具有鳍部的衬底。

90.基底结构层100还可以包括其他结构,例如,栅极结构、掺杂区、浅沟槽隔离结构)

和介电层等。其中,栅极结构可以为金属栅结构或多晶硅栅结构。具体地,基底结构层100还包括位于衬底上的层间介质层(图未示)以及位于介质层中的接触孔插塞(contact,ct)(图未示)。

91.本实施例中,基底10还包括位于基底结构层100上的硬掩膜材料层120。通过硬掩膜材料层120,有利于提高图形传递的精度。本实施例中,硬掩膜材料层120为硬掩膜材料层。为此,硬掩膜材料层120的材料可以包括氧化硅、氮化硅、氮氧化硅、碳化硅、钛、氧化钛、氮化钛、钽、氧化钽、氮化钽、氮化硼、氮化铜、氮化铝和氮化钨中的一种或多种。作为一种示例,硬掩膜材料层120为金属硬掩膜材料层,其材料为氮化钛。

92.本实施例中,基底结构层100上还形成有保护层140,保护层140位于硬掩膜材料层120和图形传递材料层130之间。保护层140用于对硬掩膜材料层120起到保护作用,在图形化图形传递材料层130时,降低硬掩膜材料层120受损的概率,从而有利于提高后续形成于硬掩膜材料层120中的图形的精度。

93.本实施例中,基底100还包括:介电层110,位于基底结构层100和硬掩膜材料层120之间。

94.本实施例中,介电层110为金属层间介质层,用于实现后段制程中金属互连结构之间的电隔离。作为一种示例,介电层110为第一金属层间介质,用于实现第一金属互连线之间的电隔离。其中,第一金属互连线指的是最靠近接触孔插塞的金属互连结构。在另一些实施例中,介电层还可以为位于第一金属互连线上的其他金属层间介质,用于实现其他互连结构之间的电隔离。例如,所述介电层为第二金属层间介质,用于实现第二金属互连线、以及位于第二金属互连线和第一金属互连线之间的通孔互连结构之间的电隔离。

95.本实施例中,介电层110的材料为超低k介质材料。具体地,超低k介质材料可以为sioch。

96.硬掩膜材料层120与图形传递材料层130之间具有较高的刻蚀选择比。具体地,硬掩膜材料层120与图形传递材料层130的材料不同。本实施例中,图形传递材料层130为无定形硅。在其他实施例中,图形传递材料层的材料还可以为多晶硅。

97.本实施例中,后续沿第一沟槽160和第二沟槽刻蚀硬掩膜材料层120,在硬掩膜材料层120中形成掩膜开口,所述掩膜开口用于作为目标图形,且剩余的硬掩膜材料层120作为硬掩膜层。第一沟槽160和第二沟槽161的图形传递至硬掩膜层200中,所述掩膜开口的图形精度相应较高。

98.硬掩膜层用于作为后续图形化介电层110的掩膜。后续以所述硬掩膜层为掩膜,沿掩膜开口(即目标图形)刻蚀所述介电层110,在所述介电层110中形成互连开口。掩膜开口的图形精度较高,从而提高了互连开口的图形精度,使得互连结构的形貌和布局满足设计需求,相应提高了互连结构的性能。

99.在其他实施例中,基底也可以包括衬底以及位于衬底上的硬掩膜材料层。后续经由图形化后的硬掩膜材料层向下传递,从而在衬底中形成沟槽。

100.第一掺杂掩膜层150用于在第二方向上使第一沟槽160之间相隔离。离子注入的工艺灵活性、位置精度和尺寸精度均较高,且易于使第一掺杂掩膜层150获得较小的尺寸,从而能够在第二方向上,使第一沟槽160在头对头的位置处实现更小的间距,且相邻第一沟槽160的头部不容易连接,相邻第一沟槽160在头对头的位置处的形貌质量也更好。

101.第一离子使第一掺杂掩膜层150的材料中的微观结构产生差别。具体地,第一离子使得第一掺杂掩膜层150材料中硅的晶界间隙减小,从而提高第一掺杂掩膜层150的热稳定性和化学稳定性,稳定性的提高相应有利于提高第一掺杂掩膜层150的抗腐蚀能力,进而增大图形传递材料层130和第一掺杂掩膜层150之间的刻蚀选择比,使得刻蚀图形传递材料层130的工艺对第一掺杂掩膜层150的影响小。

102.本实施例中,第一离子使得图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比大于30。因此,第一离子包括b离子、c离子、p离子和as离子中的一种或多种。

103.本实施例中,第一离子为b离子。通过向部分区域的无定形硅中掺杂b离子,使第一掺杂掩膜层150的材料变为硼掺杂的硅,从而显著提高第一掺杂掩膜层150的耐刻蚀度,进而提图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比。而且,b原子的稳定性较高,有利于提高第一掺杂掩膜层150的热稳定性和化学稳定性,此外,b离子是半导体领域中常用的掺杂离子,工艺兼容性较高。

104.第一沟槽160用于定义形成于基底10中的部分目标图形的形状、尺寸和位置。作为一种示例,在第一方向上,第一沟槽160的侧壁和第一掺杂掩膜层150的侧壁相齐平。本实施例中,第一沟槽160底部露出保护层140。

105.掩膜侧墙170用于实现第二沟槽与第一沟槽160的隔离,防止第二沟槽与第一沟槽160出现贯通的问题,且使得相邻第二沟槽与第一沟槽160的间距满足设计最小间隔。而且,后续将第二沟槽与第一沟槽160的图形传递至基底10中时,掩膜侧墙170还用于作为刻蚀基底10的掩膜。此外,掩膜侧墙170用于调节第二沟槽与第一沟槽160在第一方向上的间距。

106.为此,掩膜侧墙170与保护层140、硬掩膜材料层120、图形传递材料层130以及第一掺杂掩膜层150的材料均不同。掩膜侧墙170的材料可以为氧化钛、氮化钛、氧化硅、氮化硅、氮氧化硅或碳化硅。本实施例中,掩膜侧墙170的材料为氮化硅。

107.其中,根据相邻第二沟槽与第一沟槽160的间距目标值,合理设定掩膜侧墙170的宽度。在一些实施例中,掩膜侧墙170的宽度为至例如为

108.第二掺杂掩膜层190用于定义第二沟槽的位置、形貌和尺寸。其中,所述第二沟槽用于定义形成于基底10中的剩余目标图形的形状、尺寸和位置。

109.图形传递材料层130与第二掺杂掩膜层190之间的刻蚀选择比较高,且图形传递材料层130与第一掺杂掩膜层150之间的刻蚀选择比也较高,因此,后续能够通过去除未掺杂有第一离子和第二离子的剩余图形传递材料层130的方式,即可形成多个分立的第二沟槽,且在第二方向上使第二沟槽之间相隔离、在第一方向上使第二沟槽和第一沟槽160之间相隔离。

110.离子注入的工艺灵活性、位置精度和尺寸精度均较高,且易于使第二掺杂掩膜层190获得较小的尺寸,有利于精确控制第二掺杂掩膜层190的尺寸和位置,从而能够在第二方向上,使第二沟槽在头对头的位置处实现更小的间距,且相邻第二沟槽的头部不容易连接,相邻第二沟槽在头对头的位置处的形貌质量也更好,进而能够精确控制所述第二沟槽的形貌、尺寸和位置。

111.第二离子包括b离子、c离子、p离子和as离子中的一种或多种。本实施例中,第二离

子为b离子。对第二离子的描述,可结合参考前述对第一离子的相应描述,在此不再赘述。

112.本实施例中,第一掺杂掩膜层150和第二掺杂掩膜层190中离子的掺杂浓度相同,这使得第一掺杂掩膜层150和第二掺杂掩膜层190的耐刻蚀度相同,相应的,后续刻蚀去除剩余的图形传递材料层130以形成第二沟槽时,便于刻蚀工艺的工艺参数的设置。而且,后续还需去除第一掺杂掩膜层150和第二掺杂掩膜层190,因此,通过使第一掺杂掩膜层150和第二掺杂掩膜层190中离子的掺杂浓度相同,以便于后续在同一步骤中去除第一掺杂掩膜层150和第二掺杂掩膜层190,以简化工艺步骤。

113.本实施例中,根据集成电路的设计要求,即根据第二沟槽和第一沟槽160在第一方向上的间距设置,在第二方向上,未掺杂有第一离子和第二离子的图形传递材料层130和掩膜侧墙170通过第二掺杂掩膜层190相隔离,或者,在第二方向上,未掺杂有第一离子和第二离子的图形传递材料层130和掩膜侧墙170相接触,从而满足集成电路的设计复杂度要求。

114.而且,通过调节第一沟槽160与未掺杂有第一离子和第二离子的图形传递材料层130在第一方向上的间距,从而调节第二沟槽和第一沟槽160在第一方向上的间距。

115.其中,当未掺杂有第一离子和第二离子的图形传递材料层130和掩膜侧墙170通过第二掺杂掩膜层190相隔离时,第二沟槽和第一沟槽160在第一方向上的间距较大,当未掺杂有第一离子和第二离子的图形传递材料层130和掩膜侧墙170相接触时,第二沟槽和第一沟槽160在第一方向上的间距较小。

116.作为一种示例,在所述第二方向上,未掺杂有第一离子和第二离子的图形传递材料层130和掩膜侧墙170通过第二掺杂掩膜层190相隔离。

117.本实施例中,后续沿第一沟槽160和第二沟槽刻蚀基底10,形成目标图形,第一掺杂掩膜层150和第二掺杂掩膜层190的尺寸精度和位置精度较高,从而能够精确控制所述第一沟槽160和第二沟槽的尺寸和位置,而且,第一沟槽160和第二沟槽即为满足图形设计需求的图形,无需再在第一沟槽160或第二沟槽中形成用于作为剪切部件的刻蚀阻挡层,进而有利于提高后续目标图形的图形精度,相应提高了图形传递的精度。

118.此外,本实施例中的第一沟槽160和第二沟槽在不同制程中形成,有利于提高形成第一沟槽160和第二沟槽的工艺窗口(例如:改善光学邻近效应或缓解光刻工艺解析度的限制),使所述第一沟槽160和第二沟槽的图形精度得到保障,从而提高图形传递的精度。

119.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1