半导体装置及半导体装置的制造方法与流程

半导体装置及半导体装置的制造方法

1.关联申请

2.本技术享有以日本专利申请2020-045738号(申请日:2020年3月16日)作为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

3.本发明的实施方式涉及半导体装置及半导体装置的制造方法。

背景技术:

4.以往,在半导体装置中,布线间隔的缩小化及布线层的多层化取得进展。另外,在半导体装置中,研究了降低布线容量的技术。

技术实现要素:

5.本发明所要解决的课题是提供布线容量低的半导体装置及半导体装置的制造方法。

6.实施方式的半导体装置具有多个布线和绝缘空间。绝缘空间配置于相邻的布线之间。绝缘空间由绝缘材料围成。绝缘空间充满大气压或压力低于大气压的空气。

附图说明

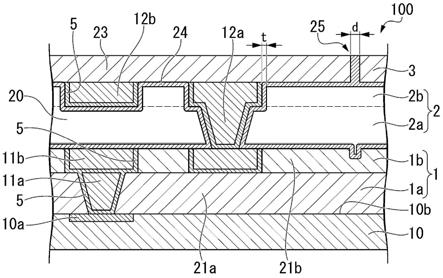

7.图1是用于说明第1实施方式的半导体装置的截面示意图。

8.图2是用于说明图1中所示的半导体装置的制造方法的一个例子的截面示意图。

9.图3是用于说明图1中所示的半导体装置的制造方法的一个例子的截面示意图。

10.图4是用于说明图1中所示的半导体装置的制造方法的一个例子的截面示意图。

11.图5是用于说明图1中所示的半导体装置的制造方法的一个例子的截面示意图。

12.图6是用于说明第2实施方式的半导体装置的截面示意图。

13.图7是用于说明图6中所示的半导体装置的制造方法的一个例子的截面示意图。

14.图8是用于说明图6中所示的半导体装置的制造方法的一个例子的截面示意图。

15.图9是用于说明图6中所示的半导体装置的制造方法的一个例子的截面示意图。

16.图10是用于说明图6中所示的半导体装置的制造方法的一个例子的截面示意图。

17.图11是用于说明实施方式的半导体装置的另一例子的截面示意图。

18.图12是用于说明实施方式的半导体装置的又一例子的截面示意图。

19.图13是用于说明实施方式的半导体装置的再一例子的截面示意图。

20.符号的说明

21.1、1c

…

第1层、1a

…

第1-1层、1b

…

第1-2层、2、2a、2b

…

第2层、2a

…

第2-1层、2b

…

第2-2层、3、3a、3b

…

第3层、3a

…

第3-1层、3b

…

第3-2层、3c

…

第3-3层、3d

…

第3-4层、3e

…

第3-5层、3f

…

第3-6层、5

…

阻挡层、10

…

基板、10a

…

接触垫、10b

…

绝缘区域、11a、11b

…

第1布线、12a、12b、12c、12e

…

第2布线、13a、13b、13c、13d、13e、13f

…

第3布线、20

…

绝缘空间、

20a、20b、20c、20d

…

含牺牲材料膜的层、21a、21b

…

第1绝缘膜、22

…

牺牲材料膜、22a

…

第1牺牲材料膜、22b

…

第2牺牲材料膜、23、23a、23b、23c、23d、23e、23f

…

第3绝缘膜、24

…

绝缘材料、25

…

柱状体、25a

…

贯通孔、26

…

衬里层、100、200、300、400、500

…

半导体装置。

具体实施方式

22.以下,参照附图对实施方式的半导体装置及半导体装置的制造方法进行说明。

23.(第1实施方式)

24.图1是用于说明第1实施方式的半导体装置的截面示意图。图1中所示的半导体装置100具有基板10、具有绝缘空间20的第2层2、配置于第2层2的基板10侧的第1层1、及配置于第2层2的与基板10相反侧的第3层3。半导体装置100具有包含第1层1、第2层2及第3层3的多层布线层。

25.基板10例如可以使用在硅晶片上设置有晶体管等元件的基板等。在图1中所示的半导体装置100中,在基板10表面具有绝缘区域10b和接触垫10a。绝缘区域10b例如由包含sio2等公知的绝缘材料的绝缘膜形成。接触垫10a通过埋入至贯通绝缘膜的接触孔中的贯通电极与晶体管的电极电连接。接触垫10a例如可以使用由cosi2、nisi2等公知的导电材料形成的垫。

26.第1层1设置于基板10上。第1层1如图1中所示的那样具有配置于基板10侧的第1-1层1a与配置于第2层2侧的第1-2层1b层叠而成的双层结构。

27.第1-1层1a具有多个第1布线11a(图1中仅记载1个)和由sio2、sin等绝缘材料形成的第1绝缘膜21a。第1布线11a由cu形成,基板10侧的面及侧面被由ti膜或tin膜形成的阻挡层5覆盖。第1布线11a为埋入至贯通第1绝缘膜21a的接触孔中的贯通布线。如图1中所示的那样,各第1布线11a与基板10的接触垫10a电连接。

28.第1-2层1b具有多个第1布线11b和由sio2形成的第1绝缘膜21b。第1布线11b由cu形成,基板10侧的面及侧面被由ti膜或tin膜形成的阻挡层5覆盖。第1布线11b将第1绝缘膜21b贯通,埋入至第1绝缘膜21b中。如图1中所示的那样,第1布线11b中的一部分设置于与第1-1层1a的第1布线11a在俯视图中重叠的位置,与第1布线11a的第2层2侧的面相接触。因此,第1布线11b中的一部分通过贯通第1-1层1a的第1布线11a与基板10的接触垫10a电连接。

29.第2层2设置于第1层1上。第2层2如图1中所示的那样,具有配置于第1层1侧的第2-1层2a与配置于第3层3侧的第2-2层2b层叠而成的双层结构。

30.第2-1层2a具有多个第2布线12a(图1中仅记载1个)。第2布线12a由cu形成,第1层1侧的面及侧面被由ti膜或tin膜形成的阻挡层5覆盖。第2布线12a为贯通第2-1层2a的贯通布线。如图1中所示的那样,各第2布线12a设置于与第1-2层1b的第1布线11b在俯视图中重叠的位置。各第2布线12a与第1布线11b的第2层2侧的面相接触,与第1布线11b电连接。

31.第2-2层2b具有多个第2布线12b。第2布线12b由cu形成,第1层1侧的面及侧面被由ti膜或tin膜形成的阻挡层5覆盖。如图1中所示的那样,第2布线12b中的一部分设置于与第2-1层2a的第2布线12a在俯视图中重叠的位置,与第2布线12a一体化。因此,第2布线12b的一部分通过贯通第2-1层2a的第2布线12a与第1-2层1b的第1布线11b电连接。

32.第2层2如图1中所示的那样,具有由绝缘空间20构成的第2绝缘膜。在图1中所示的

半导体装置100中,绝缘空间20兼作将第2-1层2a的相邻的第2布线12a间绝缘的绝缘膜、将第2-2层2b的相邻的第2布线12b间绝缘的绝缘膜及将第2布线12b与第1-2层1b的第1布线11b绝缘的绝缘膜。绝缘空间20由在绝缘空间20内连续地设置的由绝缘材料24形成的绝缘膜围成。作为绝缘材料24,使用sio2。绝缘空间20充满大气压或压力低于大气压的空气。

33.第3层3设置于第2层2上。第3层3具有多个第3布线(图1中未图示)、由sio2形成的第3绝缘膜23及柱状体25。

34.多个第3布线作为用于将半导体装置100与外部电连接的电极发挥功能。

35.柱状体25如图1中所示的那样,设置于在俯视图中不与布线(第1布线11a、11b、第2布线12a、12b)重叠的位置。柱状体25为俯视圆形,在第3层3中沿第1方向(图1中为上下方向)延伸,贯通绝缘空间20而到达至第1层1的第1-2层1b,在第1-2层1b内具有底面。在柱状体25内,填充有绝缘材料24。填充于柱状体25内的绝缘材料24与设置于绝缘空间20内的绝缘膜一体化。

36.在图1中所示的半导体装置100中,将绝缘空间20包围的绝缘材料24在俯视图中的厚度t优选为柱状体25(绝缘部)的直径d的一半以下。在制造这样的半导体装置100的情况下,在用于设置包围绝缘空间20的绝缘材料24的绝缘覆盖工序中,通过在成为柱状体25的贯通孔中填充绝缘材料24,可以完成在绝缘空间20内封入大气压或压力低于大气压的空气的绝缘空间形成工序。因此,成为可高效地制造的半导体装置100。另外,根据这样的半导体装置100,能够抑制包围绝缘空间20的绝缘材料24的厚度过厚而给由绝缘空间20带来的布线容量的降低效果造成障碍。

37.接着,对于制造图1中所示的半导体装置100的制造方法,使用图1~图5进行详细说明。

38.在本实施方式中,首先,在基板10上设置第1层1、含牺牲材料膜的层20a(参照图4)及配置于含牺牲材料膜的层20a上的第3层3。作为基板10,如图2中所示的那样,使用在表面具有绝缘区域10b和接触垫10a的基板。

39.第1层1例如可以如以下所示的那样,使用镶嵌(damascene)法来设置。首先,在基板10的表面设置由sio2、sin等绝缘材料形成的第1绝缘膜21a。接着,将第1绝缘膜21a图案化而设置接触孔,使接触垫10a露出。接着,在接触孔的内表面及第1绝缘膜21a上设置由ti膜或tin膜形成的阻挡层5。之后,将cu埋入至接触孔内,使用化学机械研磨(cmp)法将表面平坦化,除去第1绝缘膜21a上的多余的cu及阻挡层5。由此,如图3中所示的那样,设置具有第1布线11a的第1-1层1a。

40.接着,在第1-1层1a上设置由sio2形成的第1绝缘膜21b。然后,与第1-1层1a的第1布线11a同样地使用镶嵌(damascene)法来设置具有第1布线11b的第1-2层1b。由此,如图4中所示的那样,设置第1层1。

41.接着,在第1层1上设置含牺牲材料膜的层20a。含牺牲材料膜的层20a例如可以如以下所示的那样,使用双镶嵌(dualdamascene)法来设置。首先,在第1层1的表面设置包含由sin形成的第1牺牲材料膜22a和由sin形成的第2牺牲材料膜22b的牺牲材料膜22。接着,将第2牺牲材料膜22b图案化。之后,在第2牺牲材料膜22b的布线图案的凹部内设置贯通第1牺牲材料膜22a的接触孔,使第1布线11b露出。

42.之后,在第1牺牲材料膜22a的接触孔内及第2牺牲材料膜22b的布线图案内和第2

牺牲材料膜22b上设置由ti膜或tin膜形成的阻挡层5。接着,在第1牺牲材料膜22a的接触孔内及第2牺牲材料膜22b的布线图案内埋入cu。然后,通过使用化学机械研磨(cmp)法将表面平坦化,从而除去第2牺牲材料膜22b上的多余的cu及阻挡层5。由此,如图4中所示的那样,设置具有第2布线12a、12b的含牺牲材料膜的层20a。

43.接着,在含牺牲材料膜的层20a上设置第3层3。第3层3可以通过使用公知的方法在含牺牲材料膜的层20a的表面设置多个第3布线(未图示)和由sio2形成的第3绝缘膜23(参照图4)的方法来制造。

44.接着,在本实施方式中,通过干式蚀刻,如图5中所示的那样,设置将第3绝缘膜23、第1牺牲材料膜22a及第2牺牲材料膜22b贯通且在第1绝缘膜21b内具有底面的贯通孔25a。干式蚀刻的条件可以根据形成第3绝缘膜23、第1牺牲材料膜22a、第2牺牲材料膜22b、第1绝缘膜21b的材料而适当决定。

45.在本实施方式中,如图5中所示的那样,为了设置在第1-2层1b内具有底面的贯通孔25a,例如可以通过以第1绝缘膜21b作为停止层进行干式蚀刻的方法来设置贯通孔25a。

46.接着,通过贯通孔25a,利用湿式蚀刻,将第1牺牲材料膜22a及第2牺牲材料膜22b的一部分或全部蚀刻除去。由此,设置与所除去的第1牺牲材料膜22a及第2牺牲材料膜22b的形状相对应的孔(蚀刻工序)。

47.湿式蚀刻中使用的蚀刻液可以根据第3绝缘膜23的材料、第1牺牲材料膜22a及第2牺牲材料膜22b的材料、形成第1绝缘膜21b的材料、阻挡层5的材料以及厚度而适当决定。例如,在第3绝缘膜23及第1绝缘膜21b由sio2形成、第1牺牲材料膜22a及第2牺牲材料膜22b由sin形成的情况下,作为蚀刻液,优选使用h3po4。这种情况下,湿式蚀刻中的第3绝缘膜23及第1绝缘膜21b与第1牺牲材料膜22a及第2牺牲材料膜22b的选择比变大,能够以高精度来设置规定的形状的孔。

48.接着,在本实施方式中,将通过进行蚀刻工序而设置的孔的内表面通过贯通孔25a用由sio2形成的绝缘材料24覆盖(绝缘覆盖工序),并且将大气压或压力低于大气压的空气封入至孔内(绝缘空间形成工序)。作为将孔的内表面用绝缘材料24覆盖的方法,例如优选使用原子层成膜(ald)法、减压化学气相生长(lpcvd)法等在真空或减压条件下进行成膜的方法。作为将孔的内表面用绝缘材料24覆盖的方法,在采用在真空或减压条件下进行成膜的方法的情况下,能够容易高效地形成充满压力低于大气压的空气的绝缘空间20。

49.具体而言,优选使用ald法或lpcvd法,将孔的内表面用绝缘材料24覆盖,同时将贯通孔25a内用绝缘材料24覆盖,在贯通孔25a内填充绝缘材料24而设置柱状体25。这种情况下,在孔内充满压力低于大气压的空气的状态下,通过填充材料24而封入。因而,通过使用ald法或lpcvd法,可以容易地形成充满压力低于大气压的空气的绝缘空间20。另外,通过使用ald法或lpcvd法,由于可以与绝缘覆盖工序同时进行绝缘空间形成工序,因此能够高效地制造半导体装置100。

50.另外,使用ald法或lpcvd法而形成的膜的阶梯差覆盖性优异。因此,通过将第1牺牲材料膜22a及牺牲材料膜22b的一部分或全部蚀刻除去,能够通过由绝缘材料24形成的皮膜有效地防止在孔的内表面露出的第2布线12a、12b中的电迁移。特别是在通过使用lpcvd法将teos(正硅酸乙酯(si(oc2h5)4))分解的方法将孔的内表面用sio2覆盖的情况下,可得到阶梯差覆盖性优异的sio2膜,从而优选。通过以上的工序,可得到图1中所示的半导体装

置100。

51.图1中所示的半导体装置100具有多个布线(第1布线11a、11b、第2布线12a、12b)、和配置于相邻的布线之间(第2布线12a彼此之间、第2布线12b彼此之间、第1布线11b与第2布线12b之间)且由绝缘材料24所围成的绝缘空间20,绝缘空间20充满大气压或压力低于大气压的空气。由于大气压或压力低于大气压的空气的相对介电常数为1左右,因此绝缘空间20的相对介电常数与sio2(相对介电常数为4左右)等一般的绝缘材料相比较低。因此,图1中所示的半导体装置100例如成为与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比布线容量低的半导体装置100。

52.具体而言,图1中所示的半导体装置100具有具备多个第2布线12a、12b和由绝缘空间20构成的第2绝缘膜的第2层2、及配置于第2层2上且具有第3绝缘膜23的第3层3,相邻的第2布线12a彼此之间及第2布线12b彼此之间通过绝缘空间20被绝缘。因此,与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比,成为相邻的第2布线12a彼此之间及相邻的第2布线12b彼此之间的容量小、布线容量低的半导体装置100。

53.进而,图1中所示的半导体装置100中,第2层2具有第2-1层2a与第2-2层2b层叠而成的双层结构,在第2-1层2b所具有的第2布线12b与和第2布线12b在层叠方向上相邻的其他布线(第1层1的第1布线11b)之间配置有绝缘空间20。因此,与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比,成为第1布线11b与第2布线12b之间的容量小、布线容量低的半导体装置100。

54.在本实施方式的半导体装置100的制造方法中,具有下述工序:设置在相邻的布线之间(第2布线12a彼此之间、第2布线12b彼此之间、第1布线11b与第2布线12b之间)配置有牺牲材料膜22的含牺牲材料膜的层20a的工序;在含牺牲材料膜的层20a上设置第3绝缘膜23的工序;设置贯通第3绝缘膜23的贯通孔25a,通过贯通孔25a将牺牲材料膜22蚀刻除去而设置孔的蚀刻工序;通过贯通孔25a将孔的内表面用绝缘材料24覆盖的绝缘覆盖工序;以及向孔内封入大气压或压力低于大气压的空气的绝缘空间形成工序。

55.即,根据本实施方式的半导体装置100的制造方法,通过进行蚀刻工序、绝缘覆盖工序及绝缘空间形成工序,可以将配置于相邻的布线之间的牺牲材料膜22与封入有大气压或压力低于大气压的空气的绝缘空间20替换。其结果是,与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比,可得到布线容量低的半导体装置100。

56.(第2实施方式)

57.图6是用于说明第2实施方式的半导体装置的截面示意图。图6中所示的半导体装置200具有基板10、具有绝缘空间20的第2层2a及第2层2b、配置于第2层2a的与基板10相反侧且第2层2b的基板10侧的第3层3a、以及配置于第2层2b的与基板10相反侧的第3层3b。

58.作为基板10,与图1中所示的第1实施方式的半导体装置100同样地,例如可以使用在硅晶片上设置有晶体管等元件的基板等。在图6中所示的半导体装置200中,作为基板10,使用在表面具有由sio2形成的绝缘区域10b和接触垫10a的基板。作为接触垫10a,与图1中所示的第1实施方式的半导体装置100同样地,例如可以使用由cosi2、nisi2等公知的导电材料形成的垫。

59.在基板10上,如图6中所示的那样,设置有第2层2a。另外,在第3层3a与第3层3b之间设置有第2层2b。

60.第2层2a、2b分别具有多个第2布线12c、12e。第2布线12c、12e由cu形成,基板10侧的面及侧面被由ti膜或tin膜形成的阻挡层5覆盖。

61.另外,在第2层2a的第2布线12c中,在设置于侧面的阻挡层5的外侧设置有由ta2o5膜或hfo2膜形成的衬里层26。ta2o5膜及hfo2膜相对于h3po4的耐性良好。因此,在使用h3po4作为蚀刻液来设置成为绝缘空间20的孔的情况下,能够通过衬里层26来防止第2布线12c与蚀刻液的接触,从而优选。特别是在无法使设置于第2布线12c的侧面的阻挡层5的厚度充分厚的情况下,为了防止第2布线12c与蚀刻液的接触,优选设置有衬里层26。

62.第2布线12c为贯通第2层2a的贯通布线。如图6中所示的那样,各第2布线12c设置于与基板10的接触垫10a在俯视图中重叠的位置。各第2布线12c的基板10侧的面与接触垫10a相接触。各第2布线12c与接触垫10a电连接。

63.另外,第2层2b的第2布线12e贯通第2层2b。如图6中所示的那样,第2布线12e中的一部分设置于与第3层3a的第3布线13d在俯视图中重叠的位置,与第3布线13d的第2层2b侧的面相接触。另外,第2布线12e中的一部分设置于与第3层3b的第3布线13e在俯视图中重叠的位置,与第3布线13e的第2层2b侧的面相接触。

64.第2层2a、2b均具有由绝缘空间20构成的第2绝缘膜。在图6中所示的半导体装置200中,第2层2a的绝缘空间20将相邻的第2布线12c间绝缘,第2层2b的绝缘空间20将相邻的第2布线12e间绝缘。绝缘空间20由在绝缘空间20内连续地设置的由绝缘材料24形成的绝缘膜所围成。作为绝缘材料24,使用sio2。绝缘空间20充满大气压或压力低于大气压的空气。

65.在基板10侧的第2层2a上,如图6中所示的那样,设置有第3层3a。第3层3a如图6中所示的那样,具有从第2层2a侧起依次层叠有第3-1层3a、第3-2层3b、第3-3层3c、第3-4层3d的四层结构。另外,在第2层2b上,设置有第3层3b。第3层3b如图6中所示的那样,具有从第2层2b侧起依次层叠有第3-5层3e和第3-6层3f的双层结构。

66.第3-1层3a~第3-6层3f均具有多个第3布线13a~13f和由sio2形成的第3绝缘膜23a~23f。第3布线13a~13f均由cu形成,基板10侧的面及侧面被由ti膜或tin膜形成的阻挡层5覆盖。第3布线13a~13f均贯通第3绝缘膜23a~23f。如图6中所示的那样,第3布线13a~13f均与设置有第3布线13a~13f的层的基板10侧的层和/或与基板10相反侧的层所具有的布线相接触。

67.柱状体25如图6中所示的那样,设置于在俯视图中不与布线(第2布线12c、12e、第3布线13a~13f)重叠的位置。柱状体25为俯视圆形,贯通第3层3a、3b和第2层2b的绝缘空间20,到达至第2层2a的绝缘空间20。在柱状体25内,填充有绝缘材料24。填充于柱状体25内的绝缘材料24与设置于绝缘空间20内的绝缘膜一体化。另外,在图6中所示的半导体装置200中,将绝缘空间20包围的绝缘材料24在俯视图中的厚度也优选为柱状体25(绝缘部)的直径的一半以下。

68.接着,对制造图6中所示的半导体装置200的制造方法使用图7~图10进行详细说明。

69.在本实施方式中,首先,在基板10上依次设置含牺牲材料膜的层20b、第3层3a、含牺牲材料膜的层20c及第3层3b。作为基板10,如图7中所示的那样,使用在表面具有绝缘区域10b和接触垫10a的基板。

70.含牺牲材料膜的层20b例如可以如以下所示的那样,使用镶嵌(damascene)法来设

置。在本实施方式中,在基板10的表面设置由sin形成的牺牲材料膜22。接着,将牺牲材料膜22图案化。之后,如图7中所示的那样,在牺牲材料膜22上设置由ta2o5膜或hfo2膜形成的衬里层26。接着,例如通过使用反应性离子蚀刻(rie)法将衬里层26的一部分选择性除去的方法,仅保留牺牲材料膜22的布线图案的凹部内的侧面的衬里层26地除去衬里层26,使接触垫10a在牺牲材料膜22的凹部的底面露出(参照图8)。

71.接着,在牺牲材料膜22的凹部内及牺牲材料膜22上设置由ti膜或tin膜形成的阻挡层5。接着,将cu埋入至牺牲材料膜22的布线图案的凹部内。然后,通过使用化学机械研磨(cmp)法将表面平坦化,从而将牺牲材料膜22上的多余的cu及阻挡层5除去。由此,如图9中所示的那样,设置具有第2布线12c的含牺牲材料膜的层20b。

72.接着,在含牺牲材料膜的层20b上,例如与设置第1实施方式的半导体装置100的第1-1层1a的方法同样地操作,设置第3层3a的第3-1层3a~第3-4层3d的各层。

73.接着,在第3层3a上,例如如以下所示的那样,使用镶嵌(damascene)法来设置含牺牲材料膜的层20c。首先,在第3层3a的表面设置由sin形成的牺牲材料膜22。接着,将牺牲材料膜22图案化,使第3层3a的第3布线13d在牺牲材料膜22的布线图案的凹部内露出。

74.之后,在牺牲材料膜22的布线图案内及牺牲材料膜22上,设置由ti膜或tin膜形成的阻挡层5。接着,将cu埋入至牺牲材料膜22的布线图案内。然后,通过使用化学机械研磨(cmp)法将表面平坦化,从而将牺牲材料膜22上的多余的cu及阻挡层5除去。由此,如图10中所示的那样,设置具有第2布线12e的含牺牲材料膜的层20c。

75.接着,在含牺牲材料膜的层20c上,例如与设置第1实施方式的半导体装置100的第1-1层1a的方法同样地操作,设置第3层3b的第3-5层3e及第3-6层3f。

76.接着,在本实施方式中,通过干式蚀刻,如图10中所示的那样,设置将第3层3b、含牺牲材料膜的层20c及第3层3a贯通且在含牺牲材料膜的层20b内具有底面的贯通孔25a。干式蚀刻的条件可以根据形成第3绝缘膜23a~23f、牺牲材料膜22、基板10的绝缘区域10b的材料而适当决定。

77.接着,通过贯通孔25a,利用湿式蚀刻,将含牺牲材料膜的层20b的牺牲材料膜22的一部分或全部和含牺牲材料膜的层20c的牺牲材料膜22的一部分或全部同时蚀刻除去。由此,设置与所除去的牺牲材料膜22的形状相对应的孔(蚀刻工序)。

78.湿式蚀刻中使用的蚀刻液可以根据第3绝缘膜23a~23f的材料、牺牲材料膜22的材料、基板10的绝缘区域10b的材料、衬里层26的材料及厚度、阻挡层5的材料及厚度而适当决定。例如,在第3绝缘膜23a~23f及基板10的绝缘区域10b由sio2形成、牺牲材料膜22由sin形成的情况下,作为蚀刻液,优选使用h3po4。这种情况下,湿式蚀刻中的第3绝缘膜23a~23f及基板10的绝缘区域10b与牺牲材料膜22的选择比变大,能够以高精度来设置规定的形状的孔。

79.接着,与第1实施方式同样地进行绝缘覆盖工序及绝缘空间形成工序。

80.通过以上的工序,可得到图6中所示的半导体装置200。

81.图6中所示的半导体装置200具有多个第2布线12c、配置于相邻的布线之间的绝缘空间20、多个第2布线12e及配置于相邻的布线之间的绝缘空间20,绝缘空间20由绝缘材料24所围成,充满大气压或压力低于大气压的空气。因此,图6中所示的半导体装置200例如成为与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比布线容量低的半

导体装置200。

82.具体而言,图6中所示的半导体装置200具有第2层2a和配置于第2层2a上且具有第3绝缘膜23a~23d的第3层3a,所述第2层2a具有多个第2布线12c和由将相邻的第2布线12c彼此之间绝缘的绝缘空间20构成的第2绝缘膜。另外,图6中所示的半导体装置200具有第2层2b和配置于第2层2b上且具有第3绝缘膜23e、23f的第3层3,所述第2层2b具有多个第2布线12e和由将第2布线12e彼此之间绝缘的绝缘空间20构成的第2绝缘膜。

83.因此,与代替第2层2a及第2层2b所具有的绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比,成为相邻的第2布线12c彼此之间及相邻的第2布线12d彼此之间的容量小、布线容量低的半导体装置200。

84.另外,在图6中所示的半导体装置200中,设置有分别具有绝缘空间20的两层的第2层2a、2b。因此,本实施方式的半导体装置200例如成为与第2层为仅1层的情况相比布线容量低的半导体装置200。

85.在本实施方式的半导体装置200的制造方法中,进行下述工序:设置在相邻的布线之间(相邻的第2布线12c彼此之间)配置有牺牲材料膜22的含牺牲材料膜的层20b的工序;在含牺牲材料膜的层20b上设置具有第3绝缘膜23a~23d的第3层3a的工序;设置在相邻的布线之间(相邻的第2布线12e彼此之间)配置有牺牲材料膜22的含牺牲材料膜的层20c的工序;以及在含牺牲材料膜的层20c上设置具有第3绝缘膜23e、23f的第3层3b的工序。之后,进行下述工序:设置贯通第3绝缘膜23a~23f及含牺牲材料膜的层20c的牺牲材料膜22的贯通孔25a,通过贯通孔25a将牺牲材料膜22蚀刻除去而设置孔的蚀刻工序;通过贯通孔25a将孔的内表面用绝缘材料24覆盖的绝缘覆盖工序;以及在孔内封入大气压或压力低于大气压的空气的绝缘空间形成工序。

86.即,根据本实施方式的半导体装置200的制造方法,通过进行蚀刻工序、绝缘覆盖工序及绝缘空间形成工序,可以将配置于相邻的布线之间的牺牲材料膜22替换成封入有大气压或压力低于大气压的空气的绝缘空间20。其结果是,与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比,可得到布线容量低的半导体装置200。

87.另外,根据本实施方式的半导体装置200的制造方法,通过仅进行1次蚀刻工序、绝缘覆盖工序及绝缘空间形成工序,可以设置分别具有绝缘空间20的两层的第2层2a、2b。即,即使是制造具有多个具有绝缘空间的第2层的半导体装置的情况下,工序数也与具有绝缘空间的层为仅1层的情况相同,没有必要根据具有绝缘空间的层的数目来增加工序数。因而,根据本实施方式的半导体装置的制造方法,即使是制造具有多个具有绝缘空间的第2层的半导体装置的情况下,也能够高效地制造。

88.需要说明的是,在第1实施方式中,列举出第2层、配置于第2层的基板侧的第1层及配置于第2层的与基板相反侧的第3层分别各为1层的情况为例进行了说明,在第2实施方式中,列举出分别各具有两层第2层及第3层、第2层与第3层交替地层叠的情况为例进行了说明,但例如也可以是如图11~图13中所示的那样,第2层和/或第3层设置有三层以上的半导体装置。需要说明的是,在第2层设置有两层以上的情况下,配置于在层叠方向上相邻的第2层间的第3层兼作第1层。

89.图11~图13是用于说明实施方式的半导体装置的其他例子的截面示意图。图11~图13是表示制造途中的半导体装置的图。图11~图13均表示在制造半导体装置的工序中在

设置贯通孔25a后将牺牲材料膜22蚀刻除去之前的状态的图。

90.图11中所示的制造途中的半导体装置300在与第1实施方式的半导体装置100同样的基板10上具有第1实施方式中的第1层1。如图11中所示的那样,在第1层1上,交替地各层叠有两层第1实施方式中的含牺牲材料膜的层20a和第2实施方式中的第3层3b。进而,如图11中所示的那样,在与基板10相反侧的第3层3b上,层叠有含牺牲材料膜的层20a和第1实施方式中的第3层3。在图11中所示的制造途中的半导体装置300中,设置有将第3层3的第3绝缘膜23、第3层3b的第3绝缘膜23e、23f及含牺牲材料膜的层20a的牺牲材料膜22贯通且在第1层1的第1绝缘膜21b内具有底面的贯通孔25a。

91.图11中所示的半导体装置300如图11中所示的那样,具有三层的含牺牲材料膜的层20a。在本实施方式中,通过仅进行1次蚀刻工序、绝缘覆盖工序及绝缘空间形成工序而将三层的含牺牲材料膜的层20a所具有的牺牲材料膜22替换成绝缘空间20。其结果是,可得到在第1层1上交替地各层叠有两层第1实施方式中的第2层2和第2实施方式中的第3层3b、进而在与基板10相反侧的第3层3b上层叠有第1实施方式中的第2层2和第3层3的半导体装置。像这样操作而得到的半导体装置与上述的实施方式同样地成为与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比布线容量低的半导体装置。

92.图12中所示的制造途中的半导体装置400具有与第2实施方式的半导体装置200同样的基板10。如图12中所示的那样,在基板10上设置有含牺牲材料膜的层20d。含牺牲材料膜的层20d除了未设置衬里层以外,为与第2实施方式中的含牺牲材料膜的层20b同样的层。因此,含牺牲材料膜的层20d除了不设置衬里层以外,可以与第2实施方式中的含牺牲材料膜的层20b同样地操作而设置。

93.在图12中所示的含牺牲材料膜的层20d上,层叠有第2实施方式中的含牺牲材料膜的层20c、两层第2实施方式中的第3层3b、第1实施方式中的含牺牲材料膜的层20a、两层第2实施方式中的第3层3b及第1实施方式中的第3层3。在图12中所示的制造途中的半导体装置400中,设置有将第3层3的第3绝缘膜23、第3层3b的第3绝缘膜23e、23f及含牺牲材料膜的层20a、20c的牺牲材料膜22贯通且在含牺牲材料膜的层20d的牺牲材料膜22内具有底面的贯通孔25a。

94.在本实施方式中,通过仅进行1次蚀刻工序、绝缘覆盖工序及绝缘空间形成工序而将图12中所示的半导体装置400的含牺牲材料膜的层20a、20c、20d所具有的牺牲材料膜22替换成绝缘空间20。其结果是,可得到在基板10上层叠有具有兼作将含牺牲材料膜的层20d的相邻的第2布线12c间绝缘的绝缘膜和将含牺牲材料膜的层20c的相邻的第2布线12e间绝缘的绝缘膜的绝缘空间20的第2层、两层第2实施方式中的第3层3b、第1实施方式中的第2层2、两层第3层3b以及第1实施方式中的第3层3的半导体装置。像这样操作而得到的半导体装置与上述的实施方式同样地成为与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比布线容量低的半导体装置。

95.图13中所示的制造途中的半导体装置500具有与第1实施方式的半导体装置100同样的基板10。如图13中所示的那样,在基板10上设置有第1层1c。第1层1c除了具有由sio2形成的第1绝缘膜21a、且在第1绝缘膜21a内具有贯通孔25a的底面以外,为与第1实施方式中的第1层1的第1-1层1a同样的层。

96.在图13中所示的第1层1c上,层叠有第2实施方式中的含牺牲材料膜的层20c、两层

第2实施方式中的第3层3b、图12中所示的含牺牲材料膜的层20d、第2实施方式中的第3层3b的第3-6层3f、两层第2实施方式中的第3层3b及第1实施方式中的第3层3。如图13中所示的那样,按照夹持含牺牲材料膜的层20d的方式配置的第3-6层3f所具有的第3布线13f彼此隔着含牺牲材料膜的层20d而相向配置。在图13中所示的制造途中的半导体装置500中,设置有将第3层3的第3绝缘膜23、第3绝缘膜23e、23f及含牺牲材料膜的层20c、20d的牺牲材料膜22贯通且在第1层1c的第1绝缘膜21a内具有底面的贯通孔25a。

97.在本实施方式中,通过仅进行1次蚀刻工序、绝缘覆盖工序及绝缘空间形成工序而将图13中所示的半导体装置500的含牺牲材料膜的层20c、20d所具有的牺牲材料膜22替换成绝缘空间20。其结果是,可得到在基板10上层叠有第1层1c、具有绝缘空间20作为将含牺牲材料膜的层20c的相邻的第2布线12e间绝缘的绝缘膜的第2层、两层第2实施方式中的第3层3b、具有绝缘空间20作为将含牺牲材料膜的层20d的相邻的第2布线12c间绝缘的绝缘膜的第2层、第2实施方式中的第3层3b的第3-6层3f、两层第2实施方式中的第3层3b以及第1实施方式中的第3层3的半导体装置。

98.像这样操作而得到的半导体装置与上述的实施方式同样地成为与代替绝缘空间20而配置由一般的绝缘材料形成的绝缘层的情况相比布线容量低的半导体装置。需要说明的是,在该半导体装置中,在隔着含牺牲材料膜的层20d而在层叠方向上相向配置的第3布线13f间配置有绝缘空间。因此,与代替绝缘空间而配置由一般的绝缘材料形成的绝缘层的情况相比,成为相向配置的第3布线13f间的容量小、布线容量低的半导体装置。

99.在第1实施方式中,列举出第1层为双层结构的情况为例进行了说明,在第2实施方式中,列举出无第1层的情况为例进行了说明,但第1层可以仅为1层,也可以为3层以上。

100.在第1实施方式中,列举出第2层为双层结构的情况为例进行了说明,在第2实施方式中,列举出第2层仅为1层的情况为例进行了说明,但第2层也可以为3层以上。

101.在第1实施方式及第2实施方式中,列举出设置有俯视圆形的柱状体25的情况为例进行了说明,但柱状体的平面形状并不限定于圆形。例如也可以为俯视矩形的槽状。

102.在图1、图6中仅记载了1个柱状体25,在图11~图13中仅记载了1个通过填充绝缘材料而成为柱状体的贯通孔25a,但本实施方式的半导体装置所具有的柱状体(贯通孔)的数目可以为1个,也可以为多个,可以根据半导体装置在俯视图中的面积、绝缘空间的数目、牺牲材料膜的蚀刻条件等而适当决定。

103.在第1实施方式及第2实施方式中,列举出绝缘膜由sio2形成、牺牲材料膜由sin形成、使用含有h3po4的蚀刻液的情况为例进行了说明,但绝缘膜与牺牲材料膜与蚀刻液的组合并不限定于该例子。例如在绝缘膜由sio2形成、牺牲材料膜由多晶硅形成的情况下,作为蚀刻液,可以使用胆碱溶液(三甲基-2-羟乙基氢氧化铵水溶液)。

104.在第1实施方式及第2实施方式中,作为布线,列举出由cu形成、且基板侧的面及侧面被由ti膜或tin膜形成的阻挡层覆盖的布线为例进行了说明,但可以使用由公知的材料形成的布线,并不限定于具有上述的材料及结构的布线。

105.在第2实施方式中,列举出衬里层26为由ta2o5膜或hfo2膜形成的层的情况为例进行了说明,但衬里层的材料可以根据为了设置成为绝缘空间的孔而使用的蚀刻液的组成而适当决定,衬里层并不限定于由ta2o5膜或hfo2膜形成的层。

106.根据以上说明的至少一个实施方式,通过具有多个布线和配置于相邻的布线之间

且由绝缘材料所围成的绝缘空间,且绝缘空间充满大气压或压力低于大气压的空气,从而成为布线容量低的半导体装置。

107.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些实施方式可以以其他的各种方式来实施,在不脱离发明的主旨的范围内,可以进行各种省略、置换、变更。这些实施方式或其变形包含于发明的范围、主旨中,同样地包含于权利要求书中记载的发明和其同等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1