半导体装置的制作方法

半导体装置

1.相关申请案的引用

2.本技术案是基于2020年03月24日提出申请的在先日本专利申请案第2020-053410号的优先权而主张优先权利益,通过引用将其全部内容并入本文中。

技术领域

3.本实施方式涉及一种半导体装置。

背景技术:

4.已知一种半导体装置,具备半导体衬底、设置在半导体衬底上方的第1半导体层、及设置在第1半导体层上方的第2半导体层,且将这些构成用作电容器。

技术实现要素:

5.一实施方式提供一种高速动作的半导体装置。

6.一实施方式的半导体装置具备:半导体衬底;第1半导体层,在与半导体衬底的表面交叉的第1方向上与半导体衬底的表面对向;第2半导体层,相比第1半导体层距半导体衬底较远,在第1方向上与第1半导体层对向;第1导电层,相比第2半导体层距半导体衬底较远,连接于第2半导体层;第3半导体层,在与第1方向交叉的第2方向上与第2半导体层并排,连接于第1半导体层;及第2导电层,在第2方向上与第1导电层并排,连接于第3半导体层。第1半导体层、第2半导体层及第3半导体层是将与第1方向及第2方向交叉的第3方向作为长度方向。

7.根据所述构成,可提供一种高速动作的半导体装置。

附图说明

8.图1是表示第1实施方式的第1构成的存储系统100的构成例的示意性侧视图。

9.图2是表示该存储系统100的构成例的示意性俯视图。

10.图3是表示存储器裸片md的构成的示意性俯视图。

11.图4是表示存储器裸片md的构成的示意性电路图。

12.图5是将图3所示的构造沿v-v线切断并沿箭头方向观察时的示意性剖视图。

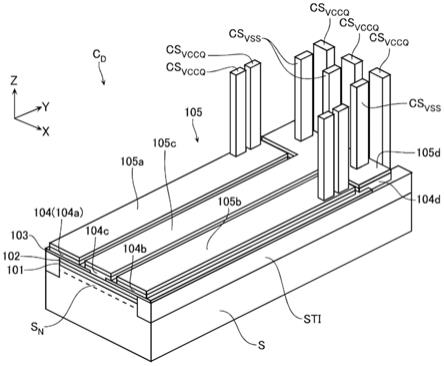

13.图6是将图3所示的构造沿vi-vi线切断并沿箭头方向观察时的示意性剖视图。

14.图7是表示配线层m2的构成的示意性俯视图。

15.图8是表示配线层mx的构成的示意性俯视图。

16.图9是表示元件层dl的构成的示意性俯视图。

17.图10是表示半导体衬底s的构成的示意性俯视图。

18.图11是表示去耦电容器c

d

的构成的示意性立体图。

19.图12是表示去耦电容器c

d

的一部分构成的示意性立体图。

20.图13是表示去耦电容器c

d

的一部分构成的示意性立体图。

21.图14是表示去耦电容器c

d

的一部分构成的示意性立体图。

22.图15是表示比较例的元件层dl'的构成的示意性俯视图。

23.图16是表示比较例的去耦电容器c

d

'的构成的示意性立体图。

24.图17是表示去耦电容器c

d

'的一部分构成的示意性立体图。

25.图18是用来对去耦电容器c

d

、c

d

'的频率特性进行说明而示出的曲线图。

26.图19是表示第2实施方式的元件层dl2的构成的示意性俯视图。

27.图20是表示第2实施方式的半导体衬底s的构成的示意性俯视图。

28.图21是表示第2实施方式的去耦电容器c

d2

的构成的示意性立体图。

29.图22是表示第3实施方式的去耦电容器c

d3

的构成的示意性俯视图。

30.图23是表示第3实施方式的半导体衬底s的构成的示意性俯视图。

31.图24是表示第4实施方式的元件层dl4的构成的示意性俯视图。

32.图25是表示第5实施方式的元件层dl5的构成的示意性俯视图。

33.图26是将图25所示的构造沿xxvi-xxvi线切断并沿箭头方向观察时的示意性剖视图。

34.图27是将图25所示的构造沿xxvii-xxvii线切断并沿箭头方向观察时的示意性剖视图。

35.图28是用来对去耦电容器c

d5

、c

d

'的频率特性进行说明而示出的曲线图。

36.图29是表示第6实施方式的元件层dl6的构成的示意性俯视图。

37.图30是将图29所示的构造沿xxx-xxx线切断并沿箭头方向观察时的示意性剖视图。

38.图31是将图29所示的构造沿xxxi-xxxi线切断并沿箭头方向观察时的示意性剖视图。

具体实施方式

39.接下来,参照附图对实施方式的半导体装置详细地进行说明。此外,以下实施方式仅为一例,并不意图限定本发明。

40.另外,在本说明书中,将与半导体衬底的表面平行的指定方向称为x方向,将与半导体衬底的表面平行且与x方向垂直的方向称为y方向,将与半导体衬底的表面垂直的方向称为z方向。

41.另外,在本说明书中,有时将沿指定平面的方向称为第1方向,将沿该指定平面与第1方向交叉的方向称为第2方向,将与该指定平面交叉的方向称为第3方向。这些第1方向、第2方向及第3方向可与x方向、y方向及z方向中任一方向对应,也可不对应。

42.另外,在本说明书中,“上”或“下”等表述是以半导体衬底为基准。例如,将沿z方向远离半导体衬底的方向称为上,将沿z方向靠近半导体衬底的方向称为下。另外,在针对某一构成记述为下表面或下端部的情况下,是指该构成的半导体衬底侧的面或端部,在记述为上表面或上端部的情况下,是指该构成的与半导体衬底相反侧的面或端部。另外,将与x方向或y方向交叉的面称为侧面等。

43.另外,在本说明书中,在记述为第1构成“电连接”于第2构成的情况下,可为第1构成直接连接于第2构成,也可为第1构成经由配线、半导体部件或晶体管等连接于第2构成。

例如在将3个晶体管串联连接的情况下,即便第2个晶体管为断开(off)状态,第1个晶体管也“电连接”于第3个晶体管。

44.另外,在本说明书中,在记述为第1构成“连接于”第2构成与第3构成“之间”的情况下,有时是指第1构成、第2构成及第3构成串联连接,且第1构成设置在第2构成及第3构成的电流路径中。

45.另外,在本说明书中,在记述为电路等使2条配线等“导通”的情况下,例如,有时是指该电路等包含晶体管等,该晶体管等设置在2条配线之间的电流路径中,该晶体管等成为接通(on)状态。

46.[第1实施方式]图1是表示本实施方式的第1构成的存储系统100的构成例的示意性侧视图。图2是表示存储系统100的构成例的示意性俯视图。为了便于说明,在图1及图2中省略了一部分构成。

[0047]

如图1所示,第1构成的存储系统100具备安装衬底msb、在安装衬底msb上积层的多个存储器裸片md、及在存储器裸片md上积层的控制裸片cd。在安装衬底msb上表面中的y方向的端部区域设置着焊垫电极p,其它一部分区域经由粘接剂等连接于存储器裸片md的下表面。在存储器裸片md上表面中的y方向的端部区域设置着焊垫电极p,其它区域经由粘接剂等连接于另一存储器裸片md或控制裸片cd的下表面。在控制裸片cd上表面中的y方向的端部区域设置着焊垫电极p。

[0048]

如图2所示,安装衬底msb、多个存储器裸片md及控制裸片cd分别具备多个焊垫电极p。设置在安装衬底msb、多个存储器裸片md及控制裸片cd上的多个焊垫电极p分别经由键合线b相互连接。

[0049]

图3是表示存储器裸片md的构成的示意性俯视图。在图3的示例中,存储器裸片md具备半导体衬底s、设置在半导体衬底s上表面的存储单元阵列mca、及设置在存储单元阵列mca周边的周边电路pc。在图3的示例中,在半导体衬底s上表面设置着沿x方向排列的2个存储单元阵列mca。各存储单元阵列mca具备沿y方向排列的多个存储块mb。另外,在周边电路pc的一部分设置着焊垫电极p。

[0050]

图4是表示存储器裸片md的一部分构成的示意性电路图。如图4所示,存储器裸片md具备多个焊垫电极p、连接于这些多个焊垫电极p的多个去耦电容器c

d

、及连接于这些多个焊垫电极p的内部电路ic。

[0051]

多个焊垫电极p中的一部分连接于传输输入信号及输出信号的输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

。这些多个输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

连接于内部电路ic中所包含的未图示的比较器等。

[0052]

另外,多个焊垫电极p中的一部分连接于向存储器裸片md中的各构成供给接地电压vss的电压传输线w

vss

。电压传输线w

vss

连接于内部电路ic。另外,在电压传输线w

vss

与输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

之间分别连接着下拉电路pd。下拉电路pd包含并联连接于电压传输线w

vss

与输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

之间的多个nmos(n-channel metal oxide semiconductor,n沟道金氧半导体)晶体管。

[0053]

另外,多个焊垫电极p中的一部分连接于向存储器裸片md中的各构成供给驱动电压vccq的电压传输线w

vccq

。电压传输线w

vccq

连接于内部电路ic。另外,在电压传输线w

vccq

与输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

之间分别连接着提升电路pu。提升电路pu包含并联

连接于电压传输线w

vccq

与输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

之间的多个pmos(p-channel metal oxide semiconductor,p沟道金氧半导体)晶体管。

[0054]

多个去耦电容器c

d

并联连接于电压传输线w

vss

与电压传输线w

vccq

之间。

[0055]

内部电路ic包含参照图3所说明的存储单元阵列mca及周边电路pc。周边电路pc在输出数据时,驱动与输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

对应的下拉电路pd或提升电路pu。由此,输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

与电压传输线w

vss

或电压传输线w

vccq

导通。

[0056]

接下来,参照图5~图14对存储器裸片md的构成例进行说明。

[0057]

图5是将图3所示的构造沿v-v线切断并沿箭头方向观察时的示意性剖视图。图6是将图3所示的构造沿vi-vi线切断并沿箭头方向观察时的示意性剖视图。

[0058]

如图5及图6所示,存储器裸片md具备设置在上表面的钝化层pl、设置在钝化层pl下方的配线层m2、设置在配线层m2下方的配线层m1、设置在配线层m1下方的配线层m0、设置在配线层m0下方的配线层mx、设置在配线层mx下方的元件层dl、及设置在元件层dl下方的半导体衬底s。

[0059]

图7是用来对配线层m2的构成进行说明的示意性俯视图。配线层m2例如具备包含氮化钛(tin)及铝(al)等的多条配线m2。配线m2中的一部分作为焊垫电极p发挥功能。焊垫电极p形成为大致矩形。如图5及图6所示,焊垫电极p上表面的一部分由聚酰亚胺等钝化层pl覆盖。另外,如图5及图6所示,焊垫电极p上表面的一部分经由设置在钝化层pl的开口op

pl

露出于外部。另外,如图7所示,在焊垫电极p的上表面设置着与键合线b(图1、图2)接触的大致圆形的键合区域bb。

[0060]

图8是用来对配线层mx的构成进行说明的示意性俯视图。配线层mx例如具备包含氮化钛(tin)及钨(w)等的多条配线mx。

[0061]

在配线层mx中的从z方向观察时与焊垫电极p重叠的区域设置着大致圆形的绝缘区域ri、及包围该大致圆形的绝缘区域ri的大致矩形的导电区域rc。绝缘区域ri例如是由氧化硅(sio2)等绝缘层51嵌埋的区域,是不包含导电部件等的区域。在绝缘区域ri的内侧设置着与焊垫电极p和键合线b的接触面对应的键合区域bb。导电区域rc例如具备沿x方向延伸且沿y方向排列的多个导电部件52、及沿y方向延伸且沿x方向排列的多个导电部件53。导电部件52、53为所述多条配线mx中的一部分。另外,在导电部件52、53之间设置着氧化硅(sio2)等绝缘层54。

[0062]

在配线层mx中的从z方向观察时不与焊垫电极p重叠的区域设置着沿x方向及y方向排列的6组配线群wg。这6组配线群wg分别具备沿x方向延伸且沿y方向排列的多条配线mx。这些多条配线mx分别作为所述电压传输线w

vss

或电压传输线w

vccq

的一部分发挥功能。另外,在这6组配线群的周围设置着以包围这6组配线群wg及所述导电部件52、53的方式配置的配线mx。该配线mx作为所述电压传输线w

vss

的一部分发挥功能。

[0063]

此外,对详细构成进行了省略,但配线层m0(图5、图6)例如具备包含氮化钛(tin)及钨(w)等的多条配线m0。另外,配线层m1(图5、图6)例如具备包含氮化钛(tin)及铜(cu)等的多条配线m1。另外,在配线层m0及配线层m1中的从z方向观察时与焊垫电极p重叠的区域设置着如参照图8所说明的大致圆形的绝缘区域、及包围该大致圆形的绝缘区域的大致矩形的导电区域。

[0064]

图9是用来对元件层dl的构成进行说明的示意性俯视图。将图9所示的构造沿v-v

线切断并沿箭头方向观察时的截面示意性地相当于图5的元件层dl。将图9所示的构造沿vi-vi线切断并沿箭头方向观察时的截面示意性地相当于图6的元件层dl。在元件层dl上设置着多个去耦电容器c

d

的一部分构成。在图9的示例中,与一个焊垫电极p对应而设置着沿x方向及y方向排列的6个去耦电容器c

d

。这6个去耦电容器c

d

从与焊垫电极p重叠的区域沿y方向延伸到不与焊垫电极p重叠的区域。另外,在与所述配线群wg(图8)对应的区域设置着将所述配线群wg中的配线mx与去耦电容器c

d

连接的多个接触电极cs

vss

、cs

vccq

。另外,在这6个去耦电容器c

d

的周围设置着以包围这6个去耦电容器c

d

的方式配置的多个接触电极cs

vss

。

[0065]

图10是用来对半导体衬底s的构成进行说明的示意性俯视图。半导体衬底s例如为包含硼(b)等p型杂质的单晶硅等的半导体衬底。在半导体衬底s上设置着半导体衬底区域s

s

、及以包围该半导体衬底区域s

s

的方式设置的p阱区域s

pw

。

[0066]

在半导体衬底区域s

s

中的与去耦电容器c

d

对应的区域分别设置着杂质区域s

n

。杂质区域s

n

例如包含磷(p)或砷(as)等n型杂质。另外,在杂质区域s

n

的y方向一端设置着杂质区域s

n+

。杂质区域s

n+

例如包含磷(p)或砷(as)等n型杂质。杂质区域s

n+

中的杂质浓度大于杂质区域s

n

中的杂质浓度。

[0067]

p阱区域s

pw

例如包含硼(b)等p型杂质。p阱区域s

pw

中的杂质浓度大于半导体衬底区域s

s

中的杂质浓度。在p阱区域s

pw

中的与所述多个接触电极cs

vss

对应的区域设置着杂质区域s

p+

。杂质区域s

p+

例如包含硼(b)等p型杂质。杂质区域s

p+

中的杂质浓度大于p阱区域s

pw

中的杂质浓度。

[0068]

图11是表示图9中的一个去耦电容器c

d

的构成的示意性立体图。图12~图14是从图11中将一部分构成省略后的示意性立体图。

[0069]

如图11所示,本实施方式的去耦电容器c

d

具备设置在半导体衬底s的杂质区域s

n

、设置在半导体衬底s上表面的绝缘层101、设置在绝缘层101上表面的半导体层102、设置在半导体层102上表面的绝缘层103、设置在绝缘层103上表面的半导体层104、及设置在半导体层104上表面的导电层105。如图9及图10所示,这些构成是将y方向作为长度方向,从自z方向观察时与焊垫电极p重叠的区域延伸到自z方向观察时不与焊垫电极p重叠的区域。

[0070]

绝缘层101例如包含氧化硅(sio2)等。

[0071]

半导体层102包含含有磷(p)或砷(as)等n型杂质、或硼(b)等p型杂质的多晶硅等。如图5及图6所示,半导体层102的下表面介隔绝缘层101与杂质区域s

n

的上表面对向。

[0072]

此外,如图5所示,在x方向上相邻的2个去耦电容器c

d

中所包含的杂质区域s

n

、绝缘层101及半导体层102介隔绝缘层sti相互隔开。另外,如图6所示,在y方向上相邻的2个去耦电容器c

d

中所包含的杂质区域s

n

、绝缘层101及半导体层102介隔绝缘层sti相互隔开。绝缘层sti例如包含氧化硅(sio2)等。

[0073]

绝缘层103例如包含氧化硅(sio2)等。如图14所示,在绝缘层103上设置着沿y方向延伸的开口op

103

。在图示的例子中,绝缘层103经由开口op

103

被截成沿x方向排列的2个部分即绝缘层103a、绝缘层103b。绝缘层103a、绝缘层103b的下表面设置在半导体层102及绝缘层sti的上表面。

[0074]

半导体层104(图11)包含含有磷(p)或砷(as)等n型杂质、或硼(b)等p型杂质的多晶硅等。如图11所示,半导体层104包含沿x方向排列的2个部分即半导体层104a、半导体层104b、设置在它们之间的半导体层104c、及连接于半导体层104c的y方向一端部的半导体层

104d。

[0075]

如图11所示,半导体层104a是将y方向作为长度方向。该半导体层104a的下表面介隔绝缘层103a(图14)与半导体层102的一部分区域102a(图13)对向。

[0076]

如图11所示,半导体层104b是将y方向作为长度方向。半导体层104b的下表面介隔绝缘层103b(图14)与半导体层102的一部分区域102b(图13)对向。

[0077]

如图11所示,半导体层104c是将y方向作为长度方向。半导体层104c的下表面经由绝缘层103的所述开口op

103

(图14)连接于半导体层102的一部分区域102c(图13)。

[0078]

如图11所示,半导体层104d是将x方向作为长度方向。半导体层104d的下表面连接于半导体层102的一部分区域102d(图13)。从z方向观察时,半导体层104d与绝缘层103a重叠一部分(图6)。

[0079]

导电层105(图11)包含钨硅化物(wsi)等。如图11所示,导电层105包含沿x方向排列的2个导电层105a、导电层105b、设置在它们之间的导电层105c、及连接于导电层105c的y方向一端部的导电层105d。

[0080]

导电层105a是将y方向作为长度方向。导电层105a的下表面连接于半导体层104a的上表面。此外,如图10所示,导电层105a沿着杂质区域s

n

的x方向端部在y方向上延伸。但是,导电层105a不到达杂质区域s

n

的y方向端部。因此,杂质区域s

n

的角部s

ne

不由导电层105a覆盖。半导体层104a也同样如此。

[0081]

导电层105b是将y方向作为长度方向。导电层105b的下表面连接于半导体层104b的上表面。此外,如图10所示,导电层105b沿着杂质区域s

n

的x方向端部在y方向上延伸。但是,导电层105b不到达杂质区域s

n

的y方向端部。因此,杂质区域s

n

的角部s

ne

不由导电层105b覆盖。半导体层104b也同样如此。

[0082]

导电层105c是将y方向作为长度方向。导电层105c的下表面连接于半导体层104c的上表面。此外,如图10所示,导电层105c沿y方向延伸,到达杂质区域s

n

的y方向端部。半导体层104c也同样如此。

[0083]

导电层105d是将x方向作为长度方向。导电层105d的下表面连接于半导体层104d的上表面。

[0084]

接触电极cs

vss

与被供给接地电压vss的焊垫电极p导通。接触电极cs

vss

是沿z方向延伸的通孔接触电极,例如包含氮化钛(tin)及钨(w)等。图11所例示的接触电极cs

vss

沿x方向设置多个,且分别连接于导电层105d的上表面。另外,这些接触电极cs

vss

的上端连接于参照图8所说明的配线群wg中的作为电压传输线w

vss

发挥功能的配线mx。导电层105d及导电层105c的下表面与半导体层104d及半导体层104c的上表面连接。半导体层104d及半导体层104c的下表面与半导体层102d及半导体层102c的上表面连接。由此,也向所述半导体层102a、102b供给接地电压vss。

[0085]

接触电极cs

vccq

与被供给驱动电压vccq的焊垫电极p导通。接触电极cs

vccq

是沿z方向延伸的通孔接触电极,例如包含氮化钛(tin)及钨(w)等。

[0086]

图11所例示的接触电极cs

vccq

中的一部分沿y方向设置多个,且分别连接于导电层105a的上表面。另外,图11所例示的接触电极cs

vccq

中的一部分沿y方向设置多个,且分别连接于导电层105b的上表面。另外,这些接触电极cs

vccq

的上端连接于参照图8所说明的配线群wg中的作为电压传输线w

vccq

发挥功能的配线mx。导电层105a及导电层105b的下表面与半

导体层104a及半导体层104b的上表面连接。由此,向所述半导体层104a、104b供给驱动电压vccq。

[0087]

图11所例示的接触电极cs

vccq

中的一部分如图12所示,沿x方向设置多个,且分别连接于半导体衬底s。此外,如图6所示,在半导体衬底s的与接触电极cs

vccq

的连接部分设置着杂质区域s

n+

。另外,这些接触电极cs

vccq

的上端连接于参照图8所说明的配线群wg中的作为电压传输线w

vccq

发挥功能的配线mx。由此,向半导体衬底s的杂质区域s

n

供给驱动电压vccq。

[0088]

[比较例]接下来,参照图15~图17对比较例的存储器裸片进行说明。图15是表示比较例的存储器裸片的一部分构成的示意性俯视图。图16是表示图15所示的构成的一部分的示意性立体图。图17是从图16所示的构成中将一部分构成省略后的示意性立体图。

[0089]

比较例的存储器裸片与第1实施方式的存储器裸片不同,不具备去耦电容器c

d

。作为代替,比较例的存储器裸片具备去耦电容器c

d

'。

[0090]

如图16所示,比较例的去耦电容器c

d

'具备杂质区域s

n

、设置在半导体衬底s上表面的绝缘层101、设置在绝缘层101上表面的半导体层102、设置在半导体层102上表面的绝缘层103'、设置在绝缘层103'上表面的半导体层104'、及设置在半导体层104'上表面的导电层105'。如图15所示,这些构成是将y方向作为长度方向,从自z方向观察时与焊垫电极p重叠的区域延伸到自z方向观察时不与焊垫电极p重叠的区域。

[0091]

绝缘层103'(图16)基本上与绝缘层103(图12)同样地构成。但是,如图17所示,绝缘层103'不具有开口op

103

(图14),未被截成2个部分。

[0092]

半导体层104'(图16)包含含有磷(p)或砷(as)等n型杂质、或硼(b)等p型杂质的多晶硅等。如图16所示,半导体层104'包含沿y方向排列的2个部分即半导体层104a'、半导体层104d'。半导体层104a'的下表面介隔绝缘层103'与半导体层102的上表面的一部分区域对向。半导体层104d'的下表面连接于半导体层102的一部分区域的上表面。

[0093]

导电层105'包含钨硅化物(wsi)等。导电层105'包含沿y方向排列的2个部分即导电层105a'、导电层105d'。导电层105a'的下表面连接于半导体层104a'的上表面。导电层105d'的下表面连接于半导体层104a'的上表面。

[0094]

图17所例示的接触电极cs

vss

沿x方向设置多个,且分别连接于导电层105d'的上表面。由此,向所述半导体层102供给接地电压vss。此外,如图15所示,接触电极cs

vss

设置在从z方向观察时不与焊垫电极p重叠的位置。

[0095]

[效果]将键合线b(图1、图2)安装于焊垫电极p时,利用毛细管向下按压焊垫电极p。此时,经由焊垫电极p也对配线mx、m0、m1施加应力。此处,如果在产生这种应力的区域设置所述配线mx、m0、m1,那么有可能应力会集中到这些配线mx、m0、m1附近的绝缘层,导致在该绝缘层产生龟裂。如果毛细管在这种状态下向上方移动,那么包含焊垫电极p的一部分构造可能与键合线b一同从半导体衬底s上被揭下。为了抑制这种现象,在比较例中,例如与参照图8所说明的第1实施方式同样地,不在与焊垫电极p和键合线b的接触面对应的键合区域bb设置配线mx、m0、m1。

[0096]

此处,连接于去耦电容器c

d

'的多个接触电极cs

vss

、cs

vccq

在上端连接于参照图8所说明的配线群wg中的配线mx。因此,在将这些配线群wg设置在不与焊垫电极p重叠的区域的情况下,接触电极cs

vss

、cs

vccq

也设置在不与焊垫电极p重叠的区域。因此,在比较例的去耦

电容器c

d

'中,将作为电容器的电极发挥功能的杂质区域s

n

、半导体层102及半导体层104'在不与焊垫电极p重叠的区域中,与接触电极cs

vss

、cs

vccq

连接。

[0097]

此处,半导体层102的电阻率大于导电层105'(图16)的电阻率。因此,存在以下情况:如果参照图4所说明的输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

的信号频率变大,那么半导体层102中的设置在距导电层105d'相对较远的区域的部分不易作为电容器发挥功能。在这种情况下,存在输入输出信号线w

io0

、w

io1

、w

io2

、w

io3

……

的电压变得不稳定的情况。

[0098]

此处,如参照图14所说明,在第1实施方式的去耦电容器c

d

中,在绝缘层103上设置着沿y方向延伸的开口op

103

。另外,如参照图11所说明,半导体层104c经由该开口op

103

连接于半导体层102的上表面。另外,导电层105c连接于半导体层104c的上表面。

[0099]

根据这种构成,能够使半导体层102整体经由导电层105c靠近导电层105d。由此,不在如参照图7所说明的键合区域bb配置接触电极cs

vss

等,便能使半导体层102的充放电高速化。因此,能够一边抑制如上所述的焊垫电极p的剥离,一边抑制伴随信号频率的高速化所造成的电容值的衰减。

[0100]

图18是表示去耦电容器c

d

、c

d

'的信号频率与电容值的关系的曲线图。此外,图18所示的特性之中,去耦电容器c

d

的相关特性表示与半导体层102上表面和半导体层104下表面之间的电容值相关的模拟结果。另外,图18所示的特性之中,去耦电容器c

d

'的相关特性表示与半导体层102'上表面和半导体层104'下表面之间的电容值相关的模拟结果。

[0101]

在信号频率相对较小的情况下,去耦电容器c

d

'的电容值大于去耦电容器c

d

的电容值。认为其原因在于:在去耦电容器c

d

中,不以半导体层104介隔绝缘层103与半导体层102c(图13)对向的方式配置,所以不蓄积电荷。

[0102]

在信号频率相对较大的情况下,去耦电容器c

d

的电容值大于去耦电容器c

d

'的电容值。认为其原因在于:在去耦电容器c

d

'中,半导体层102的一部分区域距导电层105d'较远,这种部分中的充放电速度较小。另外,认为其原因在于:在去耦电容器c

d

中,半导体层102整体设置在导电层105d附近,在半导体层102的区域102a、102b中,高速地进行充放电。

[0103]

[第2实施方式]接下来,参照图19~图21对第2实施方式的存储器裸片进行说明。图19及图20是用来对本实施方式的存储器裸片的构成进行说明的示意性俯视图。图21是用来对本实施方式的存储器裸片的构成进行说明的示意性立体图。此外,在以下说明中,对与第1实施方式相同的构成要素标注相同符号,并省略说明。

[0104]

本实施方式的存储器裸片基本上与第1实施方式的存储器裸片md同样地构成。但是,本实施方式的存储器裸片不具备去耦电容器c

d

,作为代替,具备去耦电容器c

d2

。本实施方式的去耦电容器c

d2

基本上与第1实施方式的去耦电容器c

d

同样地构成。但是,本实施方式的去耦电容器c

d2

不具备绝缘层103、半导体层104及导电层105,作为代替,具备绝缘层203、半导体层204及导电层205。

[0105]

绝缘层203基本上与绝缘层103同样地构成。但是,绝缘层203不具有所述开口op

103

(图14),不被截成2个部分。另外,绝缘层203不覆盖半导体层102的x方向的一侧端部。

[0106]

半导体层204基本上与半导体层104同样地构成。但是,半导体层204仅具备与半导体层104a对应的半导体层204a、与半导体层104c对应的半导体层204c、及与半导体层104d对应的半导体层204d,不具备与半导体层104b对应的半导体层204b。半导体层204c连接于半导体层102的不由绝缘层203覆盖的部分的上表面。

[0107]

导电层205基本上与导电层105同样地构成。但是,导电层205仅具备与导电层105a对应的导电层205a、与导电层105c对应的导电层205c、及与导电层105d对应的导电层205d,不具备与导电层105b对应的导电层205b。

[0108]

此外,如图20所示,在本实施方式中,导电层205c覆盖杂质区域s

n

的x方向一端部及y方向一端部。由此,在本实施方式中,杂质区域s

n

的角部s

ne

由导电层205c覆盖。

[0109]

[第3实施方式]接下来,参照图22及图23对第3实施方式的存储器裸片进行说明。图22是用来对本实施方式的存储器裸片的构成进行说明的示意性俯视图。用来对本实施方式的存储器裸片的构成进行说明的示意性立体图与图21相同。图23是用来对本实施方式的比较例的存储器裸片的构成进行说明的示意性俯视图。此外,在以下说明中,对与第2实施方式相同的构成要素标注相同符号,并省略说明。

[0110]

本实施方式的存储器裸片基本上与第2实施方式的存储器裸片同样地构成。然而,本实施方式的存储器裸片不具备去耦电容器c

d2

,作为代替,具备去耦电容器c

d3

。本实施方式的去耦电容器c

d3

基本上与第2实施方式的去耦电容器c

d2

同样地构成。但是,本实施方式的去耦电容器c

d3

不具备半导体层204及导电层205,作为代替,具备未图示的半导体层及导电层305。

[0111]

未图示的半导体层基本上与半导体层204同样地构成。也就是说,该半导体层具备与半导体层204a对应的半导体层、与半导体层204c对应的半导体层、及与半导体层204d对应的半导体层。但是,与该半导体层204d对应的部分不覆盖杂质区域s

n

的y方向的一侧端部。因此,在本实施方式中,杂质区域s

n

的角部s

ne

(图22)不由半导体层304覆盖。

[0112]

导电层305基本上与导电层205同样地构成。也就是说,导电层305具备与导电层205a对应的导电层305a、与导电层205c对应的导电层305c、及与导电层205d对应的导电层305d。但是,本实施方式的导电层305c不覆盖杂质区域s

n

的y方向一端部。因此,在本实施方式中,例如如图22所示,杂质区域s

n

的角部s

ne

不由导电层305覆盖。

[0113]

此处,在杂质区域s

n

的角部s

ne

,存在发生电场集中的情况。在这种情况下,如果杂质区域s

n

的角部s

ne

由导电层等覆盖,那么存在该角部附近容易发生绝缘破坏等,导致去耦电容器的寿命变短的情况。因此,在第1实施方式中,使得半导体层104及导电层105不与杂质区域s

n

的角部s

ne

重叠。同样地,在第3实施方式中,使得未图示的半导体层及导电层305不与这种杂质区域s

n

的角部s

ne

重叠。根据这种构成,与第2实施方式相比较,能够提供长寿命的存储器裸片。

[0114]

在第3实施方式的比较例的构成中,如图23所示,未图示的半导体层及导电层305不覆盖杂质区域s

n

的x方向的一侧端部。此处,因为半导体层102是将y方向作为长度方向,所以在未图示的半导体层及导电层305以避开x方向的一侧端部(长边)的方式配置的构成中,存在去耦电容器c

d3

'的电容值相对于去耦电容器c

d3

的电容值相对较小的情况。另外,如第3实施方式,因为未图示的半导体层及导电层305c的y方向长度(图22)小于第2实施方式中的半导体层204c及导电层205c的y方向长度(图20),所以存在电容值相对较小的情况。对此,在第1实施方式中,将连接于半导体层102的半导体层104c配置于半导体层104a、半导体层104b之间。根据这种构成,能够抑制x方向上的电容值减少及y方向上的电容值减少,因此,能够实现长寿命且大电容的去耦电容器c

d

。

[0115]

[第4实施方式]接下来,参照图24对第4实施方式的存储器裸片进行说明。图24是

用来对本实施方式的存储器裸片的构成进行说明的示意性俯视图。此外,在以下说明中,对与第1实施方式相同的构成要素标注相同符号,并省略说明。

[0116]

本实施方式的存储器裸片基本上与第1实施方式的存储器裸片同样地构成。然而,本实施方式的存储器裸片不具备去耦电容器c

d

,作为代替,具备去耦电容器c

d4

。本实施方式的去耦电容器c

d4

基本上与第1实施方式的去耦电容器c

d

同样地构成。然而,本实施方式的去耦电容器c

d4

不具备半导体层104及导电层105,作为代替,具备导电层405及未图示的半导体层。

[0117]

导电层405基本上与导电层105同样地构成。也就是说,导电层405具备与导电层105a对应的导电层405a、与导电层105b对应的导电层405b、与所述导电层105c对应的导电层405c、及与导电层105d对应的导电层405d。但是,本实施方式的导电层405d不沿x方向延伸。

[0118]

设置在绝缘层103与导电层405之间的半导体层基本上与半导体层104同样地构成。但是,该半导体层的平面形状与导电层405同样地形成。

[0119]

[第5实施方式]接下来,参照图25~图28对第5实施方式的存储器裸片进行说明。图25是用来对本实施方式的存储器裸片的构成进行说明的示意性俯视图。图26及图27是用来对本实施方式的存储器裸片的构成进行说明的示意性剖视图。此外,在以下说明中,对与第1实施方式相同的构成要素标注相同符号,并省略说明。

[0120]

本实施方式的存储器裸片基本上与第1实施方式的存储器裸片同样地构成。然而,本实施方式的存储器裸片不具备半导体衬底s,作为代替,具备半导体衬底s5。本实施方式的半导体衬底s5基本上与第1实施方式的半导体衬底s同样地构成。然而,如参照图10所说明,在第1实施方式的半导体衬底s上设置着半导体衬底区域s

s

、及以包围该半导体衬底区域s

s

的方式设置的p阱区域s

pw

,在该半导体衬底区域s

s

设置着6个去耦电容器c

d

。另一方面,如图25所示,在本实施方式的半导体衬底s5上设置着n阱区域s

nw

、及以包围该n阱区域s

nw

的方式设置的p阱区域s

pw

,在该n阱区域s

nw

设置着6个去耦电容器c

d5

。n阱区域s

nw

例如包含磷(p)或砷(as)等n型杂质。另外,在该n阱区域s

nw

设置着沿y方向延伸的杂质区域s

n+

。在该杂质区域设置着沿y方向排列的多个接触电极cs

vccq

。

[0121]

本实施方式的去耦电容器c

d5

基本上与第1实施方式的去耦电容器c

d

同样地构成。然而,如图26及图27所示,6个去耦电容器c

d5

中所包含的6个杂质区域s

n

经由n阱区域s

nw

导通。

[0122]

图28是表示去耦电容器c

d5

、c

d

'的信号频率与电容值的关系的曲线图。此外,图28所示的特性之中,去耦电容器c

d5

的相关特性表示与半导体衬底s5的上表面和半导体层102的下表面之间的电容值相关的模拟结果。另外,图28所示的特性之中,去耦电容器c

d

'的相关特性表示与半导体衬底s的上表面和半导体层102的下表面之间的电容值相关的模拟结果。

[0123]

在信号频率相对较小的情况下,去耦电容器c

d5

、c

d

'的电容值成为相同程度。另一方面,在信号频率相对较大的情况下,去耦电容器c

d5

的电容值大于去耦电容器c

d

'的电容值。其原因在于:通过n阱区域s

nw

降低了半导体衬底s5上表面的电阻率。

[0124]

如上所述,根据本实施方式的这种构成,通过n阱区域s

nw

降低了半导体衬底s5上表面的电阻率,能够更好地抑制伴随信号频率的高速化所造成的电容值的衰减。

[0125]

另外,根据本实施方式的这种构成,通过半导体衬底s5的n阱区域s

nw

与设置在该n阱区域s

nw

下方的半导体衬底区域s

s

之间的耗尽层而产生寄生电容。因此,能够利用该寄生电容来增大去耦电容器c

d5

的电容值。

[0126]

[第6实施方式]接下来,参照图29~图31对第6实施方式的存储器裸片进行说明。图29是用来对本实施方式的存储器裸片的构成进行说明的示意性俯视图。图30及图31是用来对本实施方式的存储器裸片的构成进行说明的示意性剖视图。此外,在以下说明中,对与第5实施方式相同的构成要素标注相同符号,并省略说明。

[0127]

本实施方式的存储器裸片基本上与第5实施方式的存储器裸片同样地构成。然而,本实施方式的存储器裸片不具备半导体衬底s5及去耦电容器c

d5

,作为代替,具备半导体衬底s6及去耦电容器c

d6

。

[0128]

本实施方式的去耦电容器c

d6

基本上与第5实施方式的去耦电容器c

d5

同样地构成。然而,本实施方式的去耦电容器c

d6

具备使半导体衬底s6的上表面露出的多个贯通孔op

cd

。也就是说,去耦电容器c

d6

例如如图30及图31所示,具备绝缘层601来代替绝缘层101。具备半导体层602来代替半导体层102。半导体层602具有区域602a、区域602b、区域602c、区域602d来代替半导体层102所具有的区域102a、区域102b、区域102c、区域102d。具备半导体层604来代替半导体层104。具备半导体层604a、半导体层604b、半导体层604c、半导体层604d来代替半导体层104a、半导体层104b、半导体层104c、半导体层104d。具备导电层605来代替导电层105。具备导电层605a、导电层605b、导电层605c、导电层605d来代替导电层105a、导电层105b、导电层105c、导电层105d。在绝缘层601、半导体层602的区域602c、半导体层604c、及导电层605c上设置着沿y方向排列的多个贯通孔。

[0129]

本实施方式的半导体衬底s6基本上与第5实施方式的半导体衬底s5同样地构成。然而,例如如图30及图31所示,在本实施方式的半导体衬底s6中,在与所述贯通孔op

cd

对应的区域设置着杂质区域s

n+

。另外,在该杂质区域s

n+

分别设置着接触电极cs

vccq

。接触电极cs

vccq

经由配线层mx的配线mx而与电压传输线w

vccq

连接。由此,在更多的位置对n阱区域s

nw

施加电压vccq,因此,n阱区域s

nw

的薄层电阻有效地减少。因此,能够抑制高频区域的有效电容下降。此外,这些接触电极cs

vccq

的至少一部分设置在从z方向观察时与焊垫电极p重叠的位置。

[0130]

[其它]虽对本发明的若干实施方式进行了说明,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些新颖的实施方式能够以其它各种方式实施,且能够在不脱离发明主旨的范围内进行各种省略、替换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书中所记载的发明及其同等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1