包括数据存储结构的半导体装置的制作方法

包括数据存储结构的半导体装置

1.相关申请的交叉引用

2.2019年9月6日提交于韩国知识产权局的题为“包括数据存储结构的半导体装置”的韩国专利申请no.10-2019-0110620整体以引用方式并入本文中。

技术领域

3.示例实施例涉及半导体装置,更具体地,涉及一种包括数据存储结构的半导体装置及其制造方法。

背景技术:

4.为了提高电子产品的价格竞争力,对提高半导体装置的集成密度的需求已增加。为了提高半导体装置的集成密度,已提出了存储器单元三维布置的半导体装置来代替包括二维布置的存储器单元的半导体装置。然而,当存储器单元三维布置时,存储器单元的分布性质可能劣化。

技术实现要素:

5.根据实施例的一方面,一种半导体装置可包括:在衬底上的堆叠结构,该堆叠结构包括沿着第一方向堆叠的交替的栅电极和绝缘层;沿着第一方向穿过堆叠结构的竖直开口,该竖直开口包括沟道结构,该沟道结构具有在竖直开口的内侧壁上的半导体层以及在半导体层上的可变电阻材料,该可变电阻材料中的空位浓度沿其宽度变化,以在更靠近沟道结构的中心而不是更靠近半导体层处具有更高的浓度;以及在衬底上的杂质区域,该半导体层在沟道结构的底部接触该杂质区域。

6.根据实施例的另一方面,一种半导体装置可包括:在衬底上的堆叠结构,该堆叠结构包括沿着第一方向堆叠的交替的栅电极和绝缘层;沿着第一方向穿过堆叠结构的竖直开口,该竖直开口包括沟道结构,该沟道结构具有在竖直开口的内侧壁上的半导体层、在半导体层上的可变电阻材料以及在第一可变电阻材料与半导体层之间的缓冲层,整个缓冲层包括具有含比半导体层的晶粒更小的晶粒的结构的材料;以及在衬底上的杂质区域,该半导体层在沟道结构的底部接触该杂质区域。

7.根据实施例的又一方面,一种半导体装置可包括:在衬底上的堆叠结构,该堆叠结构包括沿着第一方向堆叠的交替的栅电极和绝缘层;沿着第一方向穿过堆叠结构的竖直开口,该竖直开口包括沟道结构,该沟道结构具有在竖直开口的内侧壁上的多晶硅半导体层、在半导体层上的可变电阻材料以及在第一可变电阻材料与半导体层之间的非晶硅缓冲层;以及在衬底上的杂质区域,半导体层在沟道结构的底部接触该杂质区域。

附图说明

8.对于本领域技术人员而言,通过参照附图详细描述示例性实施例,特征将变得显而易见,附图中:

9.图1示出根据示例实施例的半导体装置的平面图;

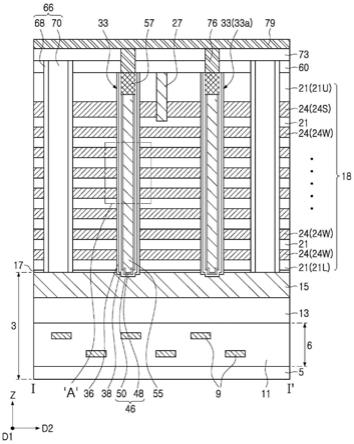

10.图2a示出沿着图1中的线i-i’的截面图;

11.图2b示出图2a中的部分“a”的放大图;

12.图3a和图3b示出根据示例实施例的半导体装置的数据存储结构中的空位浓度的曲线图;

13.图3c示出在设定状态和重置状态下图3a或图3b所示的数据存储结构的空位浓度的改变的概念图;

14.图4a示出根据另一示例实施例的半导体装置的数据存储结构中的空位浓度的曲线图;

15.图4b示出在设定状态和重置状态下图4a所示的数据存储结构的空位浓度的改变的概念图;

16.图5a示出根据示例实施例的半导体装置的数据存储结构的一部分的修改示例的放大截面图;

17.图5b示出根据另一示例实施例的半导体装置的数据存储结构的一部分的另一修改示例的放大截面图;

18.图6a示出根据另一示例实施例的半导体装置的放大图;

19.图6b至图6e示出根据示例实施例的半导体装置的数据存储结构中的空位浓度的曲线图;

20.图6f示出根据另一示例实施例的半导体装置的放大图;

21.图6g示出根据另一示例实施例的半导体装置的放大图;

22.图7a示出根据另一示例实施例的半导体装置的截面图;

23.图7b和图7c分别示出图7a中的部分“b”和部分“c”的放大图;

24.图8示出与图7a的部分“c”对应的半导体装置的修改示例;

25.图9示出与图7a的部分“b”对应的半导体装置的修改示例;

26.图10示出与图7a的部分“b”对应的半导体装置的另一修改示例;

27.图11a示出根据另一示例实施例的半导体装置的截面图;

28.图11b示出根据另一示例实施例的半导体装置的截面图;

29.图12a示出根据另一示例实施例的半导体装置的截面图;

30.图12b示出根据另一示例实施例的半导体装置的截面图;

31.图12c示出根据另一示例实施例的半导体装置的截面图;

32.图12d示出根据另一示例实施例的半导体装置的截面图;

33.图12e示出根据另一示例实施例的半导体装置的截面图;

34.图13、图14a和图15示出根据示例实施例的半导体装置的制造方法中的各阶段的截面图;以及

35.图14b和图14c示出根据示例实施例的数据存储结构的形成方法中的各阶段的示意图。

具体实施方式

36.以下,将参照附图如下描述实施例。

37.在下面的描述中,将参照图1根据示例实施例描述半导体装置。图1是示出根据示例实施例的半导体装置的元件的部分的平面图。

38.参照图1,示例实施例中的半导体装置1可包括堆叠结构18、穿透堆叠结构18的分离结构66、分离结构66之间的竖直结构33以及导线79。分离结构66可在第一方向d1上延伸,并且可在垂直于第一方向d1的第二方向d2上彼此间隔开。导线79可在第二方向d2上延伸,并且可在第一方向d1上彼此间隔开。

39.竖直结构33可设置在堆叠结构18中,例如,竖直结构33穿透堆叠结构18。竖直结构33可包括芯区域55、围绕芯区域55的侧表面的数据存储结构46、围绕数据存储结构46的外侧表面的沟道半导体层38以及围绕沟道半导体层38的外侧表面的栅极介电层36。例如,如图1所示,当在俯视图中看时,数据存储结构46、沟道半导体层38和栅极介电层36中的每一个围绕芯区域55的整个周界。竖直结构33可包括沟道结构。沟道结构可包括栅极介电层36、沟道半导体层38、数据存储结构46和芯区域55。沟道半导体层38可被称为“半导体层”。

40.在示例实施例中,数据存储结构46可包括可变电阻材料。在另一示例实施例中,数据存储结构46可包括相变材料。在下面的描述中,将描述半导体装置1的一个或多个示例实施例。

41.将参照图2a和图2b根据示例实施例描述半导体装置。图2a是示出沿着图1中的线i-i’截取的半导体装置的区域的截面图。图2b是示出图2a中的部分a的放大图。

42.参照图1、图2a和图2b,堆叠结构18可设置在下结构3上。在示例实施例中,下结构3可包括杂质区域15。杂质区域15可由例如具有n型导电性的多晶硅形成。

43.在示例实施例中,下结构3可包括下基底5、设置在下基底5上的外围电路区域6、设置在外围电路区域6上的上基底13以及设置在上基底13上的杂质区域15。下基底5可被实现为由半导体材料(例如,硅)形成的半导体衬底。下基底5可以是单晶硅衬底。外围电路区域6可包括外围引线9和覆盖外围引线9的下绝缘层11。上基底13可包括金属和/或金属硅化物。例如,上基底13可由包括钨和设置在钨上的硅化钨的导电材料层形成。杂质区域15可设置在上基底13上。

44.堆叠结构18可位于杂质区域15上。堆叠结构18可包括交替地层叠的层间绝缘层21和栅极层24。

45.层间绝缘层21可包括最下层间绝缘层21l和最上层间绝缘层21u。在层间绝缘层21和栅极层24当中,最下层可被配置为最下层间绝缘层21l,最上层可被配置为最上层间绝缘层21u。例如,层间绝缘层21可由绝缘材料(例如,氧化硅等)形成。

46.在示例实施例中,栅极层24可被配置为栅电极。因此,在下面的描述中,栅极层24将被称为栅电极。

47.在示例实施例中,下缓冲层17可设置在堆叠结构18和下结构3之间。下缓冲层17可由相对于层间绝缘层21具有蚀刻选择性的材料形成。例如,下缓冲层17可由绝缘材料(例如,氧化铝等)形成。在另一示例实施例中,可不提供下缓冲层17。

48.竖直结构33可设置在穿透堆叠结构18的孔30中。孔30可被称为“竖直开口”或“开口”。孔30可穿透堆叠结构18并且可例如沿着竖直方向z向下延伸,并且可穿透下缓冲层17。孔30可暴露下结构3的一部分(例如,杂质区域15的一部分)。竖直结构33可形成在孔30中以穿透堆叠结构18和下缓冲层17。

49.竖直结构33可包括焊盘图案57以及图1所示的芯区域55、数据存储结构46、沟道半导体层38和栅极介电层36。例如,如图2a所示,焊盘图案57可位于芯区域55和数据存储结构46的顶表面上,而沟道半导体层38和栅极介电层36可沿着数据存储结构46和图案57中的每一个的外表面(例如,整个外表面)延伸(例如,连续地延伸),因此例如,焊盘图案57、沟道半导体层38和栅极介电层36的顶表面可彼此齐平。

50.详细地,芯区域55可被配置为由绝缘材料(例如,氧化硅等)形成的绝缘柱。例如,芯区域55的与焊盘图案57相邻的上部可由氧化硅形成,芯区域55的与焊盘图案57间隔开的下部可由包括空隙的氧化硅形成,或者可由气隙形成。芯区域55可与孔30的侧壁间隔开,芯区域55的上表面可设置在比栅电极24中的最上栅电极高的水平处,芯区域55的下表面可设置在比栅电极24中的最下栅电极低的水平处。

51.沟道半导体层38可覆盖芯区域55的侧表面和下表面。栅极介电层36可被插入在沟道半导体层38的外侧表面与栅电极24之间。在示例实施例中,栅极介电层36可从插入在沟道半导体层38的外侧表面与栅电极24之间的部分延伸到沟道半导体层38的外侧表面与层间绝缘层21之间的空间。

52.数据存储结构46可被插入在芯区域55与沟道半导体层38之间,并且可覆盖芯区域55的侧表面和底表面。例如,如图2a所示,数据存储结构46可沿着芯区域55的整个侧壁和底部连续。

53.焊盘图案57可与芯区域55的上表面接触。在示例实施例中,焊盘图案57可与数据存储结构46的上表面接触。在示例实施例中,焊盘图案57可与沟道半导体层38的横向侧表面的上部接触。在示例实施例中,焊盘图案57可由具有n型导电性的掺杂的硅(例如,多晶硅)形成。

54.栅电极24可包括字线24w以及设置在字线24w上的至少一条选择线24s。绝缘图案27可被安置为将栅电极24的所述至少一条选择线24s在第二方向d2上彼此隔离。绝缘图案27可将所述至少一条选择线24s在第二方向d2上隔离,可在竖直方向z上延伸,并且可穿透最上层间绝缘层21u。在示例实施例中,所述至少一条选择线24s中的每一条的厚度可大于每条字线24w的厚度(例如,在竖直方向z上)。

55.第一上绝缘层60和第二上绝缘层73可依次层叠并设置在堆叠结构18上。分离结构66可穿透第一上绝缘层60和堆叠结构18。分离结构66可具有在第一方向d1上延伸的线形式,如图1所示。

56.在示例实施例中,分离结构66可由绝缘材料形成。在另一示例实施例中,分离结构66可包括绝缘材料和导电材料。例如,每个分离结构66可包括由绝缘材料形成的第一隔离图案68以及由导电材料形成的第二隔离图案70。第一隔离图案68可被插入在第二隔离图案70和堆叠结构18之间。

57.可设置穿透第一上绝缘层60和第二上绝缘层73并电连接到竖直结构33的接触插塞76。接触插塞76可与竖直结构33的焊盘图案57接触并电连接。

58.可设置位于接触插塞76上电连接到接触插塞76的导线79。导线79可被配置为位线。

59.在示例实施例中,数据存储结构46包括沿其宽度具有不均匀的空位浓度的可变电阻材料。例如,数据存储结构46可包括在从沟道半导体层38朝着芯区域55取向的方向上空

位浓度增加的可变电阻材料,例如,空位浓度可在径向方向上随着距芯区域55的外表面的距离减小而增加。例如,如果数据存储结构46中的可变电阻材料将被分离成设置在沟道半导体层38与芯区域55之间(例如,沿着芯区域55的整个周界)的第一部分48(即,第一可变电阻层48)和设置在第一可变电阻层48与芯区域55之间(例如,沿着芯区域55的整个周界)的第二部分50(即,第二可变电阻层50),则第二部分50(更靠近芯区域55的部分)中的空位浓度将高于第一部分48(更远离芯区域55的部分)的空位浓度。以下,为了说明方便,将依据第一部分48和第二部分50(或者可互换地,依据“第一可变电阻层48”和“第二可变电阻层50”)来讨论数据存储结构46中的可变电阻材料,以方便提及沿着竖直结构33的径向方向的不同空位浓度。第一可变电阻层48可被称为第一可变电阻材料层,第二可变电阻层50可被称为第二可变电阻材料层。

60.在示例实施例中,数据存储结构46中的可变电阻材料可包括第一元素和氧。例如,数据存储结构46中的可变电阻材料可包括过渡金属元素和氧,使得所得过渡金属氧化物(例如,氧化铪(hfo))中的氧空位的浓度朝着芯区域55增加。

61.例如,参照图2b,第一可变电阻层48和第二可变电阻层50可共同包括第一元素和氧。例如,第一元素可以是金属元素,例如a1、mg、zr、hf等。例如,第一可变电阻层48和第二可变电阻层50二者可由包括hf和o的hfo材料形成,并且包括在第二可变电阻层50中的hfo材料中的氧空位的浓度可高于包括在第一可变电阻层48中的hfo材料的氧空位的浓度。因此,第一可变电阻层48和第二可变电阻层50可被配置为包括相同元素的材料层。

62.在另一示例中,第一可变电阻层48和第二可变电阻层50中的一个可被配置为包括第一元素和氧的氧化物,第一可变电阻层48和第二可变电阻层50中的另一个可被配置为包括不同于第一元素的第二元素和氧的材料。第一元素和第二元素中的至少一个可以是过渡金属元素。第一可变电阻层48可由包括第一元素的第一材料形成,第二可变电阻层50可由包括不同于第一元素的第二元素的第二材料形成。例如,第一可变电阻层48可由sio

x

、alo

x

、mgo

x

、zro

x

、hfo

x

和sin

x

当中的一种材料形成,第二可变电阻层50可由siox、alo

x

、mgo

x

、zro

x

、hfo

x

和sin

x

当中与第一可变电阻层48的材料不同的材料形成。

63.在示例实施例中,第一可变电阻层48和第二可变电阻层50中的每一个可包括具有开关性质的材料,例如sio

x

、alo

x

、mgo

x

、zro

x

、hfo

x

和sin

x

中的一种。例如,第一可变电阻层48可由hfo

x

形成,第二可变电阻层50可由alo

x

形成。

64.数据存储结构46的面向字线24w的侧表面的区域可被配置为存储数据,并且可被配置为存储器单元。在示例实施例中,通过提供包括第一可变电阻层48和第二可变电阻层50的数据存储结构46,存储器单元的分布性质可改进。

65.详细地,数据存储结构46的面向字线24w的数据存储区域可被编程。例如,编程操作可包括选择字线24w中面向数据存储结构46的可能需要编程的数据存储区域的字线,并取消选择其它字线的操作。字线24w当中的所选字线wla可截止,未选字线wlb1和wlb2可导通。例如,编程操作可包括将0v或负电压施加到所选字线wla的操作、将高于阈值电压(例如,约6v)的正电压施加到未选字线wlb1和wlb2的操作、将约5v至约6v的电压施加到导线79(即,位线)的操作、以及将杂质区域15(即,公共源极线)接地的操作。

66.图2b中的虚线指示当进行上述编程操作时(即,当所选字线wla被选择并截止时)电流100的流动。即,参照图2b,图2b中的电流100可沿着面向设置在所选字线wla上方的第

一未选字线wlb1的沟道半导体层38流动,由于施加偏压所导致的电阻改变而偏移到面向所选字线wla的数据存储结构46中(即,流过与截止的所选字线wla对应的区域中的数据存储结构46),并移回到面向设置在所选字线wla下方的第二未选字线wlb2的沟道半导体层38。

67.在从沟道半导体层38朝着竖直结构33的中心取向的方向上沿着数据存储结构46的宽度的空位浓度增加(例如,与沿着宽度的均匀浓度或在相反方向上变化的浓度相比)允许电流100进一步向数据存储结构46中偏移,例如由于第二可变电阻层50中的电阻相对于第一可变电阻层48较低,流过第二可变电阻层50而非第一可变电阻层48,从而改进电流操作的控制和均匀度。即,向竖直结构33(其包括具有变化的空位浓度的数据存储结构46)施加偏压使空位浓度在与所选栅电极wla对应的区域处的数据存储结构46内沿着竖直方向z更均匀地散布,并例如在所选栅电极wla上方和下方形成两个耗尽区域,使得最外空位与沟道半导体层38之间的竖直距离减小,以便改进通过沟道半导体层38的电流操作的控制和均匀度。

68.如上所述,随着电流沿着面向所选字线wla的数据存储结构46流动,数据存储结构46的电阻改变,并且面向所选字线wla的数据存储结构46的数据存储区域可被配置为处于设定状态。通过执行上述编程操作,数据存储结构46的电阻减小。

69.在示例实施例中,数据存储结构46可形成单级存储器单元。例如,面向所选字线wla的数据存储结构46的数据存储区域可被配置为处于第一电阻状态,并且处于第一电阻状态的数据存储结构46的数据存储区域可形成单级存储器单元。

70.在另一示例实施例中,数据存储结构46的数据存储区域可形成多级存储器单元。例如,根据所应用的编程操作,面向所选字线wla的数据存储结构46的数据存储区域可被配置为处于第一电阻状态,或者可被配置为处于第二电阻状态,在第二电阻状态中,电阻高于第一电阻状态的电阻。因此,当面向所选字线wla的数据存储结构46的数据存储区域被配置为处于不同的电阻状态时,数据存储结构46可形成多级存储器单元。

71.可对如上编程的数据存储结构46的数据存储区域执行擦除操作,并且类似于上述编程操作,擦除操作可包括使所选字线wla截止,使未选字线wlb1和wlb2导通,将擦除电压(即,约5v至约6v的电压)施加到杂质区域15(即,公共源极线),并使导线79(即,位线)接地的操作。因此,电流可在与图2b所示的方向相反的方向上流动,使得磁场可改变,并且面向所选字线wla的数据存储结构46的数据存储区域可被配置为处于重置状态。通过擦除操作,数据存储结构46的数据存储区域的电阻增加。因此,通过执行编程操作而获得的设定状态下的数据存储结构46的数据存储区域的电阻可不同于通过执行擦除操作而获得的重置状态下的电阻。例如,在数据存储结构46的数据存储区域中,设定状态下的电阻可低于重置状态下的电阻。

72.在示例实施例中,数据存储结构46可包括在单级存储器单元中。例如,数据存储结构46的与所选字线wla相对的区域可进入第一电阻状态,并且数据存储结构的处于第一电阻状态的区域可包括在单级存储器单元中。

73.在另一示例中,数据存储结构46可包括在多级单元mlc中。例如,根据所应用的编程操作,数据存储结构46的与所选字线wl相对的区域可处于第一电阻状态或者可处于高于第一电阻状态的第二电阻状态。因此,数据存储结构46的与所选字线wl相对的区域可被配置为处于不同的电阻状态,并且数据存储结构46可包括在多级存储器单元中。

74.在下面的描述中,将参照图3a和图3b描述例如包括第一可变电阻层48和第二可变电阻层50的数据存储结构46中的空位浓度。图3a是示出数据存储结构46中的空位浓度的示例的曲线图。图3b是示出数据存储结构46中的空位浓度的修改示例的曲线图。

75.例如,参照图3a,数据存储结构46可具有以阶梯形式改变的空位浓度。即,在从沟道半导体层38朝着芯区域55取向的方向上沿着数据存储结构46的宽度的空位浓度可沿着阶梯轮廓增加。

76.详细地,例如,第一可变电阻层48(即,数据存储结构46的更靠近沟道半导体层38的部分)可具有第一空位浓度c1,第二可变电阻层50(即,数据存储结构46的更靠近芯区域55的部分)可具有高于第一空位浓度c1的第二空位浓度c2。第一空位浓度c1可在第一可变电阻层48的厚度变化中保持恒定,第二空位浓度c2可在第二可变电阻层50的厚度变化中保持恒定。

77.在另一示例中,参照图3b,数据存储结构46可具有逐渐改变的空位浓度。例如,随着距第二可变电阻层50的距离增加,第一可变电阻层48内的空位浓度可增加。类似地,随着距第一可变电阻层48的距离增加,第二可变电阻层50内的空位浓度可减小。

78.例如,在第一可变电阻层48中,第一可变电阻层48的与沟道半导体层38(图2b中)接触的部分的空位浓度可高于第一可变电阻层48的与第二可变电阻层50接触的部分的空位浓度。在第二可变电阻层50中,第二可变电阻层50的与第一可变电阻层48接触的部分的空位浓度可高于第二可变电阻层50的与芯区域55(图2b中)接触的部分的空位浓度。因此,第二可变电阻层50的空位浓度可高于第一可变电阻层48的空位浓度。

79.在下面的描述中,将参照图3c描述在设定状态和重置状态下数据存储结构46的空位浓度、编程操作的方法以及擦除操作的方法。图3c是示出在数据存储结构46的设定状态和重置状态下数据存储结构46的空位浓度的改变的概念图,其空位浓度如图3a或图3b所示以阶梯形式改变。

80.在图3c中,元素b1a是沟道半导体层38与第一可变电阻层48之间的第一边界面b1a,设定电流从第一边界面b1a开始从沟道半导体层38流到第一可变电阻层48中,元素b2a是第二边界面b2a,设定电流从第二边界面b2a开始从第一可变电阻层48流到第二可变电阻层50中。元素b2b是第三边界面b2b,在第二可变电阻层50中流动的设定电流从第三边界面b2b开始从第二可变电阻层50流到第一可变电阻层48中,元素b1b是第一可变电阻层48和沟道半导体层38之间的第四边界面b1b,流过第一可变电阻层48的电流从第四边界面b1b流到沟道半导体层38中。因此,图3c中的边界b1a、b2a、b2b和b1b的布置方式示意性地反映与图2b中的所选字线wla对应的区域中的电流路径。设定电流可以是通过编程操作生成的电流。

81.参照图3c,在数据存储结构46的被配置为通过编程操作处于设定状态的区域中,可在第一边界面b1a与第二边界面b2a之间的第一可变电阻层48中形成第一长丝(filament)f1a,可在第二边界面b2a与第三边界面b2b之间的第二可变电阻层50中形成第二长丝f2a,并且可在第三边界面b2b与第四边界面b1b之间的第一可变电阻层48中形成第三长丝f3a。第一长丝f1a、第二长丝f2a和第三长丝f3a可彼此连接。因此,可沿着数据存储结构46中相继连接的第一长丝f1a、第二长丝f2a和第三长丝f3a形成电流路径,即,第一长丝至第三长丝反映通过数据存储结构46的实际电流路径。

82.在第一长丝f1a中,第一长丝f1a的与第一边界面b1a相邻的的区域的空位浓度可

高于第一长丝f1a的与第二边界面b2a相邻的区域的空位浓度。在第二长丝f2a中,第二长丝f2a的与第二边界面b2a相邻的区域的空位浓度可高于第二长丝f2a的与第三边界面b2b相邻的区域的空位浓度。在第三长丝f3a中,第三长丝f3a的与第三边界面b2b相邻的区域的空位浓度可高于第三长丝f3a的与第四边界面b1b相邻的区域的空位浓度。

83.在数据存储结构46的被配置为通过擦除操作处于重置状态的区域中,可在第一边界面b1a与第二边界面b2a之间的第一可变电阻层48中形成第一变形长丝f1b,可在第二边界面b2a与第三边界面b2b之间的第二可变电阻层50中形成第二变形长丝f2b,并且可在第三边界面b2b与第四边界面b1b之间形成第三变形长丝f3b。

84.在图3c中,第一长丝至第三长丝f1a、f2a和f3a以及第一变形长丝至第三变形长丝f1b、f2b和f3b的宽度可指示空位浓度。例如,在第一长丝至第三长丝f1a、f2a和f3a以及第一变形长丝至第三变形长丝f1b、f2b和f3b中,具有相对大的宽度的部分可指示空位浓度相对高,具有相对小的宽度的部分可指示空位浓度相对低。

85.第一变形长丝f1b可与第一边界面b1a接触并且可基本上与第二边界面b2a间隔开。与第二长丝f2a相比,第二变形长丝f2b的与第三边界面b2b相邻的区域的空位浓度可减小。第三变形长丝f3b可与第三边界面b2b接触并且可基本上与第四边界面b1b间隔开。因此,在数据存储结构46的处于重置状态的区域中,第一变形长丝f1b可与第二变形长丝f2b断开连接,并且第三变形长丝f3b可与第四边界面b1b断开连接。

86.如上所述,数据存储结构46的处于设定状态的区域可包括彼此连接的第一长丝至第三长丝f1a、f2a和f3a,并且数据存储结构46的处于重置状态的区域可包括第一变形长丝至第三变形长丝f1b、f2b和f3b,第一变形长丝至第三变形长丝f1b、f2b和f3b中的至少一个与另一个断开连接。

87.在下面的描述中,将参照图4a描述在通过沉积工艺形成数据存储结构46之后数据存储结构46中的空位浓度的修改示例。图4a是示出数据存储结构46中的空位浓度的修改示例的曲线图。

88.在修改示例中,根据图4a,数据存储结构46可具有不断改变的空位浓度。例如,在数据存储结构46中,空位浓度可从第一可变电阻层48到第二可变电阻层50逐渐增加。因此,第二可变电阻层50的空位浓度可高于第一可变电阻层48的空位浓度。

89.在下面的描述中,将参照图4b描述在设定状态和重置状态下数据存储结构46的空位浓度。图4b示出在设定状态和重置状态下数据存储结构46的空位浓度的改变。在图4b中,元素b1a、b2a、b2b和b1b分别对应于图3c所示的第一边界面b1a、第二边界面b2a、第三边界面b2b和第四边界面b1b。

90.参照图4b,在数据存储结构46的被配置为通过编程操作处于设定状态的区域中,可在第一边界面b1a与第二边界面b2a之间的第一可变电阻层48中形成第一长丝f1a’,可在第二边界面b2a与第三边界面b2b之间的第二可变电阻层50中形成第二长丝f2,并且可在第三边界面b2b与第四边界面b1b之间的第一可变电阻层48中形成第三长丝f3a’。第一长丝f1a’、第二长丝f2和第三长丝f3a’可彼此连接。因此,可沿着数据存储结构46中相继连接的第一长丝f1a’、第二长丝f2和第三长丝f3a’形成电流路径。

91.在第一长丝f1a’中,第一长丝f1a’的与第一边界面b1a相邻的区域的空位浓度可低于第一长丝f1a’的与第二边界面b2a相邻的区域的空位浓度。在第二长丝f2中,第二长丝

f2的与第二边界面b2a相邻的区域的空位浓度可与第二长丝f2的与第三边界面b2b相邻的区域的空位浓度基本上相同。在第三长丝f3a’中,第三长丝f3a’的与第三边界面b2b相邻的区域的空位浓度可低于第三长丝f3a’的与第四边界面b1b相邻的区域的空位浓度。

92.在数据存储结构46的被配置为通过擦除操作处于重置状态的区域中,可在第一边界面b1a与第二边界面b2a之间的第一可变电阻层48中形成第一变形长丝f1b’,在第二边界面b2a与第三边界面b2b之间的第二可变电阻层50中第二长丝f2可基本上不变形,并且可在第三边界面b2b与第四边界面b1b之间形成第三变形长丝f3b’。

93.在图4b中,第一长丝至第三长丝f1a’、f2和f3a’以及第一变形长丝f1b’和第三变形长丝f3b’的宽度可指示空位浓度。例如,在第一长丝至第三长丝f1a’、f2和f3a’以及第一变形长丝f1b’和第三变形长丝f3b’中,具有相对大的宽度的部分可指示空位浓度相对高,具有相对小的宽度的部分可指示空位浓度相对低。

94.第一变形长丝f1b’可与第一边界面b1a间隔开并断开连接,并且可与第二长丝f2维持连接。第三变形长丝f3b’可与第二长丝f2维持连接并且可与第四边界面b1b间隔开并断开连接。因此,在数据存储结构46的处于重置状态的区域中,第一变形长丝f1b’可与第一边界面b1a断开连接,并且第三变形长丝f3b’可与第四边界面b1b断开连接。

95.返回参照图1、图2a和图2b,第一可变电阻层48和第二可变电阻层50可例如沿着第二方向d2具有相同的厚度,但是其示例实施例不限于此。例如,第一可变电阻层48和第二可变电阻层50可被配置为例如沿着第二方向d2具有不同的厚度。例如,第一可变电阻层48和第二可变电阻层50中的每一个的厚度可为约1nm至约5nm。将参照图5a和图5b描述被配置为具有不同厚度的可变电阻层的示例。图5a和图5b是示出被配置为具有不同厚度的可变电阻层的部分的放大图。

96.在修改示例中,参照图5a,数据存储结构46a可包括第一可变电阻层48a以及厚度小于第一可变电阻层48a的厚度的第二可变电阻层50a。通过将第一可变电阻层48a的厚度配置为大于第二可变电阻层50a的厚度,半导体装置可以相对较低的电流操作,从而降低半导体装置的功耗。在另一修改示例中,参照图5b,数据存储结构46b可包括第一可变电阻层48b以及厚度小于第一可变电阻层48b的厚度的第二可变电阻层50b。通过将第一可变电阻层48b的厚度配置为小于第二可变电阻层50b的厚度,分布性质可改进。

97.在下面的描述中,将参照图6a描述堆叠结构的修改示例。图6a是与图2b所示的部分a对应的放大图。

98.在修改示例中,参照图6a,竖直结构33b可包括数据存储结构46c以及在上述示例实施例中描述的栅极介电层36、沟道半导体层38、芯区域55和焊盘图案57。

99.数据存储结构46c可包括图2a和图2b所示的第一可变电阻层48和第二可变电阻层50。数据存储结构46c还可包括设置在第一可变电阻层48和第二可变电阻层50之间的一个或多个附加可变电阻层52a和52b。一个或多个附加可变电阻层52a和52b的空位浓度可高于第一可变电阻层48的空位浓度并且可低于第二可变电阻层50的空位浓度。

100.在示例实施例中,一个或多个附加可变电阻层52a和52b可以是单个附加可变电阻层。

101.在示例实施例中,可提供多个附加可变电阻层52a和52b,并且多个附加可变电阻层52a和52b可包括第一附加可变电阻层52a和第二附加可变电阻层52b。第一附加可变电阻

层52a可被插入在第二附加可变电阻层52b和第一可变电阻层48之间。

102.第一附加可变电阻层52a的空位浓度可高于第一可变电阻层48的空位浓度。第二附加可变电阻层52b的空位浓度可高于第一附加可变电阻层52a的空位浓度并且可低于第二可变电阻层50的空位浓度。

103.在示例实施例中,第一可变电阻层48可被称为第一层,第一附加可变电阻层52a可被称为第二层,第二附加可变电阻层52b可被称为第三层,第二可变电阻层50可被称为第四层。在示例实施例中,通过提供包括第一层48、第二层52a、第三层52b和第四层52b的数据存储结构46c,分布性质可改进。

104.在示例实施例中,数据存储结构46c可形成单级存储器单元。在示例实施例中,数据存储结构46c可形成多级存储器单元。

105.在下面的描述中,将参照图6b、图6c、图6d和图6e描述数据存储结构46c的空位浓度。图6b、图6c、图6d和图6e是示出数据存储结构46c的空位浓度的一个或多个示例的曲线图。例如,图6a是示出数据存储结构46c中的空位浓度的示例的曲线图。图6b是示出数据存储结构46c中的空位浓度的修改示例的曲线图。图6c是示出数据存储结构46c中的空位浓度的另一修改示例的曲线图。图6d是示出数据存储结构46c中的空位浓度的另一修改示例的曲线图。图6e是示出数据存储结构46c中的空位浓度的另一修改示例的曲线图。

106.参照图6b,与图3a所示的示例实施例类似,数据存储结构46c可具有以阶梯轮廓改变的空位浓度。例如,数据存储结构46c可包括在沟道半导体层38(图6a中)中的芯区域55(图6a中)的方向上依次设置的第一可变电阻层48a、第一附加可变电阻层52a、第二附加可变电阻层52b和第二可变电阻层50。第一附加可变电阻层52a的空位浓度可高于第一可变电阻层48的空位浓度,第二附加可变电阻层52b的空位浓度可高于第一附加可变电阻层52a的空位浓度,第二可变电阻层50的空位浓度可高于第二附加可变电阻层52b的空位浓度。如上所述,当未提供第一附加可变电阻层52a和第二附加可变电阻层52b之一时,第一附加可变电阻层52a和第二附加可变电阻层52b中的另一者的空位浓度可高于第一可变电阻层48的空位浓度并且可低于第二可变电阻层50的空位浓度。

107.在下面的描述中,尽管针对如上所述的未提供第一附加可变电阻层52a和第二附加可变电阻层52b之一的数据存储结构46c进行描述,但可基于对包括第一附加可变电阻层52a和第二附加可变电阻层52b二者的数据存储结构46c的空位浓度的描述来理解未提供第一附加可变电阻层52a和第二附加可变电阻层52b之一的数据存储结构46c的空位浓度。

108.在修改示例实施例中,参照图6c,数据存储结构46c的至少一部分的空位浓度可具有这样的浓度分布,其具有从第一可变电阻层48朝着第二可变电阻层50增加的趋势。例如,第一附加可变电阻层52a和第二附加可变电阻层52b的空位浓度分布可在从第一可变电阻层48朝向第二可变电阻层50的方向上增加。第一可变电阻层48与第一附加可变电阻层52a之间的边界部分的空位浓度的斜率以及第一附加可变电阻层52a与第二附加可变电阻层52b之间的边界部分的空位浓度的斜率可比第一附加可变电阻层52a的中央部分的空位浓度的斜率以及第二附加可变电阻层52b的中央部分的空位浓度的斜率更陡。

109.在修改示例实施例中,参照图6d,类似于图3b所示的示例实施例,数据存储结构46可具有以阶梯轮廓改变的空位浓度。例如,第一可变电阻层48的与沟道半导体层38(图6a中)相邻的部分的空位浓度可高于第一可变电阻层48的与第一附加可变电阻层52a相邻的

部分的空位浓度,第一附加可变电阻层52a的与第一可变电阻层48相邻的部分的空位浓度可高于第一附加可变电阻层52a的与第二附加可变电阻层52b相邻的部分的空位浓度,第二附加可变电阻层52b的与第一附加可变电阻层52a相邻的部分的空位浓度可高于第二附加可变电阻层52b的与第二可变电阻层50相邻的部分的空位浓度,第二可变电阻层50的与第二附加可变电阻层52b接触的部分的空位浓度可高于第二可变电阻层50的与芯区域55(图6a中)接触的部分的空位浓度。

110.在修改示例中,参照图6e,类似于图4a所示的示例实施例,数据存储结构46可具有以恒定斜率改变的空位浓度。

111.在下面的描述中,将参照图6f描述堆叠结构的修改示例。图6f是与图2b所示的部分a对应的放大图。

112.在修改示例中,参照图6f,竖直结构33c可包括介电结构136,而非上述示例实施例中描述的栅极介电层36(图2b中)。因此,竖直结构33c可包括介电结构136以及上述示例实施例中描述的沟道半导体层38、芯区域55、焊盘图案57和数据存储结构46。

113.介电结构136可包括第一介电层136a、数据存储层136b和第二介电层136c。数据存储层136b可以是捕获电荷的电荷捕获层。第一介电层136a可由例如氧化硅或掺杂有氮的氧化硅形成。数据存储层136b可由捕获电荷的材料(例如,氮化硅)形成。第二介电层136c可包括例如氧化硅和高k电介质。

114.介电结构136中的数据存储层136b可用作nand闪存的数据存储区域,并且数据存储结构46可用作可变电阻存储器装置的数据存储区域。由于数据存储区域可设置在沟道半导体层38的两侧,所以数据存储密度可增加。

115.在下面的描述中,将参照图6g描述堆叠结构的修改示例。图6g是与图2b所示的部分a对应的放大图。

116.在修改示例中,参照图6g,竖直结构33d可包括数据存储结构146以及上述示例实施例中描述的栅极介电层36、沟道半导体层38、芯区域55和焊盘图案57。

117.数据存储结构146可包括交替地层叠的多个分离层和多个数据存储层。多个数据存储层中的每一个可包括相变材料。

118.多个数据存储层可包括第一相变材料层148和第二相变材料层150。多个分离层可包括设置在第一相变材料层148和沟道半导体层38之间的第一分离层147以及设置在第一相变材料层148和第二相变材料层150之间的第二分离层149。第一相变材料层148和第二相变材料层150中的每一个的厚度可大于第一分离层147和第二分离层149中的每一个的厚度。

119.多个相变材料层148和150中的每一个可由相变存储器材料形成,例如包括ge、sb和/或te的硫系材料等。另选地,多个相变材料层148和150中的每一个可由包括例如te和se中的至少一种以及例如ge、sb、bi、pb、sn、as、s、si、p、o、n和in中的至少一种的相变存储器材料形成。

120.多个相变材料层148和150可共同包括第一元素,并且第二相变材料层150中的第一元素的浓度可高于包括在第一相变材料层148中的第一元素的浓度。第一元素可以是sb或te。多个分离层147和149可由金属氮化物(例如,tin)等形成。

121.在示例实施例中,通过提供包括多个分离层147和149以及多个相变材料层148和

150的数据存储结构146,分布性质可改进。

122.在下面的描述中,将参照图7a、图7b和图7c描述参照图1描述的竖直结构33的修改示例。图7a是示出沿着图1中的线i-i’截取的区域的截面图,图7b是示出图7a中的部分b的放大图,图7c是示出图7a中的部分c的放大图。

123.参照图7a、图7b和图7c,竖直结构33e可包括数据存储结构46d和缓冲半导体层39以及上述示例实施例中描述的栅极介电层36、沟道半导体层38、芯区域55和焊盘图案57。在示例实施例中,数据存储结构46d可被配置为单个可变电阻层。缓冲半导体层39可被称为缓冲层。

124.缓冲半导体层39可被插入在数据存储结构46d和沟道半导体层38之间。缓冲半导体层39可例如整体由具有晶粒小于沟道半导体层38的结构的材料形成。

125.例如,沟道半导体层38可由多晶硅形成,缓冲半导体层39可由非晶硅形成。在另一示例中,沟道半导体层38可由第一多晶硅形成,缓冲半导体层39可由晶粒小于第一多晶硅的晶粒的第二多晶硅形成。

126.例如,当缓冲半导体层39由具有晶粒小于沟道半导体层38的结构的材料形成时,例如,当缓冲半导体层39由非晶硅形成时,在施加偏压时通过缓冲半导体层39形成的长丝(例如,如先前参照图3c和图4b描述的)可更容易与较小晶粒的晶界对准,从而改进沿着竖直方向z的空位分布的均匀度。换言之,更小的晶粒有助于通过晶界(即,经由长丝)的更笔直的电流路径。

127.在示例实施例中,缓冲半导体层39的厚度可小于沟道半导体层38的厚度。例如,缓冲半导体层39的厚度可为约0.5nm至约2nm,并且沟道半导体层38的厚度可为约2nm至约10nm。

128.焊盘图案57可与沟道半导体层38直接接触。焊盘图案57可与数据存储结构46d的上端和缓冲半导体层39的上端直接接触。在示例实施例中,焊盘图案57的上表面可与沟道半导体层38的上表面共面。

129.在示例实施例中,通过提供包括沟道半导体层38和缓冲半导体层39的竖直结构33e,分布性质可改进。

130.在下面的描述中,将参照图8描述参照图7a和图7c描述的焊盘图案的修改示例。图8是与图7c中的放大部分c对应的放大图。

131.在修改示例中,参照图8,焊盘图案57a可覆盖沟道半导体层38a的上表面。例如,焊盘图案57a可具有覆盖数据存储结构46d的上端和缓冲半导体层39的上端并覆盖沟道半导体层38a的上表面的下表面。

132.在下面的描述中,将参照图9描述参照图7a至图7c描述的数据存储结构的修改示例。图9是与图7b中的放大部分b对应的放大图。

133.在修改示例中,参照图9,竖直结构33f可包括数据存储结构46以及在上述示例实施例中参照图7a至图7c描述的栅极介电层36、沟道半导体层38、缓冲半导体层39、芯区域55和焊盘图案57。

134.数据存储结构46可包括图2a和图2b所示的第一可变电阻层48和第二可变电阻层50。第一可变电阻层48可与缓冲半导体层39接触,并且第二可变电阻层50可与芯区域55接触。

135.在示例实施例中,通过提供包括沟道半导体层38、缓冲半导体层39和数据存储结构46的竖直结构33f,分布性质可改进。

136.在下面的描述中,将参照图10描述参照图9描述的数据存储结构的修改示例。图10是与图9中的放大图对应的放大图。

137.在修改示例中,参照图10,竖直结构33g还可包括界面层41以及图9所示的栅极介电层36、沟道半导体层38、缓冲半导体层39、芯区域55、焊盘图案57(图7a中)和数据存储结构46。

138.在示例实施例中,数据存储结构46可包括参照图2a和图2b描述的第一可变电阻层48和第二可变电阻层50。在另一示例实施例中,数据存储结构46a可被配置为单个可变电阻层。

139.界面层41可由通过将沟道半导体层38的面向芯区域55的表面氧化而形成的沟道半导体层38的氧化物形成。例如,当沟道半导体层38由多晶硅形成时,界面层41可由通过将多晶硅氧化而形成的氧化硅形成。

140.界面层41可被插入在沟道半导体层38和缓冲半导体层39之间。界面层41的厚度可小于数据存储结构46b的厚度。

141.在示例实施例中,通过提供包括沟道半导体层38、界面层41、缓冲半导体层39和数据存储结构46的竖直结构33g,分布性质可改进。

142.在下面的描述中,将参照图11a和图11b描述在上述示例实施例中描述的竖直结构的修改示例。图11a和图11b对应于沿着图1的线i-i’的截面图。

143.在修改示例中,参照图11a,竖直结构33h还可包括设置在焊盘图案57和数据存储结构46之间的屏障层56以及栅极介电层36、沟道半导体层38、芯区域55和焊盘图案57。屏障层56可被插入在焊盘图案57和数据存储结构46之间,并且也可被插入在芯区域55和焊盘图案57之间。在示例实施例中,屏障层56可由绝缘材料(例如,氧化硅)形成。屏障层56可被称为屏障绝缘层。

144.屏障层56可阻挡从焊盘图案57流到数据存储结构46的电流路径。即,屏障层56确保电流路径从焊盘图案57流到沟道半导体层38,然后才流到数据存储结构46(即,没有直接在焊盘图案57与数据存储结构46之间流动),以改进电流流动的控制(经由沟道半导体层38)。因此,包括选择线24s的选择晶体管的开关性质可改进。

145.在另一修改示例中,参照图11b,竖直结构33i可包括焊盘图案157以及上述示例实施例中描述的栅极介电层36、沟道半导体层38、数据存储结构46和芯区域55。

146.焊盘图案157可包括第一焊盘层157a和第二焊盘层157b。第一焊盘层157a可覆盖第二焊盘层157b的下表面和侧表面。第二焊盘层157b可由具有n型导电性的多晶硅形成。第一焊盘层157a的与第二焊盘层157b相邻的第一部分157a_1可由具有n型导电性的多晶硅形成,设置在第二焊盘层157b下方并与数据存储结构46接触的第二部分157a_2可由未掺杂多晶硅形成。第一焊盘层157a的第二部分157a_2可显著减小从焊盘图案157流到数据存储结构46的电流路径,从而改进包括选择线24s的选择晶体管的开关性质。

147.在下面的描述中,将参照图12a至图12e描述参照图2a和图2b描述的半导体装置的一个或多个修改示例。在下面参照图12a至图12e描述的半导体装置的一个或多个修改示例的描述中,将主要描述修改的元素,在修改示例中未描述的图12a至图12e中的元素可基于

上述示例实施例中描述的元素来理解。

148.将参照图12a描述参照图2a和图2b描述的堆叠结构的修改示例。图12a对应于沿着图1中的线i-i’截取的截面图。

149.在修改示例中,参照图12a,下缓冲层17可如上所述设置在下结构3上。堆叠结构118可设置在下缓冲层17上。堆叠结构118可包括交替地层叠的层间绝缘层21和栅电极124。如上所述,层间绝缘层21可包括最下层间绝缘层121l和最上层间绝缘层121u,并且在层间绝缘层21和栅电极124当中,最下层可被配置为最下层间绝缘层121l并且最上层可被配置为最上层间绝缘层121u。

150.可设置与参照图2a描述的分离结构66基本上相同的分离结构66。分离结构66可穿透堆叠结构118和下缓冲层17。

151.可设置穿透堆叠结构118和下缓冲层17的竖直结构33。竖直结构33的截面结构可与参照图2a至图10描述的竖直结构33b、33c、33d、33e、33f和33g之一的截面结构基本上相同。因此,竖直结构33也可由上述示例实施例中描述的竖直结构33b、33c、33d、33e、33f和33g之一代替。

152.每个栅电极124可包括与竖直结构33相邻的第一栅极部分124a以及与分离结构66相邻的第二栅极部分124b。第一栅极部分124a可围绕竖直结构33的侧表面。

153.第一栅极部分124a可由掺杂多晶硅形成,并且第二栅极部分124b可由金属硅化物(例如,wsi、tisi等)、金属氮化物(例如,wn、tin等)和/或金属(例如,w等)形成。

154.由于每个栅电极124包括第二栅极部分124b,所以栅电极124的电特性可改进。因此,可提供具有改进的电特性的半导体装置。

155.在下面的描述中,将参照图12b描述参照图2a和图2b描述的下结构的修改示例。图12b对应于沿着图1中的线i-i’截取的截面图。

156.在修改示例中,参照图12b,下结构113可包括半导体衬底105和设置在半导体衬底105上的杂质区域115。半导体衬底105可被配置为单晶硅衬底。可通过将单晶硅衬底掺杂为n型来形成杂质区域115。因此,杂质区域115可具有n型导电性。

157.将参照图12c根据示例实施例描述半导体装置的修改示例。图12c是示出半导体装置的修改示例的截面图。

158.参照图12c,可设置第一芯片区域203以及设置在第一芯片区域203上的第二芯片区域503。第一芯片区域203可包括基底衬底205以及设置在基底衬底205上的外围电路结构207。外围电路结构207可包括外围电路中所包括的外围晶体管ptr和外围引线209、覆盖外围晶体管ptr和外围引线209的基底绝缘层211、以及设置在基底绝缘层211中并电连接到外围引线209的基底接合焊盘214。外围晶体管ptr可包括外围栅极pg和外围源极/漏极psd。基底接合焊盘214和基底绝缘层211可具有彼此共面的上表面。基底接合焊盘214和外围引线209可通过基底插塞212彼此电连接。

159.第二芯片区域503可包括依次堆叠的多个堆叠结构318和418和多个竖直结构333和433。多个堆叠结构318和418中的每一个可与图2a所示的堆叠结构18基本上相同。例如,多个堆叠结构318和418可包括第一堆叠结构318以及设置在第一堆叠结构318上的第二堆叠结构418。第一堆叠结构318可包括交替地堆叠的第一层间绝缘层321和多个第一栅电极324。第二堆叠结构418可包括交替地堆叠的第二层间绝缘层421和多个第二栅电极424。

160.第二芯片区域503可包括设置在第一堆叠结构318和第一芯片区域203之间的第一导电结构379、设置在第一堆叠结构318和第二堆叠结构418之间的第二导电结构500以及设置在第二堆叠结构418上的第三导电结构410。

161.第一导电结构379可由金属材料(例如,钨、铜等)形成。第二导电结构500可包括与第一堆叠结构318相邻的第一导电层315以及与第二堆叠结构418相邻的第二导电层479。第三导电结构410可包括与第二堆叠结构418相邻的第三导电层415以及设置在第三导电层415上的第四导电层413。第一导电层315和第三导电层415可由具有n型导电性的多晶硅形成。第二导电层479和第四导电层413可由金属材料(例如,钨和/或硅化钨等)形成。

162.第二芯片区域503还可包括设置在第三导电结构410上的绝缘层411。第二芯片区域503还可包括在第一芯片区域203和第一导电结构379之间与第一芯片区域203的基底绝缘层211接触和组合的接触绝缘层382、设置在接触绝缘层382中并与基底接合焊盘214接触和组合的芯片接合焊盘390、以及设置在接触绝缘层382中并将芯片接合焊盘390和第一导电结构379电连接的过孔385。

163.第二芯片区域503还可包括设置在第一堆叠结构318和第一导电结构379之间的第一上绝缘层360、设置在第一上绝缘层360和第一导电结构379之间的第二上绝缘层370、以及设置在第一堆叠结构318和第二导电结构500之间的第一缓冲层317。

164.第二芯片区域503还可包括设置在第二堆叠结构418和第二导电结构500之间的第三上绝缘层460、设置在第三上绝缘层460和第二导电结构500之间的第四上绝缘层470、以及设置在第二堆叠结构418和第三导电结构410之间的第二缓冲层417。

165.多个竖直结构333和433可包括第一竖直结构333和第二竖直结构433,第一竖直结构333穿透第一堆叠结构318和第一缓冲层317并电连接到第二导电结构500,第二竖直结构433穿透第二堆叠结构418和第二缓冲层417并电连接到第三导电结构410。

166.多个竖直结构333和433中的每一个可具有与参照图1至图11b描述的竖直结构33之一的结构相同的结构。例如,当包括第二芯片区域503的半导体装置旋转180度时,第二芯片区域503中的第一竖直结构333和第二竖直结构433中的每一个可具有与图2a所示的竖直结构33的结构相同的结构。例如,第一竖直结构333和第二竖直结构433中的每一个可包括分别与栅极介电层36(图2a中)、沟道半导体层38(图2a中)、数据存储结构46(图2a中)、芯区域55(图2a中)和焊盘图案57(图2a中)对应的栅极介电层336和436、沟道半导体层338和438、数据存储结构346和446、芯区域355和455以及焊盘图案357和457。

167.第一竖直结构333的焊盘图案357可通过穿透第一上绝缘层360和第二上绝缘层370的接触插塞376电连接到第一导电结构379。第一竖直结构333的焊盘图案357可由具有n型导电性的多晶硅形成。

168.第一竖直结构333的沟道半导体层338可电连接到第二导电结构500的第一导电层315,并且第二竖直结构433的焊盘图案457可通过穿透第三上绝缘层460和第四上绝缘层470的接触插塞476电连接到第二导电结构500的第二导电层479e。可提供多个第二导电结构500。

169.第二竖直结构433的沟道半导体层438可电连接到第三导电结构410的第三导电层415。

170.第一导电结构379可被配置为第一公共源极线,第二导电结构500可被配置为位

线,第三导电结构410可被配置为第二公共线。因此,第二导电结构500(位线)可设置在第一竖直结构333和第二竖直结构433之间。通过在竖直方向上设置第一竖直结构333和第二竖直结构433,并且在第一竖直结构333和第二竖直结构433之间设置第二导电结构500(位线),半导体装置的集成密度可改进。

171.参照图12d,将描述半导体装置的修改示例。图12d是示出半导体装置的修改示例的截面图。

172.参照图1和图12d,可提供图2a所示的下结构3。在另一示例中,下结构3可由半导体衬底代替。

173.水平结构614可设置在下结构3上。水平结构614可包括第一水平图案610和在第一水平图案610上的第二水平图案612。

174.在示例实施例中,水平结构614可由多晶硅形成。例如,第一水平图案610和第二水平图案612中的每一个可由多晶硅形成。

175.在示例实施例中,第一水平图案610和第二水平图案612中的至少一个可由具有n型导电性的多晶硅形成。例如,第一水平图案610和第二水平图案612可由具有n型导电性的多晶硅形成。

176.堆叠结构618可设置在水平结构614上。堆叠结构618可包括第一组618a和在第一组618a上的第二组618b。

177.第一组618a可包括交替地层叠的第一层间绝缘层621a和第一栅极层624a。第一层间绝缘层621a和第一栅极层624a中的最下层可以是最下第一层间绝缘层,最上层可以是最上第一层间绝缘层。

178.第二组618b可包括第二层间绝缘层621b和第二栅极层624b。第二层间绝缘层621b和第二栅极层624b中的最下层可以是最下第二层间绝缘层,最上层可以是最上第二层间绝缘层。可设置与图2a中基本上相同的绝缘图案27。例如,绝缘图案27可穿透第二栅极层624b当中用作选择线的第二栅极层。

179.可设置穿透堆叠结构618的竖直结构633。每个竖直结构633可包括穿透堆叠结构618的第一组618a的下部633a以及在下部633a上穿透堆叠结构618的第二组618b的上部633b。在示例实施例中,下部633a的与上部633b相邻的上区域的宽度可大于上部633b的与下部633a相邻的下区域的宽度。

180.每个竖直结构633可包括栅极介电层636、芯区域655、数据存储结构646、沟道半导体层638和焊盘图案657。

181.芯区域655可在垂直于下结构3的上表面的竖直方向z上延伸,并且可至少穿透第一栅极层624a和第二栅极层624b。焊盘图案657可设置在芯区域655上。沟道半导体层638可覆盖芯区域655的下表面和侧表面,并且可延伸到焊盘图案657的侧表面。沟道半导体层638可与焊盘图案657直接接触。数据存储结构646可被插入在沟道半导体层638和芯区域655之间,并且可设置在焊盘图案657下方。数据存储结构646可包括具有不同空位浓度的第一可变电阻层648和第二可变电阻层650。栅极介电层636可围绕沟道半导体层638的外侧表面。此外,栅极介电层636可覆盖沟道半导体层638的底表面。

182.水平结构614的至少一部分可穿透栅极介电层636并且可与沟道半导体层638接触。例如,水平结构614的第一水平图案610可穿透栅极介电层636并且可与沟道半导体层

638接触。

183.在竖直结构633中,沟道半导体层638、数据存储结构646和芯区域655可分别对应于沟道半导体层38(图2a和图2b中)、数据存储结构46(图2a和图2b中)和芯区域55(图2a和图2b中)。然而,其示例实施例不限于此,竖直结构633可如参照图5a至图11b描述的示例实施例中那样修改。例如,每个竖直结构633可包括参照图6a描述的第一附加可变电阻层52a和第二附加可变电阻层52b(图6a中)。作为另一示例,每个竖直结构633还可包括参照图7a至图9描述的缓冲半导体层39(图7a至图9中)。在这种情况下,在每个竖直结构633中,上述示例实施例中描述的缓冲半导体层39(图7a至图9中)可被插入在沟道半导体层638和数据存储结构646之间。作为另一示例,每个竖直结构633还可包括参照图10描述的缓冲半导体层39(图10中)和界面层41(图10中)。作为另一示例,每个竖直结构633还可包括参照图11a描述的屏障层56(图11a中)。

184.在下面的描述中,将参照图12e描述半导体装置的修改示例。图12e是示出半导体装置的修改示例的截面图。

185.参照图1和图12e,堆叠结构718可设置在下结构703上。下结构703可以是图2a所示的下结构3(图2a中)。堆叠结构718可包括第一组718a和在第一组718a上的第二组718b。第一组718a可包括交替地层叠的第一层间绝缘层721a和第一栅极层724a。第一层间绝缘层721a和第一栅极层724a中的最下层可以是最下第一层间绝缘层,最上层可以是最上第一层间绝缘层。第二组718b可包括交替地层叠的第二层间绝缘层721b和第二栅极层724b。第二层间绝缘层721b和第二栅极层724b中的最下层可以是最下第二层间绝缘层,最上层可以是最上第二层间绝缘层。可设置与图2b中基本上相同的绝缘图案27。例如,绝缘图案27可穿透第二栅极层724b当中用作选择线的第二栅极层。

186.可设置穿透堆叠结构718的竖直结构733。每个竖直结构733可包括穿透堆叠结构718的第一组718a的下部733a以及在下部733a上穿透堆叠结构718的第二组718b的上部733b。

187.在示例实施例中,下部733a的与上部733b相邻的上区域的宽度可大于上部733b的与下部733a相邻的下区域的宽度。

188.竖直结构733的下部733a可包括半导体图案716、设置在半导体图案716上的第一栅极介电层736a、第一芯区域755a、第一数据存储结构746a、第一沟道半导体层738a和第一焊盘图案757a。

189.在竖直结构733的下部733a中,半导体图案716可穿透第一栅极层724a中的最下第一栅极层,第一芯区域755a可在半导体图案716上在竖直方向z上延伸并且可穿透第一栅极层724a的其它第一栅极层,第一焊盘图案757a可设置在第一芯区域755a上,第一沟道半导体层738a可覆盖第一芯区域755a的下表面和侧表面并且可延伸到第一焊盘图案757a的侧表面,第一数据存储结构746a可被插入在第一沟道半导体层738a和第一芯区域755a之间并且可设置在第一焊盘图案757a下方,第一栅极介电层736a可围绕第一沟道半导体层738a的外侧表面。第一数据存储结构746a可包括具有不同空位浓度的第一可变电阻层748和第二可变电阻层750。

190.在示例中,半导体图案716可以是从衬底703外延生长的外延硅层。

191.在示例中,下栅极介电层717可设置在第一栅极层724a中的最下第一栅极层与半

导体图案716之间。

192.在示例中,第一沟道半导体层738a可与半导体图案716接触。

193.在另一示例中,可不提供半导体图案716。当未提供半导体图案716时,第一沟道半导体层738a可向下延伸并且可与衬底703接触。

194.在竖直结构733的上部733b中,第二芯区域755b可在第一焊盘图案757a上在竖直方向z上延伸并且可穿透第二栅极层724b,第二焊盘图案757b可设置在第二芯区域755b上,第二沟道半导体层738b可覆盖第二芯区域755b的下表面和侧表面并且可延伸到第二焊盘图案757b的侧表面,第二数据存储结构746b可被插入在第二沟道半导体层738b和第二芯区域755b之间并且可设置在第二焊盘图案757b下方,第二栅极介电层736b可围绕第二沟道半导体层738b的外侧表面。第二数据存储结构746b可由与第一数据存储结构746a的材料相同的材料形成。

195.在竖直结构733中,第一沟道半导体层738a和第二沟道半导体层738b、第一数据存储结构746a和第二数据存储结构746b以及第一芯区域755a和第二芯区域755b可分别对应于参照图2a和图2b描述的沟道半导体层38(图2a和图2b中)、数据存储结构46(图2a和图2b中)和芯区域55(图2a和图2b中)。然而,其示例实施例不限于此,竖直结构733的下部733a和上部733b中的每一个可如参照图5a至图11b描述的上述示例实施例中那样修改。

196.在下面的描述中,将参照图13至图15根据示例实施例描述制造半导体装置的方法。图13、图14a和图15是示出沿着图1中的线i-i’截取的区域的截面图。图14b和图14c是根据示例实施例的数据存储结构46的形成方法中的各阶段的示意图。

197.参照图1至图13,可在下结构3上依次形成下缓冲层17和堆叠结构18。形成下结构3可包括:在下基底5上形成外围电路区域6,然后在外围电路区域6上依次形成上基底13和杂质区域15。外围电路区域6可包括外围引线9和覆盖(例如,嵌入)外围引线9的下绝缘层11。下基底5可被实现为单晶硅衬底,上基底13可由例如金属、金属硅化物或多晶硅形成。

198.在另一示例实施例中,形成下结构3可包括例如直接在半导体衬底105(图12b中)上形成杂质区域115(图12b中),如图12b所示。

199.形成堆叠结构18可包括交替地且重复地形成层间绝缘层21和栅电极24。层间绝缘层21可包括最下层间绝缘层21l和最上层间绝缘层21u。在层间绝缘层21和栅电极24当中,最下层可被配置为最下层间绝缘层21l,最上层可被配置为最上层间绝缘层21u。可形成绝缘图案27,其穿透最上层间绝缘层21u并向下延伸,并且穿透栅电极24中的上栅电极24(例如,至少一条选择线24s)。绝缘图案27可由例如氧化硅形成。

200.可形成穿透堆叠结构18和下缓冲层17的孔30。形成孔30可包括:通过蚀刻堆叠结构18来暴露下缓冲层17,并且通过蚀刻下缓冲层17来暴露下结构3。

201.参照图1至图14a,可在孔30中形成竖直结构33。竖直结构33可形成为参照图2a至图11b描述的竖直结构33至33i之一。例如,竖直结构33可如参照图2a和图2b所述形成。例如,形成竖直结构33可包括:在孔30的侧壁上形成栅极介电层36,在孔30中形成覆盖栅极介电层36并与杂质区域15接触的沟道半导体层38,在孔30中形成覆盖沟道半导体层38的数据存储结构46,形成填充孔30的一部分的芯区域55,并且在芯区域55的顶部形成焊盘图案57以完全填充孔30。

202.形成数据存储结构46可包括依次形成参照图2a和图2b描述的第一可变电阻层48

和第二可变电阻层50。即,下面将参照图14b和图14c描述数据存储结构46的可变电阻材料的形成的示例。

203.例如,参照图14b,可例如经由原子层沉积(ald)在沟道半导体层38上沉积第一过渡金属(例如,hf)以形成第一过渡金属层44,然后例如经由ald在沉积的第一过渡金属层44上沉积氧和附加气体(例如,氢气或氮气)的混合物以形成混合物层47a。第一过渡金属层44和混合物层47a的沉积可重复多次,例如,可执行至少三次ald循环以沉积与三个混合物层47a交替的总共至少三个过渡金属层44。如图14b所示,在各个沉积循环期间可相对于氧的量增加附加气体(例如,氢气)的量,使得附加气体(例如,氢气)的量可在各个附加沉积的混合物层47a中逐渐增加。例如,参照图14b,在第一沉积循环中,沉积的混合物中的氧的量可大于氢的量,而在最后沉积循环中,沉积的混合物中的氢的量可大于氧的量。

204.一旦沉积了第一过渡金属层44和混合物层47a,对第一过渡金属层44和混合物层47a进行处理以去除附加气体,使得形成(例如,保留)空位45来替代附加气体的被去除的原子。由于在各个沉积循环中附加气体的量增加,所以随着距沟道半导体层38的距离增加,在处理之后所得空位的量也随着距沟道半导体层38的距离增加而增加。因此,随着距沟道半导体层38的距离增加而增加的空位浓度的增加是指在去除附加气体的原子之后所得材料中的空位的量增加。

205.例如,如果附加气体是氢,则用氯处理第一过渡金属层44和混合物层47a以从混合物层47a去除氢原子,使得空位代替去除的氢原子。然后,对具有空位的所得混合物层47a’加热以在沟道半导体层38上形成数据存储结构46,使得沿着从沟道半导体层38朝着竖直结构33(图14a中)的中心取向的方向空位浓度增加。对具有空位的混合物层47a’加热可包括例如在约650℃下退火约360秒或在约1100℃下退火约1秒。

206.在另一示例中,如果附加气体是氮,则可对第一过渡金属层44和混合物层47a进行化学处理(例如,用磷酸),以从混合物层47a去除氮原子并在沟道半导体层38上形成空位浓度沿着从沟道半导体层38朝着竖直结构33(图14a中)的中心取向的方向增加的数据存储结构46。

207.例如,可通过调节混合物层47a中的附加气体的量来调节数据存储结构46中的空位浓度。例如,可控制各个过渡金属层44和混合物层47a的沉积时间以调节空位浓度分布,例如,可控制循环长度以具有恒定轮廓(各个层或多个层的阶梯轮廓)或者逐渐增加的轮廓(非常短的循环,以及提供逐渐增加的浓度曲线图的增加的浓度)。

208.在另一示例中,参照图14c,可例如经由原子层沉积(ald)在沟道半导体层38上沉积第一过渡金属氧化物(例如,hfo)以形成第一过渡金属氧化物层44’,随后例如经由ald沉积非晶硅层47b。然后,对所得结构加热,使得氧原子从第一过渡金属氧化物层44’转移到非晶硅层47b中。从第一过渡金属氧化物层44’去除的氧原子在第一过渡金属氧化物层44’中形成空位,同时非晶硅层47b转变为氧化硅47b’。例如经由氢氟酸去除(例如,完全蚀刻掉)氧化硅47b’以暴露具有空位的第一过渡金属氧化物层,使得所得暴露的具有空位的第一过渡金属氧化物层在沟道半导体层38上限定数据存储结构46。例如,可执行多个循环以逐渐增加空位浓度(例如,沉积、加热和去除的重复循环)。

209.参照图1和图15,可形成覆盖竖直结构33和堆叠结构18的第一上绝缘层60。可形成穿透第一上绝缘层60、堆叠结构18和下缓冲层17的隔离沟槽63。

210.在另一示例实施例中,为了形成参照图12a描述的栅电极124(图12a中),可形成穿透堆叠结构18的隔离沟槽63,可通过部分地蚀刻通过隔离沟槽63暴露的栅电极24来形成凹陷,可用金属材料填充凹陷,并且可通过蚀刻下缓冲层17来暴露下结构3。部分蚀刻的栅电极24可被定义为第一栅极部分124a(图12a中),并且填充凹陷的金属材料可被定义为第二栅极部分124b(图12a中)。

211.参照图1、图2a和图2b,可形成填充隔离沟槽63的分离结构66。在示例实施例中,形成分离结构66可包括:形成覆盖隔离沟槽63的侧壁的第一隔离图案68,并且形成填充各个隔离沟槽63的第二隔离图案70。第一隔离图案68可被插入在第二隔离图案70和堆叠结构18之间。第一隔离图案68可由绝缘材料形成,并且第二隔离图案70可由导电材料形成。在另一示例实施例中,分离结构66可由绝缘材料形成。

212.可在分离结构66和第一上绝缘层60上形成第二上绝缘层73。可形成穿透第一上绝缘层60和第二上绝缘层73并电连接到竖直结构33的接触插塞76。可形成在接触插塞76上电连接到接触插塞76的导线79。

213.根据上述示例实施例,可提供一种包括具有改进的分布性质的存储器单元的半导体装置。

214.本文公开了示例实施例,尽管采用了特定术语,但其仅在一般性和描述性意义上使用和解释,而非为了限制。在一些情况下,如自提交本申请起对本领域普通技术人员而言将显而易见的,除非另外具体地指示,否则结合特定实施例描述的特征、特性和/或元件可单独使用,或与结合其它实施例描述的特征、特性和/或元件组合使用。因此,本领域技术人员将理解,在不脱离所附权利要求中阐述的本发明的精神和范围的情况下,可进行各种形式和细节上的改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1