台面型铟镓砷探测器芯片及其制备方法与流程

[0001]

本发明涉及红外探测器领域,特别涉及一种台面型铟镓砷探测器芯片及其制备方法。

背景技术:

[0002]

短波红外铟镓砷探测器具有高探测率、高量子效率、近室温工作等优异性能,随着铟组分增加时,延伸波长铟镓砷探测器的截止波长可以从1.7μm延伸到2.5μm,在环境监测、光谱学、夜视等方面有着广泛应用价值。

[0003]

随着短波红外成像技术向高分辨率发展的需求,延伸波长铟镓砷焦平面探测器向大规模、小像元、高灵敏度的方向发展,对于1280

×

1024元及更大规模的面阵器件,为了保证光敏芯片与读出电路的倒焊连通率,需要开发高性能的大规模、小像元、高深宽比的延伸波长铟镓砷焦平面探测器的制备工艺方法。

[0004]

目前,在现有的台面型铟镓砷焦平面探测器芯片的制备工艺过程中,氮化硅钝化膜的制备方法主要有感应耦合等离子体化学气相沉淀积法(icp cvd)和等离子体增强化学气相沉积法(pecvd)。

[0005]

其中,icp cvd设备复杂且成本昂贵。pecvd设备简单成本低,在产业当中被广泛用于淀积介质膜。pecvd工艺中通常以sih4和nh3为反应气体,13.56mhz为射频频率,能制备出较致密的si3n4薄膜,但是由于反应气体都含有大量的h,衬底加热温度又受限制,导致si3n4薄膜中含有较多的h,使得si3n4薄膜中无足够密度的n与in

x

al

1-x

as表面处的in、al悬挂键结合以发挥好的钝化效果,而且nh3是腐蚀性的有毒气体,不利于管理,所以采用sih4和n2作反应气体有重要的意义。

[0006]

然而,反应气体n2的n≡n键的键能为942kj/mol,远大于n-h键的键能391.5kj/mol,采用通用的13.56mhz射频频率产生的等离子场n的密度过小,难以获得致密的si3n4薄膜。

[0007]

因此,目前亟需研究如何增加等离子体场中电子的能量以得到大量的激发态的n原子,从而获得致密的、低应力的si3n4薄膜,同时不会造成轰击到外延材料上的离子能量过大给材料表面带来大的损伤。

技术实现要素:

[0008]

本发明要解决的技术问题是为了克服现有技术中台面型面阵探测器芯片产业化中存在的工艺缺陷,提供一种台面型铟镓砷探测器芯片及其制备方法。

[0009]

本发明是通过下述技术方案来解决上述技术问题:

[0010]

一种台面型铟镓砷探测器芯片的制备方法,包括氮化硅钝化膜的生长步骤;

[0011]

所述氮化硅钝化膜的生长步骤包括:

[0012]

在铟镓砷外延片上采用pecvd法生长两叠层的氮化硅钝化膜,其中,底层氮化硅钝化膜包括致密结构的呈压应力的si3n4膜,底层氮化硅钝化膜的厚度范围为100nm~200nm,

顶层氮化硅钝化膜包括疏松结构的呈拉应力的sin

x

膜,所述顶层氮化硅钝化膜的厚度范围为200nm~400nm。

[0013]

可选地,所述底层氮化硅钝化膜的生长条件包括:

[0014]

采用脉冲射频作为激励电源,射频电源功率的范围为55w~65w,射频频率的设定范围为95khz~105khz,脉冲信号占空比的范围为20%~50%,衬底的温度范围为310℃~330℃,采用的工艺气体包括sih4及n2,其中sih4:n2的范围为1:198~1:202,压强的范围为400mtorr~800mtorr。

[0015]

可选地,所述顶层氮化硅钝化膜的生长条件包括:

[0016]

采用13.5mhz~13.6mhz射频作为激励电源,射频电源功率的范围为35w~45w,衬底的温度范围为310℃~330℃,采用的工艺气体包括sih4及n2,其中sih4:n2的范围为1:198~1:202,压强的范围为400mtorr~800mtorr。

[0017]

可选地,所述氮化硅钝化膜的生长步骤之前,所述制备方法还包括:

[0018]

在铟镓砷外延片上沉积氮化硅掩膜;

[0019]

刻蚀氮化硅和刻蚀铟镓砷外延片形成台面;

[0020]

去除氮化硅掩膜;

[0021]

在铟镓砷外延片上开设n槽;

[0022]

生长p电极;

[0023]

进行热退火。

[0024]

可选地,所述在铟镓砷外延片上沉积氮化硅掩膜的步骤包括:

[0025]

在铟镓砷外延片上采用pecvd法沉积厚度范围为380nm~420nm的氮化硅,以形成氮化硅掩膜,其中,射频功率的范围为35w~45w,衬底的温度范围为310℃~330℃,采用的工艺气体包括sih4及n2,其中sih4:n2的范围为1:16~1:20;和/或,

[0026]

所述刻蚀氮化硅和刻蚀铟镓砷外延片形成台面的步骤包括:

[0027]

采用icp刻蚀技术刻蚀氮化硅,其中,刻蚀条件包括:icp功率范围为1995w~2005w,射频功率的范围为35w~45w,刻蚀气体包括sf6;采用icp刻蚀技术刻蚀铟镓砷外延片形成台面,其中,刻蚀条件包括:icp功率范围为345w~355w,射频功率的范围为125w~135w,刻蚀气体包括cl2和n2;和/或,

[0028]

所述去除氮化硅掩膜的步骤包括:

[0029]

采用氢氟酸缓冲液在室温下腐蚀115s~125s,腐蚀液体积比包括hf:nh4f:h2o为3:6:10;和/或,

[0030]

所述在铟镓砷外延片上开设n槽的步骤包括:

[0031]

用酒石酸溶液腐蚀铟镓砷层,腐蚀液体积比为重量比酒石酸溶液:h2o为1:1,腐蚀速率为0.45μm/min~0.55μm/min;和/或,

[0032]

所述生长p电极的步骤包括:

[0033]

采用电子束蒸发工艺淀积厚度为20nm

±

5nm/30nm

±

5nm/20nm

±

5nm的ti/pt/au;和/或,

[0034]

所述热退火的条件包括:

[0035]

氮气保护气氛,退火温度范围为415℃~425℃,温度保持时间范围为35s~45s。

[0036]

可选地,所述氮化硅钝化膜的生长步骤之后,所述制备方法还包括:

[0037]

在铟镓砷外延片上开设p、n电极孔。

[0038]

可选地,所述在铟镓砷外延片上开设p、n电极孔的步骤之后,所述制备方法还包括:

[0039]

在铟镓砷外延片上生长加厚电极。

[0040]

可选地,所述在铟镓砷外延片上生长加厚电极的步骤包括:

[0041]

采用离子束溅射工艺依次淀积厚度范围为15nm~25nm的cr和厚度范围为380nm~420nm的au。

[0042]

可选地,所述在铟镓砷外延片上生长加厚电极的步骤之后,所述制备方法还包括:

[0043]

进行划片。

[0044]

一种台面型铟镓砷探测器芯片,所述台面型铟镓砷探测器芯片利用如上述的制备方法制备。

[0045]

在符合本领域常识的基础上,所述各优选条件,可任意组合,即得本发明各较佳实施例。

[0046]

本发明的积极进步效果在于:

[0047]

本发明提供的台面型铟镓砷探测器芯片及其制备方法,采用低应力、致密的氮化硅薄膜钝化方式,有效地控制了台面型铟镓砷面阵探测器芯片的翘曲度;外延材料的表面和侧面处的in和al悬挂键得到充分的化学钝化,从而有效地提升了钝化效果;氮化硅钝化膜生长过程中未对外延材料的表面和侧面附近造成大的损伤,从而使得探测器的表面和侧面暗电流得到抑制。

附图说明

[0048]

在结合以下附图阅读本公开的实施例的详细描述之后,能够更好地理解本发明的所述特征和优点。在附图中,各组件不一定是按比例绘制,并且具有类似的相关特性或特征的组件可能具有相同或相近的附图标记。

[0049]

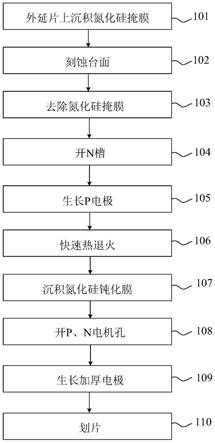

图1为根据本发明的一实施例的台面型铟镓砷探测器芯片的制备方法的流程示意图。

[0050]

图2为根据本发明的一实施例的台面型铟镓砷探测器芯片的剖面结构示意图。

具体实施方式

[0051]

下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

[0052]

为了克服目前存在的上述缺陷,本实施例提供一种台面型铟镓砷探测器芯片的制备方法,所述制备方法包括氮化硅钝化膜的生长步骤;所述氮化硅钝化膜的生长步骤包括:在铟镓砷外延片上采用pecvd法生长两叠层的氮化硅钝化膜,其中,底层氮化硅钝化膜包括致密结构的呈压应力的si3n4膜,底层氮化硅钝化膜的厚度范围为100nm~200nm,顶层氮化硅钝化膜包括疏松结构的呈拉应力的sin

x

膜,所述顶层氮化硅钝化膜的厚度范围为200nm~400nm。

[0053]

在本实施例中,具体提供一种低应力、低损伤钝化的台面型铟镓砷探测器的制备方法,所述制备方法主要适用于制备大面阵、小像元、高深宽比、高灵敏度、高可靠性的台面

型铟镓砷探测器。当然,所述制备方法也适用于其他材料的台面型红外探测器,其工艺步骤类似,具体可根据实际需求进行相应的选择及调整。

[0054]

在本实施例中,所用的外延片为采用分子束外延技术的外延片。

[0055]

在本实施例中,区别于现有的采用昂贵、复杂的电感耦合等离子体化学气相沉积设备来实现低损伤钝化膜的制备,本实施例采用了成本低、简单的等离子体增强化学气相沉积设备,从而有效地节省了成本。

[0056]

在本实施例中,采用低应力、致密的氮化硅薄膜钝化方式,有效地控制了台面型铟镓砷面阵探测器芯片的翘曲度;外延材料的表面和侧面处的in和al悬挂键得到充分的化学钝化,从而有效地提升了钝化效果;氮化硅钝化膜生长过程中未对外延材料的表面和侧面附近造成大的损伤,从而使得探测器的表面和侧面暗电流得到抑制。

[0057]

具体地,作为一实施例,本实施例提供一种台面型铟镓砷探测器芯片的制备方法,如图2所示,所述台面型铟镓砷探测器芯片主要包括:半绝缘inp衬底1;以及,在半绝缘inp衬底1上,依次生长的n

+

型inp层2、组分渐变的n

+

型in

x

al

1-x

as缓冲层3、in

x

ga

1-x

as吸收层4、p

+

型in

x

al

1-x

as帽层5、氮化硅(sin

x

)钝化膜6、p电极7和加厚电极8。

[0058]

其中,在所述台面型铟镓砷探测器芯片的表面覆盖的氮化硅钝化膜6包含两层薄膜,底层的氮化硅薄膜起着表面钝化的作用,顶层的氮化硅薄膜起着调节应力的作用,该氮化硅钝化膜生长前后大面阵探测器芯片的具有很小的翘曲度以及良好的器件性能。

[0059]

如图1所示,所述制备方法主要包括以下步骤:

[0060]

步骤101、外延片上沉积氮化硅掩膜。

[0061]

在本步骤中,在铟镓砷外延片上沉积氮化硅掩膜,用作刻蚀掩膜。

[0062]

具体地,在本步骤中,在铟镓砷外延片上采用pecvd法沉积厚度范围为380nm~420nm的氮化硅,以形成氮化硅掩膜,其中,射频功率的范围为35w~45w,衬底的温度范围为310℃~330℃,采用的工艺气体包括sih4及n2,其中sih4:n2的范围为1:16~1:20,优选地,气体流量sih4:n2为1:18。

[0063]

步骤102、刻蚀台面。

[0064]

在本步骤中,刻蚀台面,分为刻蚀氮化硅和刻蚀铟镓砷(in

x

ga

1-x

as)外延片形成台面两部分。

[0065]

具体地,在本步骤中,采用icp刻蚀技术刻蚀氮化硅,其中,刻蚀条件包括:icp功率范围为1995w~2005w,射频功率的范围为35w~45w,刻蚀气体采用sf6;采用icp刻蚀技术刻蚀铟镓砷外延片形成台面,其中,刻蚀条件包括:icp功率范围为345w~355w,射频功率的范围为125w~135w,刻蚀气体采用cl2和n2。

[0066]

步骤103、去除氮化硅掩膜。

[0067]

具体地,在本步骤中,采用氢氟酸缓冲液在室温下腐蚀115s~125s,腐蚀液体积比为hf:nh4f:h2o为3:6:10。

[0068]

步骤104、开n槽。

[0069]

在本步骤中,在铟镓砷外延片上开设n槽。

[0070]

具体地,在本步骤中,用酒石酸溶液腐蚀铟镓砷层,腐蚀液体积比为重量比酒石酸溶液:h2o为1:1,腐蚀速率为0.45μm/min~0.55μm/min。

[0071]

步骤105、生长p电极。

[0072]

在本步骤中,生长p电极,用作p电极7。

[0073]

具体地,在本步骤中,采用电子束蒸发工艺淀积厚度为20nm

±

5nm/30nm

±

5nm/20nm

±

5nm的ti/pt/au。

[0074]

步骤106、快速热退火。

[0075]

具体地,在本步骤中,退火条件为氮气保护气氛,退火温度范围为415℃~425℃,温度保持时间范围为35s~45s。

[0076]

步骤107、沉积氮化硅钝化膜。

[0077]

在本步骤中,在铟镓砷外延片上采用pecvd法生长两叠层的氮化硅钝化膜作为钝化膜,钝化膜的总厚度为300nm~600nm。钝化膜为pecvd技术生长的低应力、致密的氮化硅钝化膜,该钝化膜在生长过程中对芯片表面造成的损伤小。

[0078]

其中,底层氮化硅钝化膜为致密的呈压应力的si3n4薄膜,底层氮化硅钝化膜的厚度范围为100nm~200nm,顶层氮化硅钝化膜为si百分含量较高相对疏松且呈拉应力的sin

x

薄膜,如si2n薄膜,所述顶层氮化硅钝化膜的厚度范围为200nm~400nm。

[0079]

具体地,在本步骤中,所述底层氮化硅钝化膜的生长条件为:采用脉冲射频作为激励电源,射频电源功率的范围为55w~65w,射频频率的设定范围为95khz~105khz,优选为100khz,脉冲信号占空比的范围为20%~50%,衬底的温度范围为310℃~330℃,采用的工艺气体为sih4及n2,其中sih4:n2的范围为1:198~1:202,优选为1:200,压强的范围为400mtorr~800mtorr。

[0080]

具体地,在本步骤中,所述顶层氮化硅钝化膜的生长条件为:采用13.5mhz~13.6mhz射频作为激励电源,优选为13.56mhz,射频电源功率的范围为35w~45w,衬底的温度范围为310℃~330℃,采用的工艺气体为sih4及n2,其中sih4:n2的范围为1:198~1:202,优选为1:200,压强的范围为400mtorr~800mtorr。

[0081]

步骤108、开p、n电机孔。

[0082]

在本步骤中,在铟镓砷外延片上开设p、n电极孔。

[0083]

具体地,在本步骤中,采用的工艺条件与步骤102中的刻蚀氮化硅的工艺条件相同或相近。

[0084]

步骤109、生长加厚电极。

[0085]

在本步骤中,在铟镓砷外延片上生长加厚电极,用作加厚电极8。

[0086]

具体地,在本步骤中,采用离子束溅射工艺依次淀积厚度范围为15nm~25nm的cr和厚度范围为380nm~420nm的au。

[0087]

步骤110、划片。

[0088]

在本步骤中,进行划片,测试芯片。

[0089]

本实施例还提供一种台面型铟镓砷探测器芯片,所述台面型铟镓砷探测器芯片利用如上述的制备方法制备。

[0090]

本实施例提供的台面型铟镓砷探测器芯片及其制备方法,主要具有以下有益效果:

[0091]

1、制备出的底层氮化硅钝化膜为致密的si3n4薄膜,化学钝化效果优异。由于反应气体流量比sih4:n2为1:190以上,n2百分含量极高,在100khz的射频频率激励下,等离子体场中的电子比13.56mhz下能够获得更高的能量,因而能够相对高效地分解n≡n键,使得等

离子体场中有足够多的激发态n原子扩散至外延片表面与含si活性基反应生成致密的si3n4,而且外延片高达320

±

10℃的温度能够有效地迫使h原子逃逸外延片表面,造成si3n4中h的含量极少,这提升了si3n4的致密性,使得界面处与in、al结合的n密度较13.56mhz下高出一倍以上,有效减少器件表面的悬挂键,从而改善表面钝化效果,使得器件的表面侧面暗电流得到有效的抑制。

[0092]

2、制备的复合氮化硅薄膜应力低。底层si3n4本身已经比较致密,成压应力状态,又因为在100khz的射频频率激励下,鞘层中的离子具有比13.56mhz下更高的能量,能够通过轰击外延层表面而嵌入si3n4表面数层原子层深度,使得底层si3n4薄膜压应力明显;而顶层薄膜由于在13.56mhz生长,n≡n键难以打开,导致生长的sin

x

薄膜为si2n,该结构的膜比较疏松,且鞘层中的离子能量较小,不能有效地嵌入si3n4表面,使得顶层si2n薄膜呈拉应力,通过选择两层薄膜的相对厚度,复合氮化硅薄膜的应力能得到有效控制,使得大面阵探测器芯片的翘曲度也能被控制在很小的范围。

[0093]

3、钝化膜生长过程中未对外延材料的表面和侧面附近造成大的损伤。底层si3n4采用脉冲射频作为激励信号,即脉冲信号on的状态下有效激励信号为经设定的100khz下的连续射频信号;脉冲信号off的状态下有效激励信号为零。其优点在于耦合进等离子体场的射频功率可以通过脉冲信号的占空比被任意调节,该功率可以低于为保持等离子体场稳定而所需要的阈值,耦合进等离子体场的射频功率越小,等离子体的电压v

pl

就越小,鞘层的电压差越小,轰击到外延片上的离子能量越小,对外延材料表面附近的损伤也就越小,极小的表面损伤使得探测器的表面和侧面暗电流得到有效抑制。

[0094]

虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1