显示装置及电子设备的制作方法

[0001]

本申请涉及显示技术领域,尤其涉及一种显示装置及电子设备。

背景技术:

[0002]

目前,在有机发光二极管(active metrix organic light emitting diode,amoled)显示面板设计中,采用屏下摄像头区域进行显示已是大势所趋。其中,利用透明导线与屏下摄像头区域的像素电性连接,以提高屏下摄像头区的透光率,从而实现屏下摄像头区透明显示是常用的方案。然而,由于透明导线在经过像素驱动电路的驱动晶体管的栅极引线时,会与栅极引线之间形成寄生电容,由于透明导线分布不均,导致透明导线与栅极引线之间的寄生电容存在差异,寄生电容差异导致像素驱动电路驱动对应的像素也存在显示差异,导致有机发光二极管显示面板出现显示亮度明暗不均(mura)的问题。

[0003]

因此,有必要提出一种技术方案以解决透明导线与栅极引线之间的寄生电容差异导致显示明暗不均的问题。

技术实现要素:

[0004]

本申请的目的在于提供一种显示装置及电子设备,以改善透明导线与栅极引线之间的寄生电容差异导致显示明暗不均的问题。

[0005]

一种显示装置,所述显示装置具有显示透光区和过渡显示区,所述过渡显示区位于所述显示透光区的外围,所述显示装置包括:

[0006]

多个发光器件,设置于所述显示透光区;

[0007]

多个像素驱动电路,设置于所述过渡显示区,每个所述像素驱动电路包括:

[0008]

驱动晶体管,所述驱动晶体管包括栅极;以及

[0009]

栅极引线,所述栅极引线位于所述驱动晶体管的上方,所述栅极引线与所述驱动晶体管的所述栅极电性连接;

[0010]

至少一个透明导电层,至少一个所述透明导电层位于多个所述像素驱动电路的上方,至少一个所述透明导电层包括多条透明导线,多条所述透明导线电性连接多个所述发光器件和部分所述像素驱动电路;以及

[0011]

屏蔽层,所述屏蔽层位于多条所述栅极引线和至少一个所述透明导电层之间,且对应多条所述栅极引线设置。

[0012]

在上述显示装置中,在所述显示装置的厚度方向上,多条所述栅极引线在所述显示装置的基板上的正投影位于所述屏蔽层在所述显示装置的所述基板上的正投影的内部。

[0013]

在上述显示装置中,所述显示装置还包括用于传输直流电压信号的金属网格,所述金属网格与所述屏蔽层同层设置,设置于所述过渡显示区且位于多个所述像素驱动电路上方的所述金属网格延伸出所述屏蔽层。

[0014]

在上述显示装置中,所述显示装置还包括多条直流电源信号线,多条所述直流电源信号线与多条所述栅极引线同层设置,所述金属网格与多条所述直流电源信号线电性连

接。

[0015]

在上述显示装置中,所述显示装置还具有主显示区,所述过渡显示区位于所述主显示区和所述显示透光区之间,多条所述直流电源信号线与所述金属网格之间设置有绝缘层,所述绝缘层对应所述主显示区的部分设置有过孔,所述金属网格与多条所述直流电源信号线通过所述过孔电性连接。

[0016]

在上述显示装置中,所述直流电压信号选自初始化信号或直流电源信号中的一种。

[0017]

在上述显示装置中,每个所述像素驱动电路还包括补偿晶体管以及电极板,所述电极板对应所述驱动晶体管的所述栅极设置且所述电极板位于所述栅极引线和所述驱动晶体管的所述栅极之间,

[0018]

所述栅极引线的一端与所述像素驱动电路的所述补偿晶体管的有源层电性连接,所述栅极引线的另一端至少通过所述电极板上的过孔与所述驱动晶体管的所述栅极连接。

[0019]

在上述显示装置中,部分所述透明导线由所述过渡显示区延伸至所述显示透光区,且部分所述透明导线位于所述过渡显示区。

[0020]

在上述显示装置中,所述显示装置包括多个所述透明导电层,多条所述透明导线位于不同的所述透明导电层。

[0021]

在上述显示装置中,所述显示透光区的形状为圆形,多个所述像素驱动电路组成多个像素驱动电路岛,多个所述像素驱动电路岛环绕所述显示透光区设置,且至少两个所述像素驱动电路岛中的所述像素驱动电路的数目不同。

[0022]

一种电子设备,所述电子设备包括上述显示装置以及感光单元,所述感光单元对应所述显示装置的所述显示透光区设置。

[0023]

有益效果:本申请通过屏蔽层屏蔽栅极引线与透明导线之间的寄生电容,避免寄生电容差异影响驱动晶体管的栅极的电位出现差异,提高驱动晶体管驱动发光器件的稳定性,避免显示装置的发光器件显示时出现明暗不均的问题。

附图说明

[0024]

图1为本申请实施例显示装置的平面示意图;

[0025]

图2为图1所示显示装置的局部放大示意图;

[0026]

图3为图2所示显示装置的局部示意图;

[0027]

图4为图3所示第二像素驱动电路的等效电路图;

[0028]

图5为图4所示第二像素驱动电路对应的驱动时序图;

[0029]

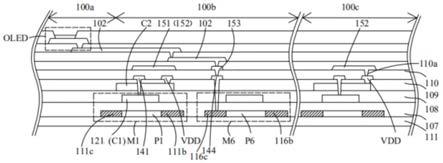

图6为显示装置的截面示意图;

[0030]

图7为第二像素驱动电路及与第二像素驱动电路连接的走线的平面示意图;

[0031]

图8-图12为组成图7所示第二像素驱动电路及与第二像素驱动电路连接走线的多个膜层的平面示意图。

具体实施方式

[0032]

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于

本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

[0033]

本申请提供一种显示装置,显示装置可以为液晶显示装置,也可以为有机发光二极管显示装置。具体地,显示装置为有机发光二极管显示装置。

[0034]

请参阅图1及图2所示,图1为本申请实施例显示装置的平面示意图,图2为图1所示显示装置的局部放大示意图,图3为图2所示显示装置的局部示意图。显示装置100具有显示透光区100a、主显示区100c以及过渡显示区100b。显示装置100包括多个第一显示像素、多个第一像素驱动电路(未示出)、多个第二显示像素、多个像素驱动电路岛101以及多条透明导线102。

[0035]

过渡显示区100b位于显示透光区100a的外围,过渡显示区100b位于主显示区100c和显示透光区100a之间。主显示区100c和过渡显示区100b均用于显示。显示透光区100a用于显示的同时,还具有高透光特性。显示透光区100a的透光率大于主显示区100c和过渡显示区100b的透光率。主显示区100c的面积大于过渡显示区100b的面积以及显示透光区100a的面积。显示透光区100a的形状为圆形,过渡显示区100b的形状为环形。显示透光区100a关于对称轴a-a以及对称轴b-b对称,对称轴a-a和对称轴b-b相互垂直。

[0036]

多个第一显示像素均匀地设置于主显示区100c,每个第一显示像素包括第一红色子像素100c1、第一绿色子像素100c3以及第一蓝色子像素100c2。第一红色子像素100c1、第一绿色子像素100c3以及第一蓝色子像素100c2在主显示区100c呈pentile设计分布。第一绿色子像素100c3的形状为椭圆形,第一红色子像素100c1和第一蓝色子像素100c2呈八边形。

[0037]

多个第一像素驱动电路也设置于主显示区100c。一个第一像素驱动电路对应驱动主显示区100c的一个子像素(第一红色子像素100c1、第一绿色子像素100c3以及第一蓝色子像素100c2中的一者)发光。每个第一像素驱动电路包括多个金属膜层,且多个第一像素驱动电路阵列地设置于主显示区100c,导致主显示区100c的透光率低。第一红色子像素100c1、第一绿色子像素100c3以及第一蓝色子像素100c2均包括发光器件,发光器件为有机发光二极管。

[0038]

多个第二显示像素均匀地设置于显示透光区100a和过渡显示区100b。每个第二显示像素包括第二红色子像素100a1、第二绿色子像素100a3以及第二蓝色子像素100a2。第二红色子像素100a1、第二绿色子像素100a3以及第二蓝色子像素100a2在显示透光区100a和过渡显示区100b均呈pentile设计分布。第二红色子像素100a1、第二绿色子像素100a3以及第二蓝色子像素100a2的形状均为圆形。第二红色子像素100a1、第二绿色子像素100a3以及第二蓝色子像素100a2均包括发光器件,发光器件为有机发光二极管,每个有机发光二极管包括阳极、阴极以及设置于阳极和阴极之间的有机发光层。

[0039]

第一红色子像素100c1的尺寸大于第二红色子像素100a1的尺寸,第一绿色子像素100c3的尺寸大于第二绿色子像素100a3的尺寸,第一蓝色子像素100c2的尺寸大于第二蓝色子像素100a2的尺寸,以保证显示透光区100a具有高透光率。从主显示区100c到过渡显示区100b,子像素的尺寸变小。

[0040]

由于一个第二红色子像素100a1与一个第一红色子像素100c1的尺寸不同,两者对应的驱动电路的驱动功率也不同,同理,第一绿色子像素100c3与第二绿色子像素100a3的

驱动电路的驱动功率也不同,且第一蓝色子像素100c2与第二蓝色子像素100a2的驱动电路的驱动功率也不同,故第一像素驱动电路只能用于驱动主显示区100c的第一红色子像素100c1、第一绿色子像素100c3以及第一蓝色子像素100c2,而不能用于驱动过渡显示区100b和显示透光区100a的第二红色子像素100a1、第二绿色子像素100a3以及第二蓝色子像素100a2。

[0041]

请结合图2及图3,多个像素驱动电路岛101设置于过渡显示区100b,每个像素驱动电路岛101包括多个阵列排布的第二像素驱动电路1011,每个像素驱动电路岛101包括m行以及n列的第二像素驱动电路1011,m大于或等于2,n大于或等于2,即每个像素驱动电路岛101呈条状。多个像素驱动电路岛101的第二像素驱动电路1011用于驱动多个第二显示像素发光,即多个像素驱动电路岛101的第二像素驱动电路1011用于驱动过渡显示区100b的第二显示像素发光的同时,还用于驱动显示透光区100a的第二显示像素发光,以避免显示透光区100a设置像素驱动电路,避免像素驱动电路的金属膜层对显示透光区100a的透光率造成影响,从而进一步地提高显示透光区100a的透光率。多个第二像素驱动电路1011组成多个像素驱动电路岛101,有利于减少多个第二像素驱动电路1011所需占用的空间,且有利于实现第二像素驱动电路1011对应显示透光区100a的第二显示像素进行驱动,然而,会导致与第二像素驱动电路1011电性连接的线路集中于像素驱动电路岛101布设的区域。像素驱动电路岛101是指多个第二像素驱动电路1011呈岛状聚集设置,其中,相邻两个像素驱动电路岛101之间的间距大于同一个像素驱动电路岛101中的相邻两个第二像素驱动电路1011之间的间距。

[0042]

与主显示区100c中不同,一个第二像素驱动电路1011用于驱动多个第二红色子像素100a1、多个第二绿色子像素100a3以及多个第二蓝色子像素100a2中的至少两个,以减少第二像素驱动电路1011的数目,减少像素驱动电路岛101占用的空间,从而使得显示透光区100a的尺寸可以增大或者使得过渡显示区100b具有更多不设置像素驱动电路岛101的空间。第二像素驱动电路1011可以用于驱动多个第二红色子像素100a1、多个第二绿色子像素100a3以及多个第二蓝色子像素100a2中发出色光相同的子像素和/或发出色光不同的子像素。在显示透光区100a,为同一个第二像素驱动电路1011驱动的子像素通过透明导线电性连接。

[0043]

具体地,两个第二红色子像素100a1被同一个第二像素驱动电路1011驱动,两个第二蓝色子像素100a2被同一个第二像素驱动电路1011驱动,四个第二绿色子像素100a3被同一个第二像素驱动电路1011驱动。

[0044]

如图2所示,多个像素驱动电路岛101环绕显示透光区100a设置,至少两个像素驱动电路岛101中的第二像素驱动电路1011的数目不同,以使得至少两个像素驱动电路岛101对应驱动的子像素驱动数目不同,适应显示透光区100a为圆形且每个像素驱动电路岛101的部分第二像素驱动电路1011用于驱动显示透光区100a中对应子像素时,显示透光区100a中对应每个像素驱动电路岛101的子像素的数目变化的情况。

[0045]

多个像素驱动电路岛101包括第一组像素驱动电路岛1012(对称轴b-b之上的像素驱动电路岛101)以及第二组像素驱动电路岛1013(对称轴b-b之下的像素驱动电路岛101)。第一组像素驱动电路岛1012中的像素驱动电路岛101和第二组像素驱动电路岛1013中的像素驱动电路岛101关于对称轴b-b对称设置,第一组驱动电路岛1012中的像素驱动电路岛

101关于对称轴a-a对称设置,第二组像素驱动电路岛1012中的像素驱动电路岛101关于对称轴a-a对称设置。

[0046]

第一组像素驱动电路岛1012中的部分像素驱动电路岛101中的第二像素驱动电路1011的数目从靠近对称轴a-a至远离对称轴a-a递减,对应地,第二组像素驱动电路岛1013中的部分像素驱动电路岛101中的第二像素驱动电路1011的数目从靠近对称轴a-a至远离对称轴a-a递减。第一组像素驱动电路岛1012中的一个像素驱动电路岛101和第二组像素驱动电路岛1013中对应的一个像素驱动电路岛101驱动两者所在区域以及显示透光区100a中两者之间的子像素,如区域100d的子像素。其中,第一组像素驱动电路岛1012和第二组像素驱动电路岛1013中的每个像素驱动电路岛101用于驱动该像素驱动电路岛101对应区域的子像素,还驱动该像素驱动电路岛101与第二组像素驱动电路岛1013中对应像素驱动电路岛之间显示透光区100a的子像素。

[0047]

如图3所示,为了提高显示透光区100a的透光率,多个第二像素驱动电路1011与显示透光区100a的第二红色子像素100a1、第二蓝色子像素100a2以及第二绿色子像素100a3通过多条透明导线102电性连接。由于多个第二像素驱动电路1011呈岛状集中分布,导致对应像素驱动电路岛101设置的透明导线102的数目较多,部分透明导线102会和与像素驱动电路岛101中的第二像素驱动电路1011的驱动晶体管的栅极电性连接的栅极引线交叠,而透明导线102分布密集且具有差异性,导致不同栅极引线与透明导线102交叠的面积存在差异。

[0048]

请参阅图4-图6,图4为图3所示第二像素驱动电路的等效电路图,图5为图4所示第二像素驱动电路对应的驱动时序图,图6为显示装置的截面示意图。

[0049]

每个第二像素驱动电路1011包括驱动晶体管m1、开关晶体管m2、补偿晶体管m3、初始化晶体管m4、第一发光控制晶体管m5、第二发光控制晶体管m6、阳极复位晶体管m7以及电容器c。驱动晶体管m1、开关晶体管m2、补偿晶体管m3、初始化晶体管m4、第一发光控制晶体管m5、第二发光控制晶体管m6以及阳极复位晶体管m7均为p型晶体管。

[0050]

显示装置100还包括多个与第二像素驱动电路1011电性连接的走线,多个走线包括设置于过渡显示区100b的第n-1级扫描信号线scan(n-1)、第n级扫描信号线scan(n)、数据线d(m)、初始化信号线vi、直流电源信号线vdd以及第n级发光控制信号线em(n)。第n-1级扫描信号线scan(n-1)用于传输第n-1级扫描信号。第n级扫描信号线scan(n)用于传输第n级扫描信号。数据线d(m)用于传输数据信号。直流电源信号线vdd用于传输直流电源信号。第n级发光控制信号线em(n)用于传输第n级发光控制信号。初始化信号线vi传输初始化信号或者复位信号。

[0051]

驱动晶体管m1的栅极g1与电容器c的第一电极板c1、补偿晶体管m3的漏极d3以及初始化晶体管m4的源极s4连接,驱动晶体管m1的源极s1通过第一发光控制晶体管m5与直流电源信号线vdd连接,且驱动晶体管m1的源极s1通过开关晶体管m2与数据线d(m)连接,驱动晶体管m1的漏极d1通过第二发光控制晶体管m6与发光器件oled连接。开关晶体管m2导通,驱动晶体管m1接收数据线d(m)传输的数据信号且给发光器件oled提供驱动电流。

[0052]

开关晶体管m2的栅极g2与第n级扫描信号线scan(n)连接,开关晶体管m2的源极s2与数据线d(m)连接,开关晶体管m2的漏极d2与驱动晶体管m1的源极s1连接,开关晶体管m2的漏极d2还通过第一发光控制晶体管m5与直流电源信号线vdd连接。开关晶体管m2根据第n

级扫描信号线scan(n)传输的第n级扫描信号导通或截止,控制数据线d(m)传输的数据信号是否写入至驱动晶体管m1的源极s1。

[0053]

补偿晶体管m3的栅极g3与第n级扫描信号线scan(n)连接,补偿晶体管m3的源极s3与驱动晶体管m1的漏极d1连接,补偿晶体管m3的源极s3还通过第二发光控制晶体管m6与发光器件oled连接,补偿晶体管m3的漏极d3与驱动晶体管m1的栅极g1、初始化晶体管m4的源极s4以及电容器c的第一电极板c1连接。补偿晶体管m3根据第n级扫描信号线scan(n)传输的第n级扫描信号导通,电性连接驱动晶体管m1的栅极g1和驱动晶体管m1的漏极d1。

[0054]

初始化晶体管m4的栅极g4与第n-1级扫描信号线scan(n-1)连接,初始化晶体管m4的漏极d4与阳极复位晶体管m7的漏极d7以及初始化信号线vi连接,初始化晶体管m4的源极s4与驱动晶体管m1的栅极g1、补偿晶体管m3的漏极d3以及电容器c的第一电极板c1连接。初始化晶体管m4根据第n-1级扫描信号线scan(n-1)传输的第n-1级扫描信号导通或截止,控制初始化信号线vi传输的初始化信号是否写入至驱动晶体管m1的栅极g1。

[0055]

第一发光控制晶体管m5的栅极g5与第n级发光控制信号线em(n)连接,第一发光控制晶体管m5的源极s5与直流电源信号线vdd以及电容器c的第二电极板c2连接,第一发光控制晶体管m5的漏极d5与驱动晶体管m1的源极s1以及开关晶体管m2的漏极d2连接。第一发光控制晶体管m5根据第n级发光控制信号线em(n)传输的第n级发光控制信号导通或截止,控制直流电源信号线vdd传输的直流电源信号是否写入至驱动晶体管m1的源极s1。

[0056]

第二发光控制晶体管m6的栅极g6与第n级发光控制信号线em(n)连接,第二发光控制晶体管m6的源极s6与驱动晶体管m1的漏极d1以及补偿晶体管m3的源极s3连接,第二发光控制晶体管m6的漏极d6与发光器件oled的阳极连接。第二发光控制晶体管m6根据第n级发光控制信号线em(n)传输的第n级发光控制信号导通或截止,控制驱动电流是否流入至发光器件oled。

[0057]

阳极复位晶体管m7的栅极g7与第n级扫描信号线scan(n)连接,阳极复位晶体管m7的漏极d7与初始化晶体管m4的漏极d4以及初始化信号线vi连接,阳极复位晶体管m7的源极s7与发光器件oled的阳极以及第二发光控制晶体管m6的漏极d6连接。阳极复位晶体管m7根据第n级扫描信号线scan(n)传输的第n级扫描信号导通或截止,控制初始化信号线vi传输的初始化信号是否写入至发光器件oled的阳极。

[0058]

电容器c的第一电极板c1与驱动晶体管m1的栅极g1、初始化晶体管m4的源极s4以及补偿晶体管m3的漏极d3连接,电容器c的第二电极板c2与直流电源信号线vdd以及第一发光控制晶体管m5的源极s5连接。电容器c用于维持驱动晶体管m1驱动发光器件oled发光时驱动晶体管m1的栅极的电压。

[0059]

结合图5,在初始化阶段t1,第n-1级扫描信号线scan(n-1)输入低电平的第n-1级扫描信号,初始化晶体管m4导通,初始化信号线vi传输的初始化信号传输至驱动晶体管m1的栅极g1,实现对驱动晶体管m1的栅极g1的初始化;第n级扫描信号线scan(n)输入高电平的第n级扫描信号,开关晶体管m2、补偿晶体管m3以及阳极复位晶体管m7均截止;第n级发光控制信号线em(n)输入高电平的第n级发光控制信号,第一发光控制晶体管m5和第二发光控制晶体管m6均截止。

[0060]

在阈值电压补偿及数据电压写入阶段t2,第n-1级扫描信号线scan(n-1)输入高电平的第n-1级扫描信号,初始化晶体管m4截止;第n级扫描信号线scan(n)输入低电平的第n

级扫描信号,开关晶体管m2、补偿晶体管m3以及阳极复位晶体管m7均导通,导通的开关晶体管m2将数据线d(m)传输的数据信号写入至驱动晶体管m1的源极,导通的补偿晶体管m3使驱动晶体管m1的栅极g1和驱动晶体管m1的漏极d1电性连接,导通的阳极复位晶体管m7将初始化信号线vi传输的初始化信号输出至发光器件oled的阳极;第n级发光控制信号线em(n)输入高电平的第n级发光控制信号,第一发光控制晶体管m5和第二发光控制晶体管m6均截止。在此阶段实现驱动晶体管m1的阈值电压的补偿、数据信号的写入以及发光器件oled的阳极的初始化。

[0061]

在发光阶段t3,第n-1级扫描信号线scan(n-1)输入高电平的第n-1级扫描信号,初始化晶体管m4截止;第n级扫描信号线scan(n)输入高电平的第n级扫描信号,开关晶体管m2、补偿晶体管m3以及阳极复位晶体管m7均截止;第n级发光控制信号线em(n)输入低电平的第n级发光控制信号,第一发光控制晶体管m5和第二发光控制晶体管m6均导通,驱动晶体管m1导通且输出驱动电流,发光器件oled发光。

[0062]

如图6所示,显示装置100包括基板111,每个第二像素驱动电路1011包括一个驱动晶体管m1、一个电容器、一个补偿晶体管m3以及一个第二发光控制晶体管m6。显示装置100还包括设置于过渡显示区100b和显示透光区100a的至少一个透明导电层,至少一个透明导电层位于多个像素驱动电路岛101的上方,至少一个透明导电层包括多个透明导线102。第二像素驱动电路1011以及至少一个透明导电层均设置于基板111上。基板111可以为柔性基板,也可以为玻璃基板。

[0063]

驱动晶体管m1包括驱动有源层p1以及驱动栅极121,驱动有源层p1的相对两端通过掺杂以分别形成驱动源极111b以及驱动漏极111c。第二发光控制晶体管m6包括第二发光控制有源层p6以及第二发光控制栅极。第二发光控制有源层p6的相对两端通过掺杂分别形成第二发光控制源极116b以及第二发光控制漏极116c。驱动有源层p1与第二发光控制有源层p6同层设置。驱动栅极121与第二发光控制栅极同层设置。补偿晶体管m3的补偿有源层与驱动有源层p1同层设置,且补偿晶体管m3的补偿栅极与驱动栅极121同层设置。电容器c包括第一电极板c1以及第二电极板c2,第一电极板c1为驱动栅极121。

[0064]

驱动有源层p1设置于基板111上,驱动栅极121设置于驱动有源层p1的上方且驱动有源层p1与驱动栅极121之间设置有第一绝缘层107。第二电极板c2设置于第一电极板c1的正上方,驱动栅极121和第二电极板c2之间设置有第二绝缘层108。栅极引线141位于驱动晶体管m1的上方,且栅极引线141位于第二电极板c2的上方,栅极引线141与第二电极板c2之间设置有第三绝缘层109。每个栅极引线141的一端通过贯穿第一绝缘层107、第二绝缘层108以及第三绝缘层109的过孔与第二像素驱动电路1011的补偿晶体管m3的补偿有源层电性连接,栅极引线141的另一端通过贯穿第三绝缘层109、第二电极板c2以及第二绝缘层108的过孔与驱动栅极121电性连接。栅极引线141、第一阳极引线144以及直流电源信号线vdd位于同一膜层。直流电源信号线vdd输入且传输直流电源信号,且通过贯穿第三绝缘层109的过孔与第二电极板c2电性连接。第一阳极引线144通过贯穿第三绝缘层109、第二绝缘层108以及第一绝缘层107的过孔与第二发光控制晶体管m6的第二发光控制漏极116c电性连接,第二阳极引线153位于第一阳极引线144的正上方,第二阳极引线153与第一阳极引线144之间有第四绝缘层110,第二阳极引线153与第一阳极引线144通过贯穿第四绝缘层110的过孔电性连接,多条透明导线102位于第二阳极引线153的上方,多条透明导线102与第二

阳极引线153电性连接,且多条透明导线102与发光器件oled的阳极电性连接,使得多条透明导线102电性连接多个发光器件oled和部分第二像素驱动电路1011。第一绝缘层107、第二绝缘层108以及第三绝缘层109均为无机绝缘层,第一绝缘层107、第二绝缘层108以及第三绝缘层109的制备材料选自氮化硅以及氧化硅中的至少一种。第四绝缘层110为有机绝缘层,有机绝缘层的制备材料选自聚酰亚胺。

[0065]

多条透明导线102位于多个透明导电层,以增加透明导线102的布设空间,避免透明导线102布设空间较小导致透明导线102之间出现短路。透明导线102的制备材料为氧化铟锡或者氧化铟锌中的至少一种。位于相邻膜层的透明导线102之间设置有机绝缘层。

[0066]

显示装置包括屏蔽层151,屏蔽层151设置于过渡显示区100b,屏蔽层151位于多条栅极引线141和至少一个透明导电层之间,且屏蔽层151对应栅极引线141设置。屏蔽层151屏蔽栅极引线141与透明导线102之间的寄生电容,避免寄生电容导致驱动晶体管m1的栅极电位不稳定,且避免寄生电容差异导致寄生电容对驱动晶体管m1的栅极电位影响差异较大,提高驱动晶体管m1的工作稳定性,避免显示装置的显示透光区100a出现显示不均的问题。

[0067]

在显示装置100的厚度方向上,多条栅极引线141在显示装置100的基板111上的正投影位于屏蔽层151在显示装置100的基板111上的正投影的内部,使得与栅极引线141对应的屏蔽层151的面积大于栅极引线141的面积,以使屏蔽层151完全遮蔽对应的栅极引线141,完全避免多条栅极引线141与多条透明导线102之间产生寄生电容。

[0068]

显示装置100还包括用于传输直流电压信号的金属网格152,屏蔽层151与金属网格152同层设置。部分金属网格152设置于多个像素驱动电路岛101的正上方,部分金属网格152设置于主显示区100c,且主显示区100c的金属网格152与多个像素驱动电路岛101正上方的金属网格152电性连接。金属网格152与直流电源信号线vdd电性连接,以降低直流电源线vdd传输的直流电源信号的电阻压降。金属网格152呈网格状。金属网格152的制备材料选自钼、铝、钛以及铜中的至少一种。

[0069]

设置于过渡显示区100b且位于多个第二像素驱动电路1011像上方的金属网格152延伸出屏蔽层151,以使屏蔽层151传输固定电压信号,屏蔽层151与栅极引线141之间形成寄生电容,然而屏蔽层151的电位是稳定的,也可以保证栅极引线141的电位稳定,避免透明导线102电位不稳定导致栅极引线141的电位不稳定,提高驱动晶体管m1的栅极电位的稳定性,提高驱动晶体管m1的工作稳定性,进而提高驱动晶体管m1驱动的子像素的亮度均一性。

[0070]

直流电压信号选自初始化信号或直流电源信号中的一种。由于初始化信号由初始化信号线vi传输,可以使初始化信号线vi与金属网格152之间电性连接,以使金属网格152传输直流电压信号。其中,初始化信号线vi与第二电极板c2同层设置。直流电源信号由直流电源信号线vdd传输,也可以使直流电源信号线vdd与金属网格152之间电性连接,以使金属网格152传输直流电压信号,使得屏蔽层151具有固定电压。

[0071]

显示装置100还包括多条直流电源信号线vdd。如前所述,多条直流电源信号线vdd与多条栅极引线141同层设置,金属网格152与多条直流电源信号线vdd电性连接。

[0072]

部分直流电源信号线vdd设置于过渡显示区100b且对应多个像素驱动电路岛101设置,且与多个像素驱动电路岛101的第二像素驱动电路1011电性连接;部分直流电源信号线vdd设置于主显示区100c且与第一像素驱动电路电性连接。对应多个像素驱动电路岛101

设置的金属网格152的部分对应过渡显示区100b的多条直流电源信号线vdd设置,即对应多个像素驱动电路岛101设置的金属网格152的部分位于过渡显示区100b的多条直流电源信号线vdd的正上方,以使传输相同信号的走线对应设置,避免产生电信号干扰。

[0073]

由于主显示区100c的第一像素驱动电路与像素驱动电路岛101中第二像素驱动电路1011的驱动功率不同,主显示区100c的直流电源信号线vdd的宽度比过渡显示区100b的直流电源信号线vdd的宽度大。过渡显示区100b的直流电源信号线vdd的宽度较小时,第四绝缘层110对主显示区100c的部分设置有过孔110a,主显示区100c的直流电源信号线vdd与主显示区100c的金属网格152通过主显示区100c的过孔110a电性连接,且由于主显示区100c的金属网格152与过渡显示区100b的金属网格152连接,使得过渡显示区100b的直流电源信号线vdd与过渡显示区100b的金属网格152电性连接。过渡显示区100b的直流电源信号线vdd的宽度较大时,过渡显示区100b的直流电源信号线vdd与过渡显示区100b的金属网格152也可以通过第四绝缘层110对应过渡显示区100b设置的过孔电性连接。

[0074]

部分透明导线102由过渡显示区100b延伸至显示透光区100a,且部分透明导线102位于过渡显示区100b,以使透明导线102连接过渡显示区100b的第二像素驱动电路1011和显示透光区100a的第二显示像素。

[0075]

以下结合具体实施例对上述方案进行详述。图7为第二像素驱动电路及与第二像素驱动电路连接的走线的平面示意图,图8-图12为组成图7所示第二像素驱动电路及与第二像素驱动电路连接走线的多个膜层的示意图。图8为图案化半导体层,图9为图案化第一金属层,图10为图案化第二金属层,图11为图案化第三金属层,图12为图案化第四金属层。图8所示图案化半导体层和图9所示图案化第一金属层之间设置有上述第一绝缘层107,图9所示图案化第一金属层与图10所示图案化第二金属层之间设置有上述第二绝缘层108,图10所示图案化第二金属层与图11所示图案化第三金属层之间设置有上述第三绝缘层109,图11所示图案化第三金属层与图12所示图案化第四金属层之间设置有上述第四绝缘层110。

[0076]

与第二像素驱动电路1011连接的走线包括数据线d(m)、初始化信号线vi、第n级扫描信号线scan(n)、第n-1级扫描信号线scan(n-1)、第n级发光控制信号线em(n)以及直流电源信号线vdd。

[0077]

第二像素驱动电路1011包括驱动晶体管m1、开关晶体管m2、补偿晶体管m3、初始化晶体管m4、第一发光控制晶体管m5、第二发光控制晶体管m6、阳极复位晶体管m7以及电容器。

[0078]

图案化半导体层11包括驱动晶体管m1的驱动沟道111a、开关晶体管m2的开关沟道112a、补偿晶体管m3的补偿沟道113a、初始化晶体管m4的初始化沟道114a、第一发光控制晶体管m5的第一发光控制沟道115a、第二发光控制晶体管m6的第二发光控制沟道116a以及阳极复位晶体管m7的阳极复位沟道117a。驱动沟道111a、开关沟道112a、补偿沟道113a、初始化沟道114a、第一发光控制沟道115a、第二发光控制沟道116a以及阳极复位沟道117a均位于同一层。图案化半导体层11的制备材料可以为多晶硅。图案化半导体层11还包括驱动晶体管m1的驱动源极111b以及驱动漏极111c。图案化半导体层11还包括开关晶体管m2的开关源极112b以及开关漏极112c。图案化半导体层11还包括补偿晶体管m3的补偿源极113b以及补偿漏极113c。图案化半导体层11还包括初始化源极114b以及初始化漏极114c。图案化半

导体层11还包括第一发光控制晶体管m5的第一发光控制源极115b以及第一发光控制漏极115c。图案化半导体层11还包括第二发光控制晶体管m6的第二发光控制源极116b以及第二发光控制漏极116c。图案化半导体层11还包括阳极复位晶体管m7的阳极复位源极117b以及阳极复位漏极117c。图案化半导体层11上的源极和漏极是通过将有源层进行掺杂实现导体化后得到。

[0079]

图案化第一金属层12包括驱动晶体管m1的驱动栅极121,驱动晶体管m1的驱动栅极121也是电容器的第一电极板c1。开关晶体管m2的开关栅极122以及补偿晶体管m3的补偿栅极123均为第n级扫描信号线scan(n)的一部分,初始化晶体管m4的补偿栅极124为第n-1级扫描信号线scan(n-1)的部分,第一发光控制晶体管m5的第一发光控制栅极125和第二发光控制晶体管m6的第二发光控制栅极126均为第n级发光控制信号线em(n)的一部分。阳极复位晶体管m7的阳极复位栅极127为第n级扫描信号线scan(n)的一部分。第n-1级扫描信号线scan(n-1)、第n级发光控制信号线em(n)、两条第n级扫描信号线scan(n)以及驱动晶体管m1的驱动栅极121均属于图案化第一金属层12,第n-1级扫描信号线scan(n-1)、第n级发光控制信号线em(n)、第n级扫描信号线scan(n)均相互平行设置,驱动晶体管m1的驱动栅极121的形状为矩形。图案化第一金属层12的制备材料包括钼、铝、钛以及铜中的至少一种。

[0080]

图案化第二金属层13包括两条初始化信号线vi以及第二电极板c2。第二电极板c2对应驱动晶体管m1的驱动栅极121设置,且驱动栅极121与第二电极板c2形成电容器。第二电极板c2上设置有过孔c2a。图案化第二金属层13的制备材料包括钼、铝、钛以及铜中的至少一种。

[0081]

图案化第三金属层14包括栅极引线141、第一初始化引线142、第二初始化引线143、数据线d(m)、直流电源信号线vdd以及第一阳极引线144。栅极引线141的一端通过贯穿第三绝缘层109、第二绝缘层108以及第二电极板c2的第一过孔141a与驱动晶体管m1的驱动栅极121电性连接,栅极引线141的另一端通过贯穿第三绝缘层109、第一绝缘层107和第二绝缘层108的第二过孔141b与补偿晶体管m3的补偿漏极电性连接。第一初始化引线142的一端通过贯穿第三绝缘层109的第三过孔142a与初始化信号线vi电性连接,第一初始化引线142的另一端通过贯穿第三绝缘层109、第二绝缘层108以及第一绝缘层107的第四过孔142b与初始化晶体管m4的初始化漏极114c电性连接。第二初始化引线143的一端通过贯穿第三绝缘层109的第五过孔143a与初始化信号线vi电性连接,第二初始化引线143的另一端通过贯穿第三绝缘层109、第二绝缘层108以及第一绝缘层107的第六过孔143b与阳极复位晶体管m7的阳极复位漏极117c电性连接。第一阳极引线144通过贯穿第三绝缘层109、第二绝缘层108以及第一绝缘层107的第七过孔144a与第二发光控制晶体管m6的第二发光控制漏极116c电性连接。数据线d(m)通过贯穿第三绝缘层109、第二绝缘层108以及第一绝缘层107的第八过孔145a与开关晶体管m2的开关源极112b电性连接。直流电源信号线vdd通过贯穿第三绝缘层109、第二绝缘层108以及第一绝缘层107的第九过孔146b与第一发光控制晶体管m5的第一发光控制源极115b电性连接。直流电源信号线vdd通过贯穿第三绝缘层109的第十过孔146a与第二电极板c2电性连接,使得第二电极板c2导入直流电源信号。图案化第三金属层14的制备材料包括钼、铝、钛以及铜中的至少一种。直流电源信号线vdd与数据线d(m)平行设置,且数据线d(m)与初始化信号线vi以及第n级扫描信号线scan(n)等垂直相交。

[0082]

图案化第四金属层15包括金属网格152、屏蔽层151以及第二阳极引线153。金属网

格152包括垂直延伸部1521以及水平延伸部1522,垂直延伸部1521与水平延伸部1522垂直相交且组成网格状的金属网格152。垂直延伸部1521对应直流电源信号线vdd设置,水平延伸部1522与第二电极板c2的部分重合,以使得传输直流电源信号的走线对应设置。第二阳极引线153设置于第一阳极引线144的正上方且通过贯穿第四绝缘层110的过孔与第一阳极引线144连接。且上述透明导电层位于图案化第四金属层15的上方,且透明导线102连接于第二阳极引线153和发光器件oled的阳极之间。金属网格152可以通过贯穿第四绝缘层110的过孔与直流电源信号线vdd连接以导入直流电源信号。图案化第四金属层15的制备材料包括钼、铝、钛以及铜中的至少一种。

[0083]

本申请还提供一种电子设备,电子设备包括上述显示装置及感光单元,感光单元对应显示装置的显示透光区设置。感光单元为摄像头。

[0084]

以上实施例的说明只是用于帮助理解本申请的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例的技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1