半导体装置的制作方法

1.本发明涉及作为功率器件等有用的半导体装置。

背景技术:

2.氧化镓(ga2o3)在室温下具有4.8~5.3ev的宽带隙,是几乎不吸收可见光和紫外线的透明半导体。因此,特别是在深紫外光线区域中操作的光器件、电器件和透明电子产品中使用的有前途的材料,近年来,正在进行基于氧化镓(ga2o3)的光检测器、发光二极管(led)和晶体管的开发(参照非专利文献1)。

3.另外,在氧化镓(ga2o3)中存在α、β、γ、σ、ε这五种晶体结构,通常最稳定的结构是β-ga2o3。然而,β-ga2o3是β-gallia结构,因此与通常以电子材料等利用的晶体系不同,不一定适合对半导体装置的利用。另外,β-ga2o3薄膜的生长需要高基板温度和高真空度,因此也存在制造成本增加的问题。另外,如非专利文献2所记载的那样,在β-ga2o3中,即使是高浓度(例如1

×

10

19

/cm3以上)的掺杂剂(si),在离子注入后,如果不在800℃~1100℃的高温下实施退火处理,也不能作为供体使用。

4.另一方面,α-ga2o3具有与已经通用的蓝宝石基板相同的晶体结构,因此适合用于光器件、电器件,进而由于其具有比β-ga2o3更宽的带隙,因此对于功率器件特别有用,因此期待将α-ga2o3用作半导体的半导体装置。

5.在专利文献1和2中,作为将β-ga2o3用作半导体并得到与之相适合的欧姆特性的电极,记载了使用由ti层和au层构成的两层、由ti层、al层和au层构成的三层,或者由ti层、al层、ni层和au层构成的四层的半导体装置。

6.另外,在专利文献3中,作为将β-ga2o3用作半导体并得到与之相适合的肖特基特性的电极,记载了使用au、pt或ni和au的层叠体中的任意一个的半导体装置。

7.但是,在将专利文献1~3记载的电极应用于将α-ga2o3用作半导体的半导体装置的情况下,存在作为肖特基电极或欧姆电极不起作用、电极不与膜粘合、半导体特性受损等问题。进而,专利文献1~3所记载的电极结构会从电极端部产生漏电流等,并不能得到作为半导体装置在实用上满意的电极结构。

8.在专利文献4中,研究了将α-ga2o3用作半导体,作为肖特基电极使用包含选自元素周期表第4族~9族中的至少一种金属的电极的半导体装置。另外,专利文献4涉及本技术人的专利申请。

9.专利文献1:日本特开2005-260101号公报

10.专利文献2:日本特开2009-81468号公报

11.专利文献3:日本特开2013-12760号公报

12.专利文献4:日本特开2018-60992号公报

13.【非专利文献1】jun liang zhao et al,“uv and visible electroluminescence from a sn:ga2o3/n+-si heterojunction by metal-organic chemical vapor deposition”,ieee transactions on electron devices,vol.58,no.5 may 2011(赵俊良

等,“通过金属-有机化学气相沉积从sn:ga2o3/n+-si异质结中产生的紫外和可见光电致发光”,《ieee电子器件学报》,第58卷,2011年5月第5期)

14.【非专利文献2】kohei sasaki et al,“si-ion implantation doping inβ-ga2o

3 and its application to fabrication of low-resistance ohmic contacts”,applied physics express 6(2013)086502(kohei sasaki等,“β-ga2o3中的硅离子注入掺杂及其在低电阻欧姆接触的制造中的应用”,《应用物理快报》,第6卷,(2013年)086502)

技术实现要素:

15.本发明的目的在于提供一种抑制漏电流的低损耗的半导体装置。

16.本发明人等为了达成上述目的,进行了深入研究的结果发现如下:一种半导体装置,至少具备半导体层和肖特基电极,所述半导体层包含具有刚玉结构的氧化物半导体作为主成分,所述肖特基电极包含第一电极层和导电率高于第一电极层的第二电极层,第二电极层的外端部经由第一电极层与所述半导体层电连接,第一电极层的外端部位于比电连接的第二电极层的电连接区域的外端部更外侧的位置,这种半导体装置能够将耗尽层良好地延伸到半导体层内,并且是抑制了漏电流的低损耗的半导体装置,这样获得的半导体装置能够一举解决上述现有的问题。

17.另外,本发明人等在得到上述见解之后,进一步经过反复研究,终于完成了本发明。

18.即,本发明涉及以下技术方式。

19.[1]一种半导体装置,至少具备半导体层和肖特基电极,所述半导体层包含具有刚玉结构的氧化物半导体作为主成分,所述肖特基电极包含第一电极层和导电率高于第一电极层的第二电极层,其特征在于,第二电极层的外端部经由第一电极层与所述半导体层电连接,第一电极层的外端部位于比电连接的第二电极层的电连接区域的外端部更外侧的位置。

[0020]

[2]根据所述[1]所述的半导体装置,其中,所述氧化物半导体包含选自铝、铟和镓中的至少一种金属。

[0021]

[3]根据所述[1]或[2]所述的半导体装置,其中,所述氧化物半导体至少包含镓。

[0022]

[4]根据所述[1]~[3]中任一项所述的半导体装置,其中,第一电极层包含选自元素周期表第4族~第10族中的至少一种金属。

[0023]

[5]根据所述[1]~[4]中任一项所述的半导体装置,其中,第一电极层包含选自元素周期表第4族和第9族中的至少一种金属。

[0024]

[6]根据所述[1]~[5]中任一项所述的半导体装置,其中,第一电极层由组成互不相同的两层以上构成。

[0025]

[7]根据所述[1]~[6]中任一项所述的半导体装置,其中,第一电极层之中比第二电极层的外端部向更外侧伸出的部分的至少一部分具有向所述半导体装置的外侧而膜厚减少的锥形区域。

[0026]

[8]根据所述[1]~[7]中任一项所述的半导体装置,其中,第二电极层包含选自银、铜、金和铝中的至少一种金属。

[0027]

[9]根据所述[1]~[8]中任一项所述的半导体装置,其中,第一电极层的层厚比第

二电极层的层厚更薄。

[0028]

[10]根据所述[1]~[9]中任一项所述的半导体装置,其中,进一步具有场绝缘膜,第一电极层的外端部位于所述场绝缘膜上。

[0029]

[11]根据所述[1]~[10]中任一项所述的半导体装置,其中,其为肖特基势垒二极管。

[0030]

[12]根据所述[1]~[11]中任一项所述的半导体装置,其中,其为功率器件。

[0031]

[13]一种半导体系统,具备半导体装置,其特征在于,所述半导体装置为所述[1]~[12]中任一项所述的半导体装置。

[0032]

本发明的半导体装置抑制了漏电流且为低损耗。

附图说明

[0033]

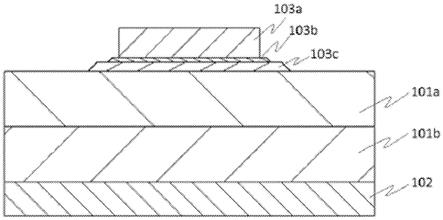

图1是示意性地示出本发明的肖特基势垒二极管(sbd)的优选的一个方式的图。

[0034]

图2是示意性地示出本发明的肖特基势垒二极管(sbd)的优选的一个方式的图。

[0035]

图3是示意性地示出本发明的肖特基势垒二极管(sbd)的优选的制造工序的图。

[0036]

图4是示意性地示出本发明的肖特基势垒二极管(sbd)的优选的一个方式的图。

[0037]

图5是在本发明的实施例中使用的雾化cvd装置的结构图。

[0038]

图6是示意性地示出电源系统的优选的一例的图。

[0039]

图7是示意性地示出系统装置的优选的一例的图。

[0040]

图8是示意性地示出电源装置的电源电路图的优选的一例的图。

[0041]

图9是示出实施例和比较例中的i-v测量的结果的图。纵轴表示电流,横轴表示电压。

具体实施方式

[0042]

本发明的半导体装置至少具备半导体层和肖特基电极,所述半导体层包含具有刚玉结构的氧化物半导体作为主成分,所述肖特基电极包含第一电极层和导电率高于第一电极层的第二电极层,其特征在于,第二电极层的外端部经由第一电极层与所述半导体层电连接,第一电极层的外端部位于比电连接的第二电极层的电连接区域的外端部更外侧的位置。这里,“电连接”可以直接接触,也可以是经由导电膜或半导体膜等接触的状态。所述电连接区域的外端部可以是第二电极层的外端部,也可以是与第二电极层内的第一电极层电连接的区域的外端部。以下,作为“所述电连接区域的外端部”的一例,举出“第二电极层的外端部”进行说明,但是本发明并不限定于这些例子。

[0043]

所述半导体层只要是包含具有刚玉结构的氧化物半导体作为主成分的半导体层则不特别限定。作为所述的具有刚玉结构的氧化物半导体,例如可以举出包含选自铝、镓、铟、铁、铬、钒、钛、铑、镍、钴和铱中的一种或两种以上的金属的金属氧化物等。在本发明中,优选地,所述氧化物半导体含有选自铝、铟和镓中的至少一种金属,更优选地,至少包含镓,最优选地,其为α-ga2o3或其混晶。此外,“主成分”是指所述的具有刚玉结构的氧化物半导体相对于所述半导体层的全部成分,优选以原子比计包含50%以上,更优选包含70%以上,进一步优选包含90%以上,也可以是100%。另外,所述半导体层的厚度并不特别限定,可以为1μm以下,也可以为1μm以上,但在本发明中,优选为10μm以上。所述半导体膜的表面积并不

特别限定,可以是1mm2以上,也可以是1mm2以下,优选为10mm2~300cm2,更优选为100mm2~100cm2。另外,所述半导体层通常是单晶,但也可以是多晶。另外,还优选地,所述半导体层为至少包含第一半导体层和第二半导体层的多层膜,在第一半导体层上设置有肖特基电极的情况下,所述半导体层为第一半导体层的载体密度小于第二半导体层的载体密度的多层膜。此外,在这种情况下,第二半导体层中通常包含掺杂剂,并且能够通过调节掺杂量,适当地设定所述半导体层的载体密度。

[0044]

优选地,所述半导体层包含掺杂剂。所述掺杂剂并不特别限定,可以是公知的掺杂剂。作为所述掺杂剂,例如可以举出锡、锗、硅、钛、锆、钒或铌等n型掺杂剂、或镁、钙、锌等p型掺杂剂等。在本发明中,所述n型掺杂剂优选为sn、ge或si。关于掺杂剂的含量,在所述半导体层的组成中,优选为0.00001原子%以上,更优选为0.00001原子%~20原子%,最优选为0.00001原子%~10原子%。更具体而言,掺杂剂的浓度通常可以是约1

×

10

16

/cm3~1

×

10

22

/cm3,另外还可以将掺杂剂的浓度例如设为约1

×

10

17

/cm3以下的低浓度。另外,进而根据本发明,还可以以约1

×

10

20

/cm3以上的高浓度含有掺杂剂。在本发明中,优选以1

×

10

17

/cm3以上的载体浓度含有。

[0045]

所述半导体层可以使用公知的方法形成。作为所述半导体层的形成方法,例如可以举出cvd法、mocvd法、movpe法、雾化cvd法、雾化/外延法、mbe法、hvpe法、脉冲生长法或ald法等。在本发明中,所述半导体层的形成方法优选为雾化cvd法或雾化/外延法。在所述的雾化cvd法或雾化/外延法中,例如通过使用图5所示的雾化cvd装置,使原料溶液雾化(雾化工序),使液滴飘浮,雾化后,将得到的雾化液滴用载气运送到基体上(运送工序),接着,在所述基体附近使所述雾化液滴产生热反应,从而在基体上层叠包含以结晶性氧化物半导体为主成分的半导体膜(成膜工序)来形成所述半导体层。

[0046]

(雾化工序)

[0047]

在雾化工序中,使所述原料溶液雾化。所述原料溶液的雾化方法只要能够雾化所述原料溶液则不特别限定,也可以是公知的方法,在本发明中,优选为使用超声波的雾化方法。由于使用超声波得到的雾化液滴的初速度为零,在空中飘浮,因此优选,由于不是像例如喷雾那样进行喷射,而是可飘浮在空间中并作为气体进行运送的雾,因此无碰撞能量导致的损伤,从而非常适合。液滴尺寸并不特别限定,可以是数毫米左右的液滴,优选为50μm以下,更优选为100nm~10μm。

[0048]

(原料溶液)

[0049]

所述原料溶液只要包含可雾化或液滴化且可形成半导体膜的原料则不特别限定,可以是无机材料,也可以是有机材料。在本发明中,所述原料优选为金属或金属化合物,更优选包含选自铝、镓、铟、铁、铬、钒、钛、铑、镍、钴和铱中的一种或两种以上的金属。

[0050]

在本发明中,作为所述原料溶液,能够适当使用使所述金属以络合物或盐的形态溶解或分散到有机溶剂或水中的物质。作为络合物的形态,例如,可以举出乙酰丙酮络合物、羰基络合物、胺络合物、氢化物络合物等。作为盐的形态,例如,可以举出有机金属盐(例如金属醋酸盐、金属草酸盐、金属柠檬酸盐等)、硫化金属盐、硝化金属盐、金属磷酸盐、卤化金属盐(例如氯化金属盐、溴化金属盐、碘化金属盐等)等。

[0051]

另外,优选地,在所述原料溶液中混合氢卤酸、氧化剂等添加剂。作为所述氢卤酸,例如可以举出氢溴酸、盐酸、氢碘酸等,其中,出于可更有效地抑制异常粒子的产生的理由,

优选为氢溴酸或氢碘酸。作为所述氧化剂,例如,可以举出过氧化氢(h2o2)、过氧化钠(na2o2)、过氧化钡(bao2)、过氧化苯甲酰((c6h5co)2o2)等过氧化物,次氯酸(hclo)、过氯酸、硝酸、臭氧水、过醋酸、硝基苯等有机过氧化物等。

[0052]

所述原料溶液中还可以包含掺杂剂。通过使原料溶液中包含掺杂剂,从而能够良好地进行掺杂。所述掺杂剂只要不阻碍本发明的目的,则不特别限定。作为所述掺杂剂,例如可以举出锡、锗、硅、钛、锆、钒或铌等n型掺杂剂,或mg、h、li、na、k、rb、cs、fr、be、ca、sr、ba、ra、mn、fe、co、ni、pd、cu、ag、au、zn、cd、hg、ti、pb、n或p等p型掺杂剂等。所述掺杂剂的含量通过使用校准线来适当设定,该校准线示出掺杂剂的原料中的浓度相对于期望的载体密度的关系。

[0053]

原料溶液的溶剂不特别限定,可以是水等无机溶剂,也可以是乙醇等有机溶剂,还可以是无机溶剂与有机溶剂的混合溶剂。在本发明中,优选地,所述溶剂包含水,更优选为水或水与乙醇的混合溶剂。

[0054]

(运送工序)

[0055]

在运送工序中,通过载气将所述雾化液滴运送到成膜室内。作为所述载气,只要不阻碍本发明的目的则不特别限定,例如可以举出氧、臭氧、氮或氩等惰性气体,或者氢气或合成气体等还原气体等作为适当的例子。另外,载气的种类可以为一种,但也可以为两种以上,还可以进一步将降低流量的稀释气体(例如10倍稀释气体等)等作为第二载气使用。另外,载气的供给部位也不仅仅有一个,也可以有两个以上。载气的流量不特别限定,优选为0.01l/分钟~20l/分钟,更优选为1l/分钟~10l/分钟。在有稀释气体的情况下,稀释气体的流量优选为0.001l/分钟~2l/分钟,更优选为0.1l/分钟~1l/分钟。

[0056]

(成膜工序)

[0057]

在成膜工序中,通过在所述基体附近使所述雾化液滴进行热反应,从而在基体上形成所述半导体膜。关于热反应,只要利用热使所述雾化液滴发生反应即可,反应条件等也是只要不阻碍本发明的目的,则并不特别限定。在本工序中,通常以溶剂的蒸发温度以上的温度进行所述热反应,优选为不过高的温度(例如1000℃)以下,更优选为650℃以下,最优选为300℃~650℃。另外,热反应只要不阻碍本发明的目的,则可以在真空下、非氧气氛下(例如,惰性气体气氛下等)、还原气体氛围下及氧气氛下中的任意氛围下进行,优选在惰性气体气氛下或氧气氛下进行。另外,还可以在大气压下、加压下及减压下的任意条件下进行,本发明中,优选在大气压下进行。另外,通过调整成膜时间,能够设定膜厚。

[0058]

(基体)

[0059]

所述基体只要能够支撑所述半导体膜,则不特别限定。所述基体的材料也是只要不阻碍本发明的目的,则不特别限定,可以是公知的基体,也可以是有机化合物,还可以是无机化合物。作为所述基体的形状可以是任何形状,对所有形状都有效,例如,可以举出平板或圆板等板状、纤维状、棒状、圆柱状、方柱状、筒状、螺旋状、球状、环状等,但在本发明中,优选为基板。基板的厚度在本发明中并不特别限定。

[0060]

所述基板为板状,如果是作为所述半导体膜的支撑体的基板就不特别限定。可以是绝缘体基板,也可以是半导体基板,还可以是金属基板或导电性基板,优选地,所述基板为绝缘体基板,另外,还优选地,是在表面具有金属膜的基板。作为所述基板,例如可以举出包含具有刚玉结构的基板材料作为主成分的基底基板、或者包含具有β-gallia结构的基板

材料作为主成分的基底基板、包含具有六方晶结构的基板材料作为主成分的基底基板等。在此,“主成分”是指具有所述特定的晶体结构的基板材料相对于基板材料的全部成分,优选以原子比计包含50%以上,更优选包含70%以上,进一步优选包含90%以上,也可以是100%。

[0061]

基板材料只要不阻碍本发明的目的,则不特别限定,可以是公知的基板材料。作为所述的具有刚玉结构的基板材料,例如,适当举出α-al2o3(蓝宝石基板)或α-ga2o3,可以举出a面蓝宝石基板、m面蓝宝石基板、r面蓝宝石基板、c面蓝宝石基板、α型氧化镓基板(a面、m面或r面)等作为更适当的例子。作为以具有β-gallia结构的基板材料为主成分的基底基板,例如,可以举出β-ga2o3基板,或者包含ga2o3和al2o3且al2o3为大于0wt%且60wt%以下的混晶体基板等。另外,作为以具有六方晶结构的基板材料为主成分的基底基板,例如,可以举出sic基板、zno基板、gan基板等。

[0062]

在本发明中,在所述成膜工序之后,还可以进行退火处理。关于退火的处理温度,只要不阻碍本发明的目的则不特别限定,通常为300℃~650℃,优选为350℃~550℃。另外,退火的处理时间通常为1分钟~48小时,优选为10分钟~24小时,更优选为30分钟~12小时。另外,关于退火处理,只要不阻碍本发明的目的,可以在任何气氛下进行。可以为非氧气氛下,也可以为氧气氛下。作为非氧气氛下,例如,可以举出惰性气体气氛下(例如,氮气氛下)或还原气体气氛下等,在本发明中,优选为惰性气体气氛下,更优选为氮气氛下。

[0063]

另外,在本发明中,可以直接在所述基体上设置所述半导体膜,也可以经由应力松弛层(例如,缓冲层、elo层等)、剥离牺牲层等其他层来设置所述半导体膜。各层的形成方法并不特别限定,可以是公知的方法,但在本发明中,优选为雾化cvd法。

[0064]

在本发明中,也可以在使用了将所述半导体膜从所述基体等剥离等的公知的方法之后,作为所述半导体层用于半导体装置,也可以直接作为所述半导体层用于半导体装置。

[0065]

第一电极层如果是具有导电性且导电率低于第二电极层的电极层,只要不阻碍本发明的目的,则不特别限定。第一电极层的构成材料可以是导电性无机材料,也可以是导电性有机材料。在本发明中,第一电极层的材料优选为金属。作为所述金属,优选例如可举出选自元素周期表第4族~第10族中的至少一种金属等。作为元素周期表第4族的金属,例如可以举出钛(ti)、锆(zr)、铪(hf)等。作为元素周期表第5族的金属,例如可以举出钒(v)、铌(nb)、钽(ta)等。作为元素周期表第6族的金属,例如可以举出铬(cr)、钼(mo)和钨(w)等。作为元素周期表第7族的金属,例如可以举出锰(mn)、锝(tc)、铼(re)等。作为元素周期表第8族的金属,例如可以举出铁(fe)、钌(ru)、锇(os)等。作为元素周期表第9族的金属,例如可以举出钴(co)、铑(rh)、铱(ir)等。作为元素周期表第10族的金属,例如可以举出镍(ni)、钯(pd)、铂(pt)等。在本发明中,优选地,第一电极层包含选自元素周期表第4族和第9族中的至少一种金属,更优选地,包含元素周期表第9族金属。第一电极层的层厚并不特别限定,优选为0.1nm~10μm,更优选为5nm~500nm,最优选为10nm~200nm。此外,在本发明中,优选地,第一电极层的层厚比第二电极层的层厚更薄。另外,在本发明中,第一电极层优选为由组成互不相同的两层以上构成。通过将第一电极层设为这样的优选结构,不仅能够得到肖特基特性更优异的半导体装置,还能够更好地表现出漏电流的抑制效果。

[0066]

第二电极层如果是具有导电性且导电率高于第一电极层的电极层,只要不阻碍本发明的目的,则不特别限定。第二电极层的构成材料可以是导电性无机材料,也可以是导电

性有机材料。在本发明中,第二电极层的材料优选为金属。作为所述金属,优选例如可举出选自元素周期表第8族~第13族中的至少一种金属等。作为元素周期表第8族~第10族的金属,可以举出在第一电极层的说明中作为元素周期表第8族~第10族的金属分别示例的金属等。作为元素周期表第11族的金属,例如可以举出铜(cu)、银(ag)、金(au)等。作为元素周期表第12族的金属,例如可以举出锌(zn)、镉(cd)等。另外,作为元素周期表第13族的金属,例如可以举出铝(al)、镓(ga)、铟(in)等。在本发明中,第二电极层优选包含选自元素周期表第11族和第13族金属中的至少一种金属,更优选包含选自银、铜、金和铝中的至少一种金属。此外,第二电极层的层厚并不特别限定,优选为1nm~500μm,更优选为10nm~100μm,最优选为0.5μm~10μm。

[0067]

第一电极层或第二电极层的形成方法并不特别限定,可以是公知的方法。作为第一电极层或第二电极层的形成方法,具体而言,例如可以举出干法和湿法等。作为干法,例如可以举出溅射、真空蒸镀、cvd等。作为湿法,例如可以举出丝网印刷或模具涂层等。

[0068]

如果第一电极层的外端部位于比第二电极层的外端部更外侧的位置,则不特别限定,但在本发明中,第一电极层的外端部与第二电极层的外端部之间的距离为1μm以上,能够更加抑制漏电流,因此优选。另外,在本发明中,第一电极层之中比第二电极层的外端部向更外侧伸出的部分(以下也称为“伸出部分”)的至少一部分具有向所述半导体装置的外侧而膜厚减少的锥形区域,也能够使所述半导体装置的耐压性更优异,因此优选。另外,通过组合这样的优选电极结构与上述的优选的所述半导体层的构成材料,能够得到更好地抑制了漏电流且损耗更低的半导体装置。此外,所述锥形区域中的膜厚的减少率等并不特别限定,为了方便,也可以说在从内侧的膜厚和外侧的膜厚的任意两点向所述半导体装置的外侧而膜厚减少的情况下,作为所述锥形区域。

[0069]

另外,在本发明中,还优选在所述半导体层上进一步具有场绝缘膜,在这种情况下,第一电极层的外端部位于所述场绝缘膜上,会在半导体层内更良好地形成耗尽层,因此更优选。所述场绝缘膜的构成材料只要不阻碍本发明的目的,则不特别限定,可以是公知的材料。作为所述场绝缘膜,例如可以举出sio2膜、多晶硅膜、磷添加sio2膜(psg膜)、硼添加sio2膜、磷-硼添加sio2膜(bpsg膜)等。作为所述场绝缘膜的形成方法,例如可以举出cvd法、大气压cvd法、等离子体cvd法、雾化cvd法、热氧化法等。在本发明中,所述场绝缘膜的形成方法优选为雾化cvd法或大气压cvd法。

[0070]

下面,使用附图来更详细地说明本发明的优选实施方式,但本发明不限于这些实施方式。

[0071]

图1示出作为本发明的优选的实施方式之一的肖特基势垒二极管(sbd)的主要部分。图1的sbd具备:欧姆电极102、n-型半导体层101a、n+型半导体层101b、肖特基电极103。另外,肖特基电极103包含金属层103a、金属层103b和金属层103c。在图1的半导体装置中,作为第一电极层的金属层103b和/或金属层103c的外端部位于比作为第二电极层的金属层103a的外端部更外侧的位置,因此能够更好地抑制漏电流。此外,进而在金属层103b和/或金属层103c中,比金属层103a的外端部向更外侧伸出的部分具有向半导体装置的外侧而膜厚减少的锥形区域,因此成为耐压性更加优异的结构。

[0072]

作为金属层103a的构成材料,例如可以举出作为第二电极层的构成材料示例的上述金属等。另外,作为金属层103b和金属层103c的构成材料,例如可以举出作为第一电极层

的构成材料示例的上述金属等。图1的各层的形成方法只要不阻碍本发明的目的,则不特别限定,可以是公知的方法。例如可以举出通过真空蒸镀法、cvd法、溅射法、各种涂覆技术成膜后,通过光刻法进行图案化的方法、或者使用印刷技术等直接进行图案化的方法等。

[0073]

图2示出作为本发明的其他优选的实施方式之一的肖特基势垒二极管(sbd)的主要部分。图2的sbd进一步具有场绝缘膜104,金属层103b和/或金属层103c的外端部位于场绝缘膜104上这点与图1的sbd不同。通过采用这样的结构,能够使半导体装置的耐压特性更优异。

[0074]

图2的各层的形成方法只要不阻碍本发明的目的,则不特别限定,可以是公知的方法。例如可以举出通过真空蒸镀法、cvd法、溅射法、各种涂覆技术成膜后,通过光刻法进行图案化的方法、或者使用印刷技术等直接进行图案化的方法等。

[0075]

以下,使用制造图2的半导体装置的优选例子,更详细地说明本发明。

[0076]

图3的(a)示出如下的层叠体:在欧姆电极102上按顺序形成有n+型半导体层101b和n-型半导体层101a,在n-型半导体层上形成有场绝缘膜104。场绝缘膜104的形成方法只要不阻碍本发明的目的,则不特别限定。作为场绝缘膜104的形成方法,例如可以举出溅射法、真空蒸镀法、涂布法、cvd法、大气压cvd法、等离子体cvd法、雾化cvd法、热氧化法等,在本发明中,优选为雾化cvd法或大气压cvd法。另外,在场绝缘膜4上形成有用于第一电极层的开口部,使得所述n-型半导体层101a的至少一部分露出。所述开口部的形成方法并不特别限定,可以是公知的蚀刻方法。此外,在场绝缘膜104中形成有从所述半导体装置的外侧向内侧而膜厚减少的锥形部。锥形部的形成方法只要不阻碍本发明的目的,则不特别限定,可以是公知的方法。

[0077]

接着,在图3的(a)的层叠体上,使用所述干法或所述湿法,形成金属层103a、103b和103c,得到图3的(b)的层叠体。然后,通过使用公知的蚀刻技术去除金属层103a、金属层103b和金属层103c中的多余部分,得到图3的(c)的层叠体。此外,在该蚀刻中,例如,优选地,通过在使抗蚀剂后退的同时进行蚀刻来形成第一电极层的外端部具有锥形形状。如上所述得到的半导体装置成为在抑制漏电流的同时具有优异的耐压性的结构。

[0078]

图4示出作为本发明的其他优选的实施方式之一的肖特基势垒二极管(sbd)的主要部分。图4的sbd在第一金属层的外端部周边进一步设置有保护金属层105,这点与图2的sbd不同。保护金属层105被设置为至少覆盖场绝缘膜104的端部。保护金属层的构成材料并不特别限定,可以与作为上述金属层的材料示例的金属相同。通过采用这样的结构,能够更有效地进行金属层103a、金属层103b和金属层103c的形成,能够在进一步提高耐压特性的同时,使半导体装置的可靠性更优异。

[0079]

图4的各层的形成方法只要不阻碍本发明的目的,则不特别限定,可以是公知的方法。例如可以举出通过真空蒸镀法、cvd法、溅射法、各种涂覆技术成膜后,通过光刻法进行图案化的方法、或者使用印刷技术等直接进行图案化的方法等。

[0080]

所述半导体装置尤其对功率器件有用。作为所述半导体装置,例如可以举出二极管(例如,pn二极管、肖特基势垒二极管、结势垒肖特基二极管等)或晶体管(例如,mosfet、mesfet等)等,其中优选二极管,更优选肖特基势垒二极管(sbd)。

[0081]

除了上述事项以外,本发明的半导体装置进一步使用公知的方法,优选用作功率模块、逆变器或转换器,这些半导体装置也包含在本发明中。另外,本发明的半导体装置进

一步优选用于例如使用电源装置的半导体系统等。所述电源装置通过使用公知的方法连接到布线图案等,从而能够从所述半导体装置或作为所述半导体装置来制作。图6示出电源系统的例子。图6使用多个所述电源装置和控制电路构成电源系统。如图7所示,所述电源系统能够与电子电路组合而用于系统装置。此外,图8示出电源装置的电源电路图的一例。图8示出由功率电路和控制电路构成的电源装置的电源电路,通过逆变器(由mosfet:a~d构成)将dc电压用高频转换至ac后,用变压器实施绝缘及变压,用整流mosfet(a~b

′

)整流后,通过dcl(平滑用线圈l1、l2)和电容器进行平滑,输出直流电压。此时,通过电压比较器将输出电压与基准电压进行比较,通过pwm控制电路来控制逆变器及整流mosfet,以成为期望的输出电压。

[0082]

实施例

[0083]

以下,对本发明的实施例进行说明,本发明并不限定于这些。

[0084]

(实施例1)

[0085]

1.n-型半导体层的形成

[0086]

1-1.成膜装置

[0087]

使用图5,对在本实施例中使用的雾化cvd装置1进行说明。雾化cvd装置1具备:用于供给载气的载气源2a;用于调节从载气源2a送出的载气的流量的流量调节阀3a;用于供给载气(稀释)的载气(稀释)源2b;用于调节从载气(稀释)源2b送出的载气(稀释)的流量的流量调节阀3b;用于收容原料溶液4a的雾化发生源4;用于装入水5a的容器5;安装在容器5的底面上的超声波振子6;成膜室7;连接从雾化发生源4到成膜室7的供给管9;设置在成膜室7内的热板8;排出热反应后的雾、液滴和废气的排出口11。此外,在热板8上设置有基板10。

[0088]

1-2.原料溶液的制作

[0089]

在0.1m的溴化镓水溶液中混合溴化锡,以锡与镓的原子比为1:0.0008的方式调制水溶液,此时,以体积比计含有20%的氢溴酸,将该水溶液作为原料溶液。

[0090]

1-3.成膜准备

[0091]

将由上述1-2.得到的原料溶液4a收容在雾化发生源4内。接着,在热板8上设置m面蓝宝石基板作为基板10,在该m面蓝宝石基板的表面形成有未掺杂α-ga2o3层作为缓冲层,通过使热板8工作而将成膜室7内的温度升温至470℃。接着,打开流量调节阀3a、3b,从作为载气源的载气供给源2a、2b向成膜室7内供给载气,在利用载气充分置换成膜室7的气氛之后,将载气的流量调节为1.2l/分钟,将载气(稀释)的流量调节为1.0l/分钟。此外,使用氮作为载气。

[0092]

1-4.结晶性氧化物半导体膜的形成

[0093]

接着,通过使超声波振子6以2.4mhz振动,并且使该振动通过水5a传播到原料溶液24a,从而使原料溶液4a雾化并生成雾4b。该雾4b借助载气通过供给管9内导入到成膜室7内,在大气压下、615℃,在成膜室7内雾进行热反应,在基板10上形成膜。此外,成膜时间为6小时。

[0094]

1-5.评价

[0095]

使用xrd衍射装置,对通过上述1-4.得到的膜的相进行鉴定,其结果得到的膜为α-ga2o3。

[0096]

2.n+型半导体层的形成

[0097]

作为原料溶液,在0.1m的溴化镓水溶液中混合溴化锡,以锡相对于镓的原子比为1:0.24的方式调制水溶液,此时,除了使用以体积比计含有20%的氢溴酸的水溶液、以及将成膜时间设为2小时以外,其他与上述1.同样,形成结晶性氧化物半导体膜。关于得到的膜,使用xrd衍射装置,对膜的相进行鉴定,其结果得到的膜为α-ga2o3。

[0098]

3.欧姆电极的形成

[0099]

在通过上述2.得到的层叠体的n+型半导体层上,分别通过溅射来层叠ti层和au层。此外,ti层的厚度为70nm,au层的厚度为30nm。

[0100]

4.基板去除

[0101]

在通过上述3.得到的层叠体的欧姆电极上,暂时接合临时晶圆,然后使用磨床和cmp装置对基板10进行研磨,去除上述蓝宝石基板和缓冲层。

[0102]

5.绝缘膜的形成

[0103]

在通过上述4.得到的层叠体的n-型半导体层上,利用等离子体cvd形成sio2膜。然后,通过蚀刻,在sio2膜上形成开口部,使得所述n-型半导体层的一部分露出。

[0104]

6.肖特基电极的形成

[0105]

在通过上述5.得到的层叠体的n-型半导体层上,通过eb(电子束)蒸镀,分别形成co膜(厚度100nm)、ti膜(50nm)和al膜(厚度5μm),作为肖特基电极。然后,通过蚀刻,去除co膜、ti膜和al膜。通过sem观察得到的肖特基电极的外端部,其结果确认了在al膜的外周,ti膜和co膜向外侧伸出约10μm,ti膜和co膜的外端部位于比al膜的外端部更外侧的位置。此外,ti膜和co膜的外端部与n-型半导体层接触。另外,伸出的co膜的薄膜电阻为1.3ω。

[0106]

(比较例1)

[0107]

以al膜、co膜和ti膜的外端部位于sio2膜上(作为第二电极层的al膜的外端部并未与半导体层电连接的状态),且使al膜、ti膜和co膜的外端部位于大致相同的位置的方式来进行肖特基电极的形成,除此以外与实施例1同样地制作sbd。

[0108]

(实施例2)

[0109]

以如下方式形成n-半导体层:作为原料溶液,使用在0.1m的溴化镓水溶液中,以体积比计含有10%的氢溴酸的水溶液,以及al膜经由co膜和ti膜与n-型半导体层上电连接,且co膜和ti膜的外端部位于sio2膜上的方式进行肖特基电极的形成,除上述以外,与实施例1同样地制作sbd。关于得到的sbd,实施i-v测量,结果是具有与实施例1的sbd同等的漏电流降低效果。

[0110]

(i-v测量)

[0111]

关于由实施例1、比较例1和实施例2得到的sbd,实施i-v测量。图9示出实施例2和比较例1的结果。从图9可以明显看出,与比较例1的sbd相比,实施例2的sbd大幅降低了漏电流。另外,实施例1的sbd具有与实施例2的sbd同等的漏电流抑制效果。

[0112]

产业上的可利用性

[0113]

本发明的半导体装置能够在半导体(例如,化合物半导体电子器件等)、电子零件及电气设备零件、光学及电子照片相关装置、工业部件等所有领域中使用,尤其对功率器件有用。

[0114]

符号说明

[0115]1ꢀꢀ

成膜装置(雾化cvd装置)

[0116]

2a 载气源

[0117]

2b 载气(稀释)源

[0118]

3a 流量调节阀

[0119]

3b 流量调节阀

[0120]4ꢀꢀ

雾化发生源

[0121]

4a 原料溶液

[0122]

4b 原料微粒

[0123]5ꢀꢀ

容器

[0124]

5a 水

[0125]6ꢀꢀ

超声波振子

[0126]7ꢀꢀ

成膜室

[0127]8ꢀꢀ

热板

[0128]9ꢀꢀ

供给管

[0129]

10 基板

[0130]

101a n-型半导体层

[0131]

101b n+型半导体层

[0132]

102

ꢀꢀ

欧姆电极

[0133]

103

ꢀꢀ

肖特基电极

[0134]

103a 金属层

[0135]

103b 金属层

[0136]

103c 金属层

[0137]

104

ꢀꢀ

绝缘膜(场绝缘膜)

[0138]

105

ꢀꢀ

保护金属层

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1