倍增型图像传感器的制作方法

1.本公开涉及倍增型图像传感器。

背景技术:

2.作为倍增型的图像传感器,专利文献1中记载有具有形成有雪崩倍增区域的半导体层的固体摄像元件。在专利文献1所记载的固体摄像元件的一例中,设置于半导体层的多个像素各自具有p型的半导体区域、形成于p型的半导体区域内且与p型的半导体区域的一部分一同形成雪崩倍增区域的n型的半导体区域、和形成于p型的半导体区域中的p-型半导体区域内且构成像素电路的一部分的p型的阱区域,n型的半导体区域按多个像素中的每一个进行分割。

3.现有技术文献

4.专利文献

5.专利文献1:国际公开2017/043068号

技术实现要素:

6.发明要解决的技术问题

7.但是,在专利文献1所记载的固体摄像元件的一例中,为了在对p型的半导体区域施加电压以对雪崩倍增区域施加击穿电压以上的电压时确保像素电路的耐压性,需要将相邻的n型的半导体区域间的区域(像素间分离区域)耗尽,在实现性上估计难易度高。

8.本公开的目的在于提供一种倍增型图像传感器,能够确保像素电路的耐压性。

9.用于解决问题的技术方案

10.本公开的一方面的倍增型图像传感器包括:半导体层,其具有第1表面和与第1表面相反的一侧的第2表面,包含以沿着第1表面的方式配置的多个像素;和设置于第2表面的配线层,多个像素各自具有:第1导电型的第1半导体区域;相对于第1半导体区域的至少一部分形成于第2表面侧,按多个像素中的每一个分割出的第2导电型的第2半导体区域;和以与第1半导体区域分离的方式形成在第2半导体区域内,构成像素电路的一部分的第1导电型的阱区域,第1半导体区域的至少一部分和第2半导体区域的至少一部分形成雪崩倍增区域。

11.在该倍增型图像传感器中,在多个像素中的每一个中,由第1导电型的第1半导体区域的至少一部分和按多个像素中的每一个分割出的第2导电型的第2半导体区域的至少一部分形成雪崩倍增区域,构成像素电路的一部分的第1导电型的阱区域以与第1导电型的第1半导体区域分离的方式形成在第2导电型的第2半导体区域内。由此,在对第1半导体区域施加电压以对雪崩倍增区域施加击穿电压以上的电压时,像素电路不易受到该电压的影响。因此,根据该倍增型图像传感器,能够确保像素电路的耐压性。

12.在本公开的一方面的倍增型图像传感器中,也可以第2半导体区域是由第1半导体区域中的除一部分外的部分按多个像素中的每一个分割的。由此,能够抑制相邻的像素间

发生串扰。

13.在本公开的一方面的倍增型图像传感器中,也可以第2半导体区域是由以在第2表面侧开口的方式形成于半导体层的沟槽按多个像素中的每一个分割的。由此,能够抑制相邻的像素间发生串扰。

14.在本公开的一方面的倍增型图像传感器中,也可以阱区域以离开沟槽的方式形成在第2半导体区域内。由此,能够实现确保像素电路的耐压性的可靠化。

15.在本公开的一方面的倍增型图像传感器中,也可以阱区域以与沟槽接触的方式形成在第2半导体区域内。由此,能够实现多个像素的配置的高密度化即作为图像传感器的开口率的提高。

16.在本公开的一方面的倍增型图像传感器中,也可以第2半导体区域在从与第1表面垂直的方向观察时的第2半导体区域的中央部与配线层电连接。由此,能够将多个像素各自产生的电荷平衡地送到配线层。

17.在本公开的一方面的倍增型图像传感器中,也可以多个像素各自具有在第2半导体区域内相互分割出的多个阱区域作为阱区域。由此,能够将多个阱区域各自的独立的电压施加于像素电路。

18.发明效果

19.根据本公开,能够提供一种倍增型图像传感器,能够确保像素电路的耐压性。

附图说明

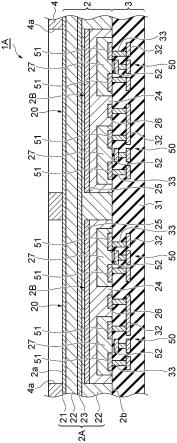

20.图1是第1实施方式的倍增型图像传感器的一部分的截面图。

21.图2是图1所示的倍增型图像传感器的半导体层的一部分的仰视图。

22.图3是图1所示的倍增型图像传感器的一部分的俯视图。

23.图4是第2实施方式的倍增型图像传感器的一部分的截面图。

24.图5是图4所示的倍增型图像传感器的半导体层的一部分的仰视图。

25.图6是第3实施方式的倍增型图像传感器的一部分的截面图。

26.图7是图6所示的倍增型图像传感器的半导体层的一部分的仰视图。

27.图8是第1变形例的倍增型图像传感器的半导体层的一部分的仰视图。

28.图9是第2变形例的倍增型图像传感器的一部分的截面图。

29.图10是图9所示的倍增型图像传感器的半导体层的一部分的仰视图。

30.图11是第3变形例的倍增型图像传感器的一部分的截面图。

31.图12是图11所示的倍增型图像传感器的半导体层的一部分的仰视图。

具体实施方式

32.下面,参照附图对本公开的实施方式进行详细说明。此外,在各图中对相同或相当部分标注相同的标号,省略重复的说明。

33.[第1实施方式]

[0034]

如图1和图2所示,倍增型图像传感器1a具有半导体层2。半导体层2具有第1表面2a和与第1表面2a相反侧的第2表面2b。半导体层2包含以沿着第1表面2a的方式配置的多个像素20。多个像素20例如呈矩阵状配置。

[0035]

各像素20具有第1导电型的第1半导体区域2a和第2导电型的第2半导体区域2b。第1半导体区域2a由p+型半导体区域21、p-型半导体区域22和p型半导体区域23构成。第2半导体区域2b由n-型半导体区域24、n型半导体区域25和n型半导体区域26构成。

[0036]

p+型半导体区域21为沿着第1表面2a的层状的区域,遍及多个像素20地形成(即在半导体层2中连续)。作为一例,p+型半导体区域21的杂质浓度为1

×

10

18

cm-3

以上,p+型半导体区域21的厚度为1.0μm左右。

[0037]

p-型半导体区域22为从p+型半导体区域21到第2表面2b的区域,遍及多个像素20地形成。作为一例,p-型半导体区域22的杂质浓度为1

×

10

16

cm-3

以下,p-型半导体区域22的厚度为10μm左右。

[0038]

p型半导体区域23为在p-型半导体区域22内与第1表面2a大致平行地扩展的层状的区域,遍及多个像素20地形成。作为一例,p型半导体区域23的杂质浓度为5

×

10

16

cm-3

以上且1

×

10

18

cm-3

以下,p型半导体区域23的厚度为1.0μm左右。

[0039]

n-型半导体区域24为在p-型半导体区域22中位于比p型半导体区域23靠第2表面2b侧的部分内到达第2表面2b的区域,按每个像素20进行分割。n-型半导体区域24的杂质浓度为1

×

10

16

cm-3

以下,n-型半导体区域24的厚度为1.0μm左右。

[0040]

n型半导体区域25为n-型半导体区域24中的沿着第1表面2a侧的端部的层状的区域,按每个像素20进行分割。n型半导体区域25的杂质浓度为5

×

10

16

cm-3

以上且1

×

10

18

cm-3

以下,n型半导体区域25的厚度为1.0μm左右。

[0041]

n型半导体区域26为在从与第1表面2a垂直的方向观察时的n-型半导体区域24的中央部沿着第2表面2b的区域。n型半导体区域26的杂质浓度为1

×

10

16

cm-3

以上,n型半导体区域26的厚度为0.5μm左右。

[0042]

在半导体层2中,第2半导体区域2b相对于第1半导体区域2a的一部分形成于第2表面2b侧,且按每个像素20进行分割。第2半导体区域2b被第1半导体区域2a的另一部分按每个像素20进行分割。具体而言,在相邻的像素20中,在一像素20的第2半导体区域2b和另一像素20的第2半导体区域2b之间配置有p-型半导体区域22的一部分(p-型半导体区域22中除从与第1表面2a垂直的方向观察时与n型半导体区域25重叠的部分外的部分)。

[0043]

在各像素20中,由p-型半导体区域22和p型半导体区域23中从与第1表面2a垂直的方向观察时与n型半导体区域25重叠的部分、以及n型半导体区域25形成光电转换区域。另外,在各像素20中,由p型半导体区域23中从与第1表面2a垂直的方向观察时与n型半导体区域25重叠的部分、n型半导体区域25、和p-型半导体区域22中它们之间的部分形成雪崩倍增区域。即,由第1半导体区域2a的一部分和第2半导体区域2b的一部分形成雪崩倍增区域。雪崩倍增区域为具有使电荷雪崩倍增的功能的区域,且为在对形成于雪崩倍增区域的pn结施加规定值的反向偏压时可产生3

×

105~4

×

105v/cm的电场强度的区域。

[0044]

各像素20具有p型阱区域27作为第1导电型的阱区域。p型阱区域27为在n-型半导体区域24内到达第2表面2b的区域,除第2表面2b侧外均被n-型半导体区域24覆盖。即,p型阱区域27以与第1半导体区域2a分离的方式(即以与第1半导体区域2a物理分离且电分离的方式)形成于第2半导体区域2b内。在本实施方式中,p型阱区域27在从与第1表面2a垂直的方向观察时以包围n型半导体区域26的方式呈环状延伸。

[0045]

p型阱区域27构成多个像素电路50的一部分。各像素电路50为具有形成于p型阱区

域27内的一对沟道区域(源极区域和漏极区域)51和栅极电极52的n型的mosfet(metal-oxide-semiconductor field-effect transistor)。除用于经由n型半导体区域26读取流入到n-型半导体区域24的信号电荷的晶体管外,各像素电路50还构成放大用的晶体管、复位用的晶体管等。

[0046]

作为一例,以上那样构成的半导体层2如下进行制造。首先,通过外延生长法,在成为p+型半导体区域21的基板上形成p-型半导体区域22。接着,通过离子注入法,在p-型半导体区域22内形成p型半导体区域23。接着,通过基于光刻的图案形成和离子注入法等,在p-型半导体区域22内形成多个n-型半导体区域24和多个n型半导体区域25。接着,通过基于光刻的图案形成和离子注入法等,在各n-型半导体区域24内形成n型半导体区域26和p型阱区域27。接着,通过基于光刻的图案形成和离子注入法等,在各p型阱区域27内形成多个沟道区域51。最后,通过研磨将基板薄型化,形成p+型半导体区域21。此外,p-型半导体区域22和p型半导体区域23也可以通过外延生长法形成于成为p+型半导体区域21的基板上。

[0047]

倍增型图像传感器1a还具有配线层3。配线层3设置于半导体层2的第2表面2b。配线层3具有绝缘层31、多个配线32、和多个接触栓33。多个配线32和多个接触栓33形成于绝缘层31内。n型半导体区域26经由接触栓33与对应的配线32电连接。即,第2半导体区域2b在从与第1表面2a垂直的方向观察时的第2半导体区域2b的中央部与配线层3电连接。像素电路50的各部经由接触栓33与对应的配线32电连接。各配线32例如与倍增型图像传感器1a的cmos读取电路部电连接。

[0048]

倍增型图像传感器1a还具有电极层4。如图1和图3所示,电极层4设置于半导体层2的第1表面2a。电极层4与p+型半导体区域21电连接。电极层4具有多个开口4a。各开口4a在从与第1表面2a垂直的方向观察时与各像素20的n型半导体区域25重叠。电极层4例如由金属构成,以形成多个开口4a的方式例如呈格子状延伸。各开口4a作为各像素20的光入射开口发挥作用。

[0049]

以上那样构成的倍增型图像传感器1a如下进行动作。即,如果经由电极层4对p+型半导体区域21施加电压以对形成于雪崩倍增区域的pn结施加规定值的反向偏压(即以对雪崩倍增区域施加击穿电压以上的电压),则在各像素20的雪崩倍增区域产生3

×

105~4

×

105v/cm的电场强度。在该状态下,如果经由电极层4的各开口4a将光入射到各像素20的光电转换区域,则在各像素20中,通过光吸收而产生的电荷被雪崩倍增,经倍增的信号电荷流入到n-型半导体区域24而被多个像素电路50读取。

[0050]

如以上所说明,在倍增型图像传感器1a中,在各像素20中,由p型的第1半导体区域2a的一部分和按每个像素20分割出的n型的第2半导体区域2b的一部分形成雪崩倍增区域,构成多个像素电路50的一部分的p型阱区域27以与p型的第1半导体区域2a分离的方式形成于n型的第2半导体区域2b内。由此,在对第1半导体区域2a施加电压以对雪崩倍增区域施加击穿电压以上的电压时,各像素电路50不易受到该电压的影响。因此,根据倍增型图像传感器1a,能够确保各像素电路50的耐压性。

[0051]

另外,在倍增型图像传感器1a中,第2半导体区域2b是由第1半导体区域2a的另一部分按每个像素20分割的。由此,能够抑制相邻的像素20间发生串扰。

[0052]

另外,在倍增型图像传感器1a中,第2半导体区域2b在从与第1表面2a垂直的方向观察时的第2半导体区域2b的中央部与配线层3电连接。由此,能够将各像素20产生的电荷

平衡地送到配线层3。

[0053]

[第2实施方式]

[0054]

如图4和图5所示,在第2半导体区域2b由沟槽60按每个像素20分割这一点上,倍增型图像传感器1b与上述的倍增型图像传感器1a不同。在倍增型图像传感器1b中,沟槽60以在第2表面2b侧开口的方式形成于半导体层2。沟槽60在从与第1表面2a垂直的方向观察时以穿过相邻的像素20之间的方式例如呈格子状延伸。沟槽60具有沿着内表面形成的绝缘膜61和配置于内部的金属部件62。此外,也可以代替金属部件62,将绝缘部件等配置于沟槽60内。

[0055]

在倍增型图像传感器1b中,沟槽60的底面位于比p型半导体区域23靠第1表面2a侧,从而第2半导体区域2b(具体而言为n-型半导体区域24和n型半导体区域25)按每个像素20进行分割。沟槽60的底面的位置只要为至少将第2半导体区域2b按每个像素20分割的位置即可,例如也可以不到达p型半导体区域23。p型阱区域27以离开沟槽60的方式形成于第2半导体区域2b内(具体而言为n-型半导体区域24内)。p型阱区域27除第2表面2b侧外均被n-型半导体区域24覆盖。

[0056]

在倍增型图像传感器1b中,与上述的倍增型图像传感器1a同样,在各像素20中,由p型的第1半导体区域2a的一部分和按每个像素20分割出的n型的第2半导体区域2b的一部分形成雪崩倍增区域,构成多个像素电路50的一部分的p型阱区域27以与p型的第1半导体区域2a分离的方式形成于n型的第2半导体区域2b内。由此,在对第1半导体区域2a施加电压以对雪崩倍增区域施加击穿电压以上的电压时,各像素电路50不易受到该电压的影响。因此,根据倍增型图像传感器1b,能够确保各像素电路50的耐压性。

[0057]

另外,在倍增型图像传感器1b中,第2半导体区域2b由以在第2表面2b侧开口的方式形成于半导体层2的沟槽60按每个像素20进行分割。由此,能够抑制相邻的像素20间发生串扰。

[0058]

另外,在倍增型图像传感器1b中,p型阱区域27以离开沟槽60的方式形成于第2半导体区域2b内。由此,能够实现确保多个像素电路50的耐压性的可靠化。

[0059]

[第3实施方式]

[0060]

如图6和图7所示,在p型阱区域27以与沟槽60接触的方式形成于第2半导体区域2b内这一点上,倍增型图像传感器1c与上述的倍增型图像传感器1b不同。在倍增型图像传感器1c中,p型阱区域27以与沟槽60接触的方式形成于n-型半导体区域24内。p型阱区域27除第2表面2b侧外均被n-型半导体区域24和沟槽60覆盖。

[0061]

在倍增型图像传感器1c中,与上述的倍增型图像传感器1a同样,在各像素20中,由p型的第1半导体区域2a的一部分和按每个像素20分割出的n型的第2半导体区域2b的一部分形成雪崩倍增区域,构成多个像素电路50的一部分的p型阱区域27以与p型的第1半导体区域2a分离的方式形成于n型的第2半导体区域2b内。由此,在对第1半导体区域2a施加电压以对雪崩倍增区域施加击穿电压以上的电压时,各像素电路50不易受到该电压的影响。因此,根据倍增型图像传感器1c,能够确保各像素电路50的耐压性。

[0062]

另外,在倍增型图像传感器1c中,与上述的倍增型图像传感器1b同样,第2半导体区域2b由以在第2表面2b侧开口的方式形成于半导体层2的沟槽60按每个像素20进行分割。由此,能够抑制相邻的像素20间发生串扰。

[0063]

另外,在倍增型图像传感器1c中,p型阱区域27以与沟槽60接触的方式形成于第2半导体区域2b内。由此,能够实现多个像素20的配置的高密度化即作为图像传感器的开口率的提高。

[0064]

[变形例]

[0065]

本公开不限定于上述的第1实施方式~第3实施方式。例如,如图8所示,各像素20也可以具有在第2半导体区域2b内相互分割出的多个p型阱区域27。在图8所示的例子中,多个p型阱区域27形成于n-型半导体区域24内,各p型阱区域27构成像素电路50。由此,能够将各p型阱区域27中独立的电压施加于像素电路50。

[0066]

另外,如图9和图10所示,通过在p型阱区域27内形成n型阱区域28,p型阱区域27也可以构成像素电路50的一部分。在图9和图10所示的例子中,一像素电路50为具有形成于p型阱区域27内的一对沟道区域(源极区域和漏极区域)51和栅极电极52的n型的mosfet,另一像素电路50为具有形成于n型阱区域28内的一对沟道区域(源极区域和漏极区域)53和栅极电极52的p型的mosfet。

[0067]

另外,如图11和图12所示,在各像素20中,第2半导体区域2b也可以在从与第1表面2a垂直的方向观察时的第2半导体区域2b的端部与配线层3电连接。在图11和图12所示的例子中,在从与第1表面2a垂直的方向观察时,形成于n-型半导体区域24内的p型阱区域27不具有孔,n型半导体区域26位于n-型半导体区域24的端部。

[0068]

另外,电极层4也可以以包围多个像素20的方式呈框状形成于p+型半导体区域21上。另外,电极层4也可以由具有导电性和透光性的材料(例如ito等)呈层状形成于p+型半导体区域21上。另外,也可以取代电极层4,经由从沟槽60内的金属部件62或半导体层2的第2表面2b延伸到第1表面2a侧的贯通电极对第1半导体区域2a施加电压。

[0069]

另外,在半导体层2上未形成n型半导体区域25,在各像素20中,也可以由p型半导体区域23中从与第1表面2a垂直的方向观察时与n-型半导体区域24重叠的部分、n-型半导体区域24中的第1表面2a侧的端部、和p-型半导体区域22中它们之间的部分形成雪崩倍增区域。另外,像素电路50不限定于mosfet,也可以为jfet(junction field-effect transistor)、双极型晶体管等。另外,p型和n型的各导电型也可以与上述相反。即,也可以为,第1导电型为n型,第2导电型为p型。另外,多个像素20也可以以沿着半导体层2的第1表面2a的方式一维地配置。

[0070]

附图标记说明

[0071]

1a、1b、1c

…

倍增型图像传感器

[0072]2…

半导体层

[0073]

2a

…

第1表面

[0074]

2b

…

第2表面

[0075]

2a

…

第1半导体区域

[0076]

2b

…

第2半导体区域

[0077]3…

配线层

[0078]

20

…

像素

[0079]

27

…

p型阱区域(阱区域)

[0080]

50

…

像素电路

[0081]

60

…

沟槽(trench)。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1