高电子迁移率晶体管及其制作方法与流程

1.本发明涉及半导体技术领域,特别是涉及一种高电子迁移率晶体管(high electron mobility transistor,hemt)结构及其制作方法。

背景技术:

2.高电子迁移率晶体管(high electron mobility transistor,hemt)为一种新兴的场效晶体管,其主要包括由多层不同半导体材料堆叠所构成的异质结构(heterostructure),通过半导体材料的选择可在异质接面(heterojunction)附近区域形成二维电子气层(two dimensional electron gas,2deg)作为电流的通道区,可获得高切换速度及响应频率,特别适合应用在功率转换器、低噪声放大器、射频(rf)或毫米波(mmw)等技术领域中。

3.为了符合高压、高频及更低功耗的应用,如何进一步降低高电子迁移率晶体管的漏电流并提升击穿电压及输出功率,以获得改善的效能,为本领域积极研究的课题。

技术实现要素:

4.为达上述目的,本发明提供了一种高电子迁移率晶体管及其制作方法,其主要于栅极结构和漏极结构之间设置包括一基部及自基部下表面往通道层方向延伸的多个凸出部的一导电板结构,可调整其附近区域的电场强度,特别是可降低栅极结构边缘的峰值电场,获得降低的栅极漏电流及提高的击穿电压。

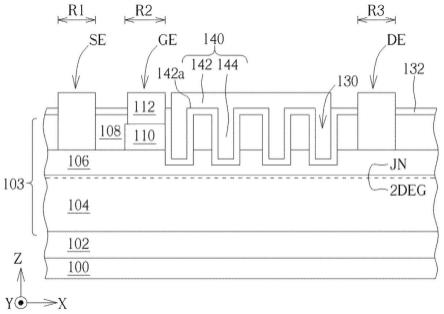

5.根据本发明的一实施例提供的一种高电子迁移率晶体管,包括一基底、一通道层设置在该基底上、一势垒层设置在该通道层上、一第一钝化层设置在该势垒层上、多个沟槽延伸穿过至少部分该第一钝化层,以及一导电板结构设置该第一钝化层上,其中该导电板结构包括一基部位于该多个沟槽上,以及多个凸出部自该基部的一下表面延伸至该多个沟槽中。

6.根据本发明的另一实施例提供的一种高电子迁移率晶体管的制作方法,包括以下步骤。首先提供一基底,接着依序于该基底上形成一通道层、一势垒层,以及一第一钝化层。然后,在该第一钝化层中形成多个沟槽,再形成一第二钝化层于该第一钝化层上并覆盖该多个沟槽的侧壁和底面。后续,形成一导电板结构于该第二钝化层上并填入该多个沟槽。

附图说明

7.图1、图2、图3、图4为本发明一实施例的高电子迁移率晶体管((highelectron mobility transistor,hemt)的制作方法的步骤剖面示意图;

8.图5为本发明一实施例的高电子迁移率晶体管的部分区域平面示意图;

9.图6为本发明一实施例的高电子迁移率晶体管的部分区域平面示意图;

10.图7为本发明一实施例的高电子迁移率晶体管的部分区域平面示意图;

11.图8为本发明一实施例的高电子迁移率晶体管的部分区域平面示意图;

12.图9为本发明一实施例的高电子迁移率晶体管的部分区域平面示意图;

13.图10a为本发明一实施例的高电子迁移率晶体管的剖面示意图;

14.图10b为本发明一实施例的高电子迁移率晶体管的剖面示意图;

15.图10c为本发明一实施例的高电子迁移率晶体管的剖面示意图;

16.图10d为本发明一实施例的高电子迁移率晶体管的剖面示意图;

17.图11为本发明一实施例的高电子迁移率晶体管的剖面示意图;

18.图12为本发明一实施例的高电子迁移率晶体管的剖面示意图;

19.图13为本发明一实施例的高电子迁移率晶体管的剖面示意图;

20.图14为本发明一实施例的高电子迁移率晶体管的剖面示意图;

21.图15为本发明一实施例的高电子迁移率晶体管的剖面示意图。

22.主要元件符号说明

23.100

ꢀꢀꢀꢀꢀꢀ

基底

24.102

ꢀꢀꢀꢀꢀꢀ

缓冲层

25.103

ꢀꢀꢀꢀꢀꢀ

叠层结构

26.104

ꢀꢀꢀꢀꢀꢀ

通道层

27.106

ꢀꢀꢀꢀꢀꢀ

势垒层

28.108

ꢀꢀꢀꢀꢀꢀ

第一钝化层

29.110

ꢀꢀꢀꢀꢀꢀ

半导体栅极层

30.112

ꢀꢀꢀꢀꢀꢀꢀ

金属栅极层

31.130

ꢀꢀꢀꢀꢀꢀꢀ

沟槽

32.132

ꢀꢀꢀꢀꢀꢀꢀ

第二钝化层

33.140

ꢀꢀꢀꢀꢀꢀꢀ

导电板结构

34.142

ꢀꢀꢀꢀꢀꢀꢀ

基部

35.142a

ꢀꢀꢀꢀꢀꢀ

下表面

36.144

ꢀꢀꢀꢀꢀꢀꢀ

凸出部

37.150

ꢀꢀꢀꢀꢀꢀꢀ

层间介电层

38.152

ꢀꢀꢀꢀꢀꢀꢀ

互连结构

39.154

ꢀꢀꢀꢀꢀꢀꢀ

互连结构

40.156

ꢀꢀꢀꢀꢀꢀꢀ

互连结构

41.158

ꢀꢀꢀꢀꢀꢀꢀ

互连结构

42.160

ꢀꢀꢀꢀꢀꢀꢀ

电阻

43.170

ꢀꢀꢀꢀꢀꢀꢀ

气隙

44.2deg

ꢀꢀꢀꢀꢀꢀ

二维电子气层

45.de

ꢀꢀꢀꢀꢀꢀꢀꢀ

漏极结构

46.ge

ꢀꢀꢀꢀꢀꢀꢀꢀ

栅极结构

47.se

ꢀꢀꢀꢀꢀꢀꢀꢀ

源极结构

48.jn

ꢀꢀꢀꢀꢀꢀꢀꢀ

接面

49.r1

ꢀꢀꢀꢀꢀꢀꢀꢀ

源极区

50.r2

ꢀꢀꢀꢀꢀꢀꢀꢀ

栅极区

51.r3

ꢀꢀꢀꢀꢀꢀꢀꢀ

漏极区

52.x

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

方向

53.y

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

方向

54.z

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

方向

具体实施方式

55.为使熟悉本发明所属技术领域的一般技术者能更进一步了解本发明,下文特列举本发明的优选实施例,并配合所附的附图,详细说明本发明的构成内容及所欲达成的功效。需知悉的是,以下所举实施例可以在不脱离本揭露的精神下,将数个不同实施例中的特征进行替换、重组、混合以完成其他实施例。

56.为了使读者能容易了解及附图的简洁,本揭露中的多张附图只绘出显示装置的一部分,且附图中的特定元件并非依照实际比例绘图。此外,图中各元件的数量及尺寸仅作为示意,并非用来限制本揭露的范围。附图中,相同或相似的元件可以用相同的标号表示。文中所描述对于图形中相对元件的上下关系,在本领域的人都应能理解其是指物件的相对位置而言,因此都可以翻转而呈现相同的构件,此都应同属本说明书所揭露的范围。

57.在本说明书中,当元件或膜层被称为「在另一元件或膜层上」或「连接到另一元件或膜层」时,它可以直接在另一个元件或膜层上,或直接连接到另一个元件或膜层,或者两者之间可存在有其他元件或膜层。相对的,当元件被称为「直接在另一个元件或膜层上」,或「直接连接到另一个元件或膜层」时,两者之间不存在有插入的元件或膜层。

58.在本说明书中,「晶片」、「基底」或「基板」意指任何包含一暴露面,可依据本发明实施例所示在其上沉积材料,制作集成电路结构的结构物。需了解的是「基底」包含半导体晶片,但并不限于此。「基底」在制作工艺中也意指包含制作于其上的材料层的半导体结构物。

59.在本说明书中,两元件描述为「电连接」或「电耦合」时,并不限于两者为等电位。在一些情况下,两元件之间可连接有其他的电路元件。

60.本发明的高电子迁移率晶体管可以是耗尽型(depletion mode)/常开型(normally-on)或增强型(enhancement mode)/常闭型(normally-off)的高电子迁移率晶体管,可应用在功率转换器、低噪声放大器、射频(rf)或毫米波(mmw)等技术领域中。

61.本发明实施例描述的高电子迁移率晶体管的栅极结构、源极结构和漏极结构的种类及形状仅为举例,以便于绘图及说明为目的,并不用于限制本发明。下文以包括金属-半导体栅极结构(metal-semiconductor gate structure)的高电子迁移率晶体管为例进行说明,应理解在其他实施例中,高电子迁移率晶体管可包括金属栅极结构(metal gate structure)。

62.图1、图2、图3、图4所绘示为根据本发明一实施例的高电子迁移率晶体管((high electron mobility transistor,hemt)的制作方法的步骤沿着xz平面的剖面示意图。

63.首先请参考图1。本发明的高电子迁移率晶体管的制作方法步骤包括提供一基底100,接着于基底100上形成一叠层结构103,其至少包括一通道层104、位于通道层104上的一势垒层106,以及位于势垒层106上的一第一钝化层108。叠层结构103包括一源极区r1、一漏极区r3,以及位于源极区r1和漏极区r3之间的一栅极区r2。

64.如本实施例所示,若高电子迁移率晶体管设计为具有金属-半导体栅极结构

(metal-semiconductor gate structure),可在栅极区r2的势垒层106上形成一半导体栅极层110,然后再形成第一钝化层108于势垒层106上并覆盖半导体栅极层110。此外,为了减少叠层结构103内发生晶格插排(lattice dislocation)或错位缺陷(lattice mismatch)的情况,可在基底100与叠层结构103之间设置一缓冲层102作为过渡区或提供应力缓冲。在一些实施例中,缓冲层102还可对叠层结构103的通道层104提供应力调变,进而改变通道层104的能带结构。

65.基底100可包括硅基底、碳化硅(sic)基底、蓝宝石(sapphire)基底、氮化镓基底、氮化铝基底或其他适合的材料所形成的基底。

66.缓冲层102、通道层104及势垒层106的材料分别可包括三五族(iii-v)半导体化合物,例如分别可包括氮化镓(gan)、氮化铝镓(algan)、渐变氮化铝镓(graded algan)、氮化铝铟(alinn)、氮化铟镓(ingan)、氮化铝镓铟(algainn)、含掺杂氮化镓(doped gan)、氮化铝(aln),或上述的组合,但不限于此。根据本发明一实施例,缓冲层102的材料可包括氮化铝(aln),通道层104的材料可包括氮化镓(gan),势垒层106的材料可包括氮化铝镓(algan)。

67.根据本发明一实施例,通过选用合适的通道层104和势垒层106材料,使两者的接面jn附近的通道层104能带弯曲而形成一位能阱(potential well),加上两者的自发极化(spontaneous polarization)与压电极化(piezoelectric polarization)特性,因而产生高浓度的电子汇聚于位能阱中,而于通道层104表面形成二维电子气层2deg,作为高电子迁移率晶体管导通(on-state)时的一平面电流通道。

68.根据本发明一实施例,缓冲层102、通道层104及势垒层106可以分别具有单层结构,或者具有由多层半导体薄层构成的超晶格(superlattice)结构。通过各半导体薄层的材料选择及厚度调整,可调变能带结构、极化场强度及/或载流子分布,进而调整二维电子气层2deg的电子分布及迁移率,以获得期望的效能。

69.半导体栅极层110用于控制栅极区r2的二维电子气层2deg的导通或截止。根据本发明一实施例,半导体栅极层110的材料可包含iii-v族半导体化合物,并且可根据高电子迁移率晶体管的应用类型选择半导体栅极层110具有n导电型(negative conductive type)或p导电型(positive conductive type),可于未施加栅极偏压时,利用其内建电压(built-in voltage)来拉升位能阱的能带,而空乏(deplete)了栅极区r2的二维电子气层2deg,以实现常闭(normally-off)操作。根据本发明一实施例,半导体栅极层110的材料可包含镁(mg)、铁(fe)或其他合适掺杂的p型氮化镓(p-gan),但不限于此。

70.第一钝化层108作为叠层结构103的绝缘层和保护层,避免其下方材料层于后续制作工艺中受到损害。第一钝化层108的材料可包括绝缘材料,例如氮化铝(aln)、氧化铝(al2o3)、氮化硼(bn)、氮化硅(si3n4)、氧化硅(sio2)、氧化锆(zro2)、氧化铪(hfo2)、氧化镧(la2o3)、氧化镏(lu2o3)、氧化镧镏(laluo3)、高介电常数(high-k)介电材料或其他适合的绝缘材料。

71.根据本发明一实施例,可利用异质外延成长(heteroepitaxy growth)技术在基底100上依序形成缓冲层102、通道层104、势垒层106及半导体栅极层110,然后进行图案化制作工艺以移除栅极区r2之外多余的半导体栅极层110,接着再沉积第一钝化层108覆盖势垒层106及半导体栅极层110,获得如图1所示结构。适用的异质外延成长技术例如分子束外延

(molecule beam epitaxy,mbe)、金属有机化学气相沉积(metal-organic chemical vapor deposition,mocvd)、氢化物气相沉积(hydride vapor phase deposition,hvpe),但不限于此。第一钝化层108可利用例如原子层沉积(ald)、等离子体加辅助原子层沉积(peald)、化学气相沉积(cvd)、等离子体辅助化学气相沉积(pecvd)、低压化学气相沉积(lpcvd)等技术形成,但不限于此。

72.请参考图2。接着,进行一图案化制作工艺,在叠层结构103的栅极区r2和漏极区r3之间形成多个沟槽130。沟槽130的深度可根据设计需求设计。图2所示实施例中,沟槽130可贯穿第一钝化层108并延伸至势垒层106的一上部中。形成沟槽130的步骤例如可包括先于第一钝化层108上形成一光致抗蚀剂层,然后于光致抗蚀剂层中形成光致抗蚀剂开口,显露出沟槽130的预定区域的第一钝化层108,接着再以光致抗蚀剂层作为掩模进行蚀刻制作工艺,例如是感应耦合等离子体-反应性离子蚀刻(icp-rie)制作工艺,自光致抗蚀剂开口蚀刻移除显露出来的第一钝化层108及势垒层106,因而在第一钝化层108及势垒层106上部形成多个沟槽130,然后移除剩余的光致抗蚀剂层。

73.沟槽130与半导体栅极层110之间的距离可根据设计需求调整,可大致上等于零或大于零。举例来说,在图2所示实施例中,沟槽130与半导体栅极层110之间的距离大致上为零,使导体栅极层110的侧壁与邻近的沟槽130的侧壁可在垂直方向上互相切齐,或者使导体栅极层110的侧壁自沟槽130的侧壁显露出来。在其他实施例中,当沟槽130与半导体栅极层110之间的距离大于零时,两者之间可被第一钝化层108区隔开。

74.请参考图3。接着,形成一第二钝化层132于第一钝化层108上并沿着各个沟槽130的侧壁和底面覆盖。第二钝化层132的材料可包括氮化铝(aln)、氧化铝(al2o3)、氮化硼(bn)、氮化硅(si3n4)、氧化硅(sio2)、氧化锆(zro2)、氧化铪(hfo2)、氧化镧(la2o3)、氧化镏(lu2o3)、氧化镧镏(laluo3)、高介电常数(high-k)介电材料或其他适合的介电材料。根据本发明一实施例,第二钝化层132与第一钝化层108可包括相同材料,例如氮化硅(si3n4)。第一钝化层108和第二钝化层132可一起被称为高电子迁移率晶体管的钝化层。

75.请参考图4。接着,形成一导电板结构140于第二钝化层132上,其包括高于沟槽130开口的基部142,以及自基部142的下表面142a往下(往通道层104的方向)延伸并且填满各个沟槽130的多个凸出部144。导电板结构140可包括金属材料,例如金(au)、钨(w)、钴(co)、镍(ni)、钛(ti)、钼(mo)、铜(cu)、铝(al)、钽(ta)、钯(pd)、铂(pt)、上述金属的化合物、复合层或合金,但不限于此。

76.导电板结构140的凸出部144的尺寸大致上由沟槽130的尺寸及第二钝化层132的沉积厚度决定。在图4所示实施例中,凸出部144的底部可低于势垒层106的上表面,且高于势垒层106的下表面。换言之,凸出部144的底部可介于势垒层106的上表面和下表面之间。导电板结构140及势垒层106由第二钝化层132区隔开,不直接接触。

77.可利用任何合适的制作工艺来制作导电板结构140。举例来说,可利用掀离制作工艺(lift-off process)来制作导电板结构140,步骤包括先于第二钝化层132上形成一光致抗蚀剂层,然后图案化该光致抗蚀剂层以形成显露出该些沟槽130的一光致抗蚀剂开口,接着以电子束蒸镀(electron beam evaporation)或溅镀(sputtering)的方式全面性地于光致抗蚀剂层上沉积一金属层并使金属层填满各个沟槽130,接着再进行一溶剂处理以掀离(lift-off)光致抗蚀剂层并同时移除掉金属层位于光致抗蚀剂层上的部分,达到图案化金

属层的目的。剩余的金属层则成为导电板结构140。在其他实施例中,也可利用光刻暨蚀刻制作工艺来制作接导电板结构140,步骤包括利用电子束蒸镀或溅镀的方式全面性地于叠层结构103上沉积一金属层并使金属层填满各个沟槽130后,接着于金属层上形成一图案化光致抗蚀剂层以定义出导电板结构140的图案,然后以光致抗蚀剂层为掩模进行一蚀刻制作工艺(例如干蚀刻制作工艺或湿蚀刻制作工艺)以移除多余的金属层,而将光致抗蚀剂层的图案转移至金属层中,获得导电板结构140。以上导电板结构140的制作方法仅为举例,实际操作可根据设计需求调整。

78.请继续参考图4。可于制作导电板结构140的步骤之前、之后或同时,在叠层结构103的源极区r1、漏极区r3及栅极区r2的钝化层内分别形成源极结构se、漏极结构de和栅极结构ge。制作方法可包括先于源极区r1、漏极区r3及栅极区r2上的钝化层(视制作工艺顺序,可为第一钝化层108或第一钝化层108和第二钝化层132,或更多层的钝化层)中定义出开口,再进行任何合适的制作工艺来制作源极结构se、漏极结构de和栅极结构ge,例如前述的掀离制作工艺或光刻暨蚀刻制作工艺,为了简化说明在此不再详述。

79.根据本发明一实施例,如图4所示,源极结构se和漏极结构de位于栅极结构ge两侧,贯穿第一钝化层108和第二钝化层132而与势垒层106接触。在其他实施例中,源极结构se和漏极结构de的底部可再往下延伸穿过部分势垒层106并停止在势垒层106中,或者再往下延伸贯穿势垒层106及部分通道层104而停止在通道层104中。源极结构se和漏极结构de材料可包括金属,与势垒层106之间形成金属-半导体接面,较佳为欧姆接触(ohmic contact),无论在顺偏压或逆偏压时都可导通。源极结构se和漏极结构de的材料可包括金(au)、钨(w)、钴(co)、镍(ni)、钛(ti)、钼(mo)、铜(cu)、铝(al)、钽(ta)、钯(pd)、铂(pt)、上述材料的化合物、复合层或合金,但不限于此。根据本发明一实施例,导电板结构140、源极结构se以及漏极结构de可包括相同的金属材料。根据本发明另一实施例,导电板结构140、源极结构se以及漏极结构de可包括不同的金属材料。

80.根据本发明一实施例,栅极结构ge是由半导体栅极层110以及位于半导体栅极层110上方的一金属栅极层112构成,两者之间形成金属-半导体接面,较佳为萧基接触(schottky contact),可具有整流功能。金属栅极层112可包括金属材料,例如金(au)、钨(w)、钴(co)、镍(ni)、钛(ti)、钼(mo)、铜(cu)、铝(al)、钽(ta)、钯(pd)、铂(pt)、上述材料的化合物、复合层或合金,但不限于此。根据本发明一实施例,金属栅极层112与源极结构se以及漏极结构de可包括相同的金属材料。根据本发明另一实施例,金属栅极层112与源极结构se以及漏极结构de可包括不同的金属材料。

81.本发明特征在于,位于栅极结构ge与漏极结构de之间的导电板结构141,利用其基部142以及多个凸出部144,可对叠层结构103产生的应力来调变叠层结构103内的压电极化效应,及/或通过提供额外的电场来调变叠层结构103内的电场强度,整体而言,可降低栅极结构ge边缘的峰值电场,达到提升高电子迁移率晶体管的击穿电压及改善元件线性度的效果,有利于高压元件的应用。导电板结构140也可被作为场板(field plate)结构使用。

82.下文将针对本发明的不同实施例进行说明。为简化说明,以下说明主要描述各实施例不同之处,而不再对相同之处作重复赘述。各实施例中相同的元件是以相同的标号进行标示,以利于各实施例间互相对照。

83.图5、图6、图7、图8、图9所绘示为根据本发明一些实施例的高电子迁移率晶体管的

部分区域沿着xy平面的平面示意图,说明沟槽130与导电板结构140的凸出部144的一些布局变化。应理解,图5、图6、图7、图8、图9示出的凸出部144上方会被基部142覆盖并连接成一体成型的结构。为了简化附图,基部142并未绘示出来。

84.在图5所示实施例中,凸出部144与沟槽130具有沿着相同方向(例如沿着y方向)延伸,具有长条形状,且各凸出部144分别对应设置在一个沟槽130内,换言之,各凸出部144与一沟槽130在垂直方向(例如z方向)上互相重叠。

85.在图6所示实施例中,沟槽130沿着y方向延伸,具有长条形状,而凸出部144具有大致上为方形(或圆形)的形状,且区被区分为多组,各组分别对应设置在一个沟槽130内。

86.在图7所示实施例中,沟槽130和凸出部144均具有大致上为方形(或圆形)的形状,各凸出部144分别对应设置在一个沟槽130内,并且沿着x方向和y方向对齐排列。

87.在图8所示实施例中,沟槽130和凸出部144均具有大致上为方形(或圆形)的形状,各凸出部144分别对应设置在一个沟槽130内,并且沿着y方向对齐排列,沿着x方向交错排列。

88.在图9所示实施例中,沟槽130和凸出部144均具有大致上为方形(或圆形)的形状,且根据与栅极结构之间的距离而有渐变的尺寸,例如图9左侧较靠近栅极结构的沟槽130和凸出部144的尺寸可大于图9右侧较远离栅极结构的沟槽130和凸出部144的尺寸。

89.可利用图2的沟槽130的图案化制作工艺搭配图4的导电板结构140的图案化制作工艺,获得上述的沟槽130与导电板结构140的凸出部144的各种布局。举例来说,图5的布局的制作步骤包括于第一钝化层108中形成沟槽130后,接着沉积第二钝化层132沿着沟槽的底面和侧壁覆盖,然后沉积金属层填满各沟槽130。图6的布局的制作步骤例如于第一钝化层108中形成沟槽130后,接着沉积第二钝化层132填满沟槽130,然后进行另一次图案化制作工艺以在沟槽130内的第二钝化层132中定义出对应各凸出部144的沟槽(图未示),接着再沉积金属层填满第二钝化层132中的沟槽。

90.图10a、图10b、图10c所绘示为根据本发明一些实施例的高电子迁移率晶体管的沿着xz平面的剖面示意图,说明沟槽130与导电板结构140的凸出部144的延伸深度变化。

91.在一些实施例中,如图10a所示,沟槽130可贯穿第一钝化层108且未延伸至第一钝化层108中,沟槽130的底部与势垒层106的上表面大致上切齐。导电板结构140的凸出部144底部会高于势垒层106的上表面,与势垒层106之间由第二钝化层132区隔开。

92.在一些实施例中,如图10b所示,沟槽130可贯穿第一钝化层108及势垒层106并延伸至通道层104的一上部中而被二维电子气层2deg包围环绕。导电板结构140的凸出部144底部会低于势垒层106的下表面,与通道层104通过第二钝化层132区隔开,不直接接触。

93.在一些实施例中,沟槽130可具有不同深度,换言之,导电板结构140的凸出部144在垂直方向(例如z方向)上可具有不同长度。举例来说,如图10c所示,较邻近栅极结构ge的沟槽130可具有较大的深度,较远离栅极结构ge的沟槽130可具有较小的深度。在一些实施例中,一部分的沟槽130可穿过第一钝化层108及势垒层106,且底部可延伸至通道层104的一上部中而被二维电子气层2deg包围环绕,另一部分的沟槽130则贯穿第一钝化层10但不贯穿势垒层106,底部位于二维电子气层2deg的上方。在一些实施例中,也可选择使具有不同深度的沟槽130均未贯穿势垒层106,底部位均于二维电子气层2deg的上方。需特别说明的是,图10c实施例中,沟槽130的深度根据与栅极结构ge的距离而渐变仅为示例,本发明不

以此为限。沟槽130深度的设计可依据元件效能来调整。

94.在一些实施例中,如图10d所示,沟槽130可仅穿过部分第一钝化层108而未显露出势垒层106,即沟槽130的底部均位于势垒层106的上表面上方。导电板结构140的凸出部144底部会高于势垒层106的上表面,与势垒层106之间由第一钝化层108及第二钝化层132区隔开。在一些实施例中,当沟槽130侧壁及底部完全被第一钝化层108包围时,也可选择省略第二钝化层132。

95.图11、图12、图13、图14所绘示为根据本发明一些实施例的高电子迁移率晶体管的剖面示意图,说明导电板结构140、栅极结构ge、源极结构se和漏极结构de通过设置在叠层结构103上的互连结构而实现的一些电连接样态。需特别说明的是,图11、图12、图13、图14绘示的导电板结构140的态样仅为举例,可根据需求选择如前文图4、图5、图6、图7、图8、图9、图10a、图10b、图10c、图10d的实施例或其他符合本发明所请的导电板结构的态样。

96.在图11所示实施例中,栅极结构ge、源极结构se和漏极结构de分别与互连结构154、互连结构152和互连结构156电连接,以对栅极结构ge、源极结构se和漏极结构de提供合适的驱动电压。导电板结构140并未与任何互连结构电连接,实质上为电性浮置(electrically folating)。

97.在图12所示实施例中,导电板结构140上可设有互连结构158,并且通过互连结构158及互连结构154而与栅极结构ge电连接,共同连接至一栅极电压源。可选择性设置一电阻160或其他电路元件电连接在互连结构158及互连结构154之间。

98.在图13所示实施例中,导电板结构140通过互连结构158及互连结构156而与漏极结构de电连接,共同连接至一漏极电压源。可选择性将电阻160或其他电路元件电连接在互连结构158及互连结构156之间。

99.在图14所示实施例中,导电板结构140通过互连结构158及互连结构152而与源极结构se电连接,共同连接至一源极电压源。可选择性将电阻160或其他电路元件设置在互连结构158及互连结构152之间。

100.应理解,在一些实施例中,也可选择使导电板结构140的互连结构158未与栅极结构ge、源极结构se或漏极结构de电连接,而是另连接至一场板电压源。

101.根据本发明一实施例,互连结构152、154、156、158分别是由导电材料构成,可包括金属,例如金(au)、钨(w)、钴(co)、镍(ni)、钛(ti)、钼(mo)、铜(cu)、铝(al)、钽(ta)、钯(pd)、铂(pt)、上述金属的化合物、复合层或合金,但不限于此。互连结构152、154、156、158可设置在叠层结构103上的一层间介电层150中。层间介电层150材料可包括氧化硅(sio2)或低介电常数(low-k)介电材料。低介电常数(low-k)介电材料例如是氟硅玻璃(fluorinated silica glass,fsg)、碳硅氧化物(sicoh)、旋涂硅玻璃(spin-on glass)、多孔性低介电常数介电材料(porous low-k dielectric material)或有机高分子介电材料,但不限于此。根据本发明一实施例,电阻160可以是由高阻值金属、金属氧化物或低温多晶硅构成,但不限于此。在一些实施例中,也可通过调整互连结构走线的尺寸及长度来获得较高的阻值而可提供电阻的功效。

102.可根据需求选择上述的各种电连接样态以进一步调整电场强度,并提高元件电流增益。通过选择在驱动回路中加入电阻,可改善元件的高频震荡(high-frequency oscillation)稳定度。

103.图15所绘示为根据本发明一实施例的高电子迁移率晶体管的剖面示意图,说明可在层间介电层150的适当位置中,例如位于互连结构之间的层间介电层150中形成至少一气隙(air gap)170,以降低互连结构之间的寄生电容,也可获得改善元件的高频震荡稳定度的效果。制作气隙170的方法例如在层间介电层150中蚀刻出沟槽,然后于层间介电层150上沉积另一层间介电层以将气隙170密封在沟槽中。

104.综合以上,本发明通过在高电子迁移率晶体管的栅极结构和漏极结构之间设置包括一基部及自基部下表面往通道层方向延伸的多个凸出部的一导电板结构,并可根据需求选择导电板结构与栅极结构、源极结构和漏极结构的电连接样态,可调变高电子迁移率晶体管内的电场强度,特别是可降低栅极结构边缘的峰值电场,可获得降低的漏电流及提高的击穿电压,从而增加了高电子迁移率晶体管的稳定性。

105.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1